## **ATLAS NSW Electronics Specifications**

Component: VMM3a

VMM is the front end ASIC to be used in the front end electronics readout system of

both the Micromegas and sTGC detectors of the New Small Wheels Upgrade project.

#### Version: v1.0

#### Abstract

<sup>8</sup> The VMM is a custom Application Specific Integrated Circuit (ASIC). It is intended to be <sup>9</sup> used in the front end readout electronics of both the Micromegas and sTGC detectors of the <sup>10</sup> New Small Wheels Phase I upgrade project. It is being developed at Brookhaven National <sup>11</sup> Laboratory by Gianluigi de Geronimo and his microelectronics design group. It is fabricated in <sup>12</sup> the 130 nm Global Foundries 8RF-DM process (former IBM 8RF-DM). The 64 channels with <sup>13</sup> highly configurable parameters will meet the processing needs of signals from all sources of both <sup>14</sup> detector types:

• Negative anode strip signals from the Micromegas detectors.

• Negative wire-group signals from the sTGC detectors.

1

2

3

6

7

• Positive cathode strip signals from the sTGC for precision spatial reconstruction.

• Positive cathode pad signals used in the sTGC trigger.

<sup>19</sup> To accomplish this the VMM has four independent data output paths:

- Precision (10-bit) amplitude and (effective) 20-bit time stamp read out at Level 0 accept.

- A serial out Address in Real Time (ART) synchronized to a 160 MHz clock which is used for the Micromegas Trigger.

- Parallel prompt outputs from all 64 channels in a variety of selectable formats (including a 6-bit ADC) for the sTGC trigger.

- Multiplexed analog amplitude and timing outputs will not be used in the NSW but can

be valuable in development and debugging.

<sup>27</sup> Version 3a, to be submitted on September 2017 in a dedicated run, has all the design contains <sup>28</sup> all the features that are needed for the ATLAS NSW upgrade and in addition contains bug fixes <sup>29</sup> form the Version 3 that are described in this document. The device will be packaged in a Ball <sup>30</sup> Grid Array with outline dimensions of  $21 \times 21 \text{ mm}^2$ .

| Revision History |                     |                                                             |                                                                     |  |  |  |  |  |

|------------------|---------------------|-------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| Rev. No.         | Proposed Date       | Description of Changes                                      | Proposed by: author                                                 |  |  |  |  |  |

|                  | Approved Date       | (Include section numbers or<br>page numbers if appropriate) | Approved by: author                                                 |  |  |  |  |  |

| v1.0             | P: 20/08/2017<br>A: | Initial Draft                                               | <b>P:</b> Polychronakos V., Iako-<br>vidis G., De Geronimo G.<br>A: |  |  |  |  |  |

31

32

| 33 | $\mathbf{C}$ | ontents                                                                             |            |

|----|--------------|-------------------------------------------------------------------------------------|------------|

| 34 | 1            | Conventions and Glossary                                                            | 5          |

| 35 | <b>2</b>     | Related Documents                                                                   | 5          |

| 36 |              | 2.1 ASICs other than VMM and related items                                          | 5          |

| 37 |              | 2.2 VMM Progress reports                                                            | 6          |

| 51 |              |                                                                                     | 0          |

| 38 | 3            | Description of the VMM                                                              | 7          |

| 39 |              | 3.1 Issues addressed from the previous prototype, corner cases simulation and unre- |            |

| 40 |              | solved issues                                                                       | 8          |

| 41 | 4            | Signal Processing requirements                                                      | 8          |

| 42 |              | 4.1 MicroMegas Detectors                                                            | 8          |

| 43 |              | 4.1.1 Dynamic Range and Noise Requirements                                          | 9          |

| 44 |              | 4.2 sTGC Detectors                                                                  | 10         |

| 45 |              | 4.3 Wire Signals                                                                    | 10         |

| 46 |              | 4.4 Pad Signals                                                                     | 10         |

| 47 |              | 4.5 Strip Signals                                                                   | 11         |

| 48 |              | 4.6 Input Capacitance and Rate per VMM                                              | 11         |

| 49 |              | 4.7 Input DC Current VMM channel                                                    | 12         |

| 50 |              | 4.8 Dynamic Range and Noise Requirements                                            | 12         |

|    | -            |                                                                                     | 10         |

| 51 | 5            | v i v                                                                               | 12         |

| 52 |              | 5.1 Layout recommendations and requirements                                         | 14         |

| 53 | 6            | Manufacturer                                                                        | 14         |

| 54 |              | 6.1 Wafer Processing                                                                | 14         |

| 55 |              | 6.2 Packaging                                                                       | 14         |

| 56 |              | 6.3 Export License Issues                                                           | 14         |

| 57 | 7            | Power                                                                               | 14         |

|    | -            |                                                                                     |            |

| 58 | 8            | Cooling                                                                             | 16         |

| 59 | 9            | Input and Output                                                                    | 17         |

| 60 | 10           | Detailed Functional Description and Specifications                                  | 17         |

| 61 |              | 10.1 Configuration Process                                                          | 17         |

| 62 |              | 10.2 Two-Phase Analog Mode                                                          | $21^{-1}$  |

| 63 |              | 10.3 Continuous (digital) Mode                                                      | 22         |

| 64 |              | 10.3.1 Non-ATLAS Continuous Mode                                                    | 23         |

|    | 11           | NSW anasifa Dandaut                                                                 | <u>م</u> ۹ |

| 65 | 11           | I                                                                                   | 24         |

| 66 |              | 11.1 Summary of requirements and external constraints                               | 24         |

| 67 |              | 11.2 VMM                                                                            | 26         |

| 68 |              | 11.2.1 Level-0 data selector                                                        | 27         |

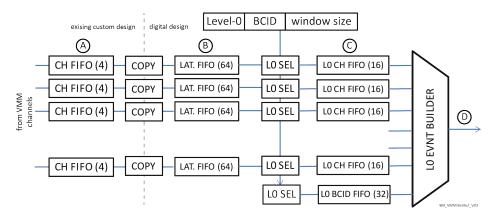

| 69 | 11.2.2 Level-0 event building $\ldots$                                                   | 28        |

|----|------------------------------------------------------------------------------------------|-----------|

| 70 | 11.2.3 Transfer from VMM to Readout Controller                                           | 29        |

| 71 | 11.2.4 VMM clock domains                                                                 | 30        |

| 72 | 11.3 Trigger Paths                                                                       | 30        |

| 73 | 11.3.1 Micromegas Trigger Primitive                                                      | 31        |

| 74 | 11.3.2 sTGC Trigger Primitives                                                           | 32        |

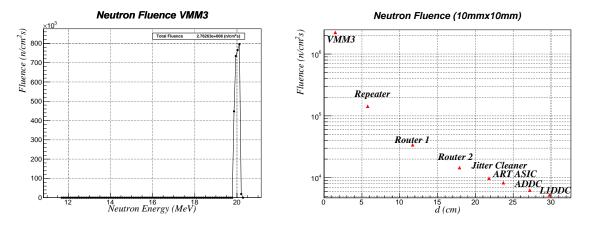

| 75 | 12 VMM3 testing                                                                          | 33        |

| 76 | 12.1 Integration with the NSW Electronics                                                | 33        |

| 77 | 12.2 VMM3 calibration                                                                    | 34        |

| 78 | 13 Radiation Tolerance and SEU                                                           | <b>34</b> |

| 79 | 13.1 VMM1 SEU testing                                                                    | 35        |

| 80 | 13.2 VMM3 SEU testing                                                                    | 35        |

| 81 | 14 Testing, Validation and Commissioning                                                 | 35        |

| 82 | 15 Reliability Matters                                                                   | 36        |

| 83 | 15.1 Consequences of Failures                                                            | 36        |

| 84 | 15.2 Prior Knowledge of Expected Reliability                                             | 36        |

| 85 | 15.3 Measures Proposed to Insure Reliability of Component and/or System $\ldots$         | 36        |

| 86 | 15.4 Quality Control to Validate Reliability Specifications during Production $\ldots$ . | 36        |

| 87 | Appendices                                                                               | 37        |

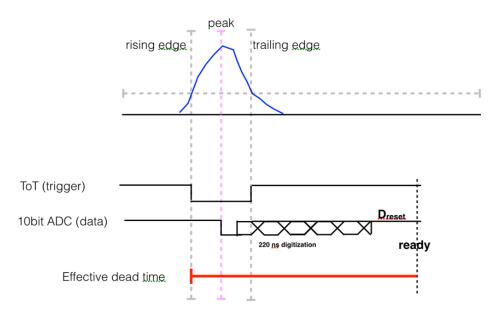

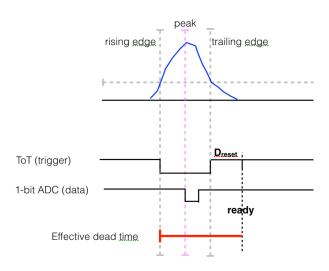

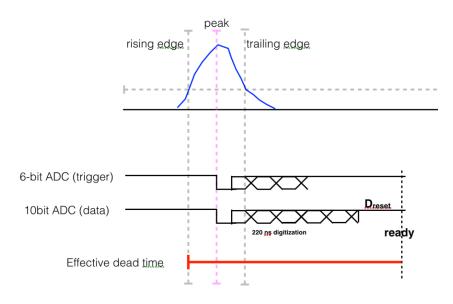

| 88 | A Deadtime in Several modes of operation                                                 | 37        |

| 89 | A.1 sTGC modes of operation                                                              | 37        |

| 90 | A.2 Micromegas trigger dead time                                                         | 39        |

## 91 1 Conventions and Glossary

| 92       | <b>ADC</b> Analog to Digital Converter.              | 110<br>111          | <b>MOSFET</b> Metal Oxide Semiconductor Field<br>Effect Transistor. |

|----------|------------------------------------------------------|---------------------|---------------------------------------------------------------------|

| 93       | <b>ART</b> Address in Real Time.                     | 112                 | <b>MSB</b> Most Significant Bit.                                    |

| 94       | <b>ASIC</b> Application-Specific Integrated Circu    |                     | NOST SIGNICANT DIT.                                                 |

| 95       | BGA Ball Grid Array.                                 | 113                 | <b>NSW</b> New Small Wheel.                                         |

| 96       | <b>CA</b> Charge Amplifier.                          | 114                 | <b>PDO</b> Peak Detector Output.                                    |

|          |                                                      | 115                 | <b>PtP</b> Pulse at Peak.                                           |

| 97<br>98 | <b>CMOS</b> Complementary Metal Oxide Ser conductor. | 111 <b>-</b><br>116 | <b>PtT</b> Peak to Threshold.                                       |

| 99       | <b>DAC</b> Digital to Analog Converter.              | 117                 | <b>ROC</b> Read Out Controller.                                     |

| 100      | <b>DDF</b> Delayed Dissipative Feedback.             | 118                 | <b>SEU</b> Single Event Upset.                                      |

| 101      | <b>DDR</b> Double Data Rate.                         | 119                 | <b>SLVS</b> Scalable Low Voltage Signaling.                         |

| 102      | <b>DICE</b> Dual Interlocked Cells.                  | 120                 | <b>SPI</b> Serial Peripheral Interface.                             |

| 103      | <b>EAR</b> Export Administration Regulations.        | 121                 | ${\bf sTGC}$ small strip Thin Gap Chambers.                         |

| 104      | <b>ENC</b> Equivalent Noise Charge.                  | 122                 | <b>TAC</b> Time to Amplitude Converter.                             |

| 105      | ESD Electrostatic Discharge.                         | 123                 | <b>TDO</b> Time Detector Output.                                    |

| 106      | <b>FIFO</b> First In First Out.                      | 124                 | <b>TDS</b> Trigger Data Serializer.                                 |

|          |                                                      | 125                 | <b>TID</b> Total Ionizing Dose.                                     |

| 107      | <b>LSB</b> Least Significant Bit.                    | 126                 | ${\bf TMR}$ Triple Modular Redundancy.                              |

| 108      | Micromegas Micro Mesh Gaseous Structu                | lľ1@7               | <b>ToT</b> Time over Threshold.                                     |

| 109      | <b>MO</b> Monitoring Output.                         | 128                 | <b>TtP</b> Threshold to Peak.                                       |

## <sup>129</sup> 2 Related Documents

The VMM interfaces directly with 3 custom ASICs and indirectly with one. A brief description

of the functionality of these ASICs and the relevant printed circuit boards, the specifications

documents, as well as links to these document are provided below.

## <sup>133</sup> 2.1 ASICs other than VMM and related items

The ReadOut Controller (ROC) ASIC. It reads data out of up to 8 VMM chips and

provides all interface readout control signals:

136 https://edms.cern.ch/file/1470540/1/NSW\_VMM3\_ROCReviewFeb2015\_PDR\_20150507.pdf

- 137 https://svnweb.cern.ch/cern/wsvn/NSWELX/ReadOutController/Documentation/VMM3\_ROCs

- 138 pecMar2016/VMM3\_ROCspec.pdf

- https://indico.cern.ch/event/647424/contributions/2630995/attachments/1482889/2300520/

- 140 ROC\_Review\_June17\_-\_ePLL.pdf

- 141 2. The Slow Control Adapter (SCA). Used for configuration and monitoring of the VMM:

- 142 https://espace.cern.ch/GBT-Project/GBT-SCA/default.aspx

- **3. The Trigger Data Serializer (TDS)**. It is used to handle the prompt signals (ToT and

strips) used in the sTGC trigger:

- 145 https://indico.cern.ch/event/327350/contribution/2/attachments/635918/875421/sTGC

- 146 \_Review\_largerfigures.pdf

- 147 https://indico.cern.ch/event/647424/contributions/2630955/attachments/1482851/2300304/

- 148 TDS\_followup\_20170626.pdf

- 149 4. The Front End Card with 8 VMM (MMFE-8), is the front end card with 8 VMM chips:

- 150 (512 channels) used by the Micromegas Detectors https://edms.cern.ch/file/1470529/1/NS

- 151 W\_MMFE-8-Specification-020515\_PDR.pdf

- <sup>152</sup> 5. NSW sTGC FEB Design Note and Specification: the front end card that is designed

for the sTGC detectors: (512 channels) used by the Micromegas Detectors https://edms.cer n.ch/file/1470532/1/NSW\_sTGC\_FEB\_Design\_Review\_20150130\_PDR.docx

155 6. The Address in Real Time (ART) ASIC receives synchronously with the BC clock the

- <sup>156</sup> ART signals from up to 32 VMM, encodes the strip address of those VMM with a hit, appends

- the BCID and transmits the data to the MM trigger processor: https://edms.cern.ch/file/

- 158 1472976/1/NSW\_ART\_ASIC\_specs\_PDR\_2015\_2.docx

- https://indico.cern.ch/event/647424/contributions/2630940/attachments/1482366/2300256/ art\_review\_june17.pdf

7. The ART Data Driver Card (ADDC) is the PCB housing the ART ASIC and GBT

chipset: https://edms.cern.ch/file/1470535/1/NSW\_ADDC\_document\_v1.0\_PDR\_2\_2015.pd

f

<sup>164</sup> 8. sTGC Analog Requirements for the New Small Wheel VMM3 ASIC : https://ed

165 ms.cern.ch/file/1536160/1/VMM3\_Analog\_Requirements\_sTGC\_EDMS\_SpecsDocument\_20150814. 166 docx

## <sup>167</sup> 2.2 VMM Progress reports

- <sup>168</sup> In addition there are some critical presentations that show the progress and review of the VMM3:

- $_{169}$  NSW ASIC Review on  $27^{\mathrm{th}}$  of April 2017:

- https://indico.cern.ch/event/631131/contributions/2561765/attachments/1450861/2237123/

- 171 VMM\_Update\_Apr\_2017\_fin.pdf

- $_{172}$  NSW ASIC Review on  $26^{\mathrm{th}}$  of June 2017:

- https://indico.cern.ch/event/647424/contributions/2630999/attachments/1482862/2300769/

- 174 VMM3a\_status\_Jun\_2017.pdf

## <sup>175</sup> **3** Description of the VMM

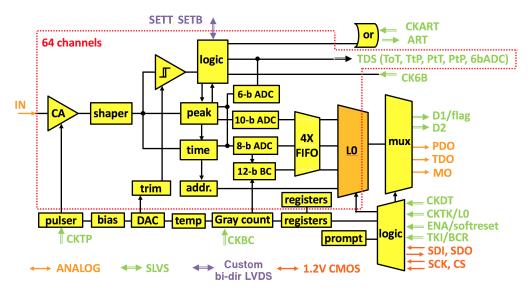

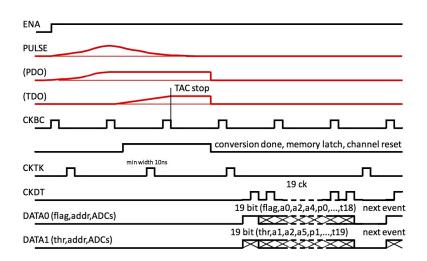

The VMM is composed of 64 linear front-end channels. A block diagram of one of the identical 176 channels is shown in Figure 1. Each channel integrates a low-noise charge amplifier (CA) with 177 adaptive feedback, test capacitor, and adjustable polarity (to process either positive or negative 178 charge). The input MOSFET is a p-channel with gate area of  $L \times W = 180 \text{ nm} \times 10 \text{ nm}$  (200 179 fingers, 50  $\mu$ m each) biased at a drain current ID = 2 mA; this corresponds to an inversion 180 coefficient IC  $\approx 0.22$ , a transconductance  $g_m \approx 50 \,\mathrm{mS}$ , and a gate capacitance  $C_q \approx 11 \,\mathrm{pF}$ . 181 The filter (shaper) is a third-order (one real pole and two complex conjugate poles) designed in 182 delayed dissipative feedback (DDF) [1], has adjustable peaking time in four values (25, 50, 100, 183 and 200 ns) and stabilized, band-gap referenced, baseline. The DDF architecture offers higher 184 analog dynamic range, making possible a relatively high resolution at input capacitance much 185 smaller than 200 pF. The gain is adjustable in eight values (0.5, 1, 3, 4.5, 6, 9, 12, 16 mV/fC). 186 Next to the shapers are the sub-hysteresis discriminators [2] with neighbor enabling logic, 187 and individual threshold trimming, the peak detector, and the time detector. The sub-hysteresis 188 function allows discrimination of pulses smaller than the hysteresis of the comparator circuit. 189 The threshold is adjusted by a global 10-bit Digital to Analog Converter (DAC) and an individual 190 channel 5-bit trimming DAC. The neighbor channel logic forces the measurements of channels 191 neighboring a triggered one, even those channels did not exceed the set threshold. The neighbor 192 logic extends also to the two neighboring chips through bidirectional IO. The peak detector 193 measures the peak amplitude and stores it in an analog memory. The time detector measures 194 the timing using a time-to-amplitude converter (TAC), i.e., a voltage ramp that starts either at 195 threshold crossing or at the time of the peak and stops at a clock cycle of the BC clock. The 196 TAC value is stored in an analog memory and the ramp duration is adjustable in four values 197 (60 ns, 100 ns, 350 ns, 650 ns). The peak and time detectors are followed by a set of three low-198 power ADCs (a 6-bit, a 10-bit, and a 8-bit), characterized by a domino architecture [3] but of a 199 new concept. These ADC are enabled depending on the selected mode of operation. 200

Figure 1: Architecture of VMM3.

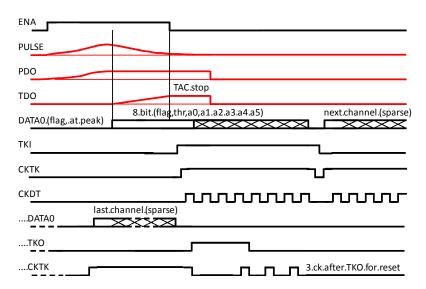

The ASIC can operate in either a two phase analog mode (not used in NSW), or in a continuous, simultaneous read/write mode. In the two phase mode data are registered while the VMM is in acquisition mode and then read out, after the system is switched to the read out mode. Acquisition is re-enabled after the readout phase is completed. In continuous mode the simultaneous read/write of data assures dead-timeless operation that can handle rates up to the maximum of 4 MHz per channel (1 MHz expected at the NSW). The ASIC has four independent output data paths:

<sup>208</sup> 1. Multiplexed analog amplitude and timing.

209 2. Digitized (10-bit amplitude, 20-bit vernier time stamp) in a 2-bit (DDR readout) digital 210 multiplexed mode in either a short four-word buffer or with a deeper buffer sufficient for 211 the expected Level-0 latency with the associated control logic.

3. Address in Real Time (ART) used in the Micromegas trigger schema.

4. Direct SLVS-400 outputs of all 64 channels in parallel in one of five selectable formats,

used in the sTGC trigger.

The ASIC includes global and acquisition resets and an adjustable pulse generator connected to the injection capacitor of each channel, adjustable with a global 10-bit DAC, and triggered by an external clock. A global threshold generator adjustable with a 10-bit DAC, a band-gap reference circuit, a temperature sensor complete the basic features of the VMM. Finally, it integrates analog monitor capability to directly measure the global DACs, the band-gap reference, the temperature sensor, the analog baseline, the analog pulse, and the channel threshold (after trimming).

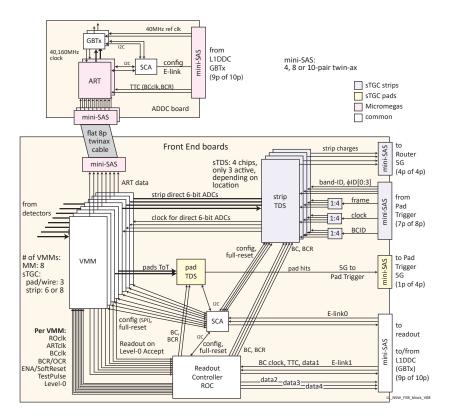

The overall connection scheme of these data paths with the rest of the NSW readout and trigger components is shown in Figure 2 and a detailed description of all modes of operation will be described in Section 11.

## 3.1 Issues addressed from the previous prototype, corner cases simulation and unresolved issues

Several issues have been identified on VMM3. All of them have been addressed on VMM3a.

Figure 3 shows the summary of them along with fixes implemented and the simulation status.

Essentially all known VMM3 issues have been addressed and simulated for all process corners.

There is no known remaining unresolved issue.

## <sup>231</sup> 4 Signal Processing requirements

Both Micromegas and sTGC chambers of the NSW Upgrade will use the VMM as their front end processing ASIC. In this section the analog requirements for the VMM of both detectors are specified.

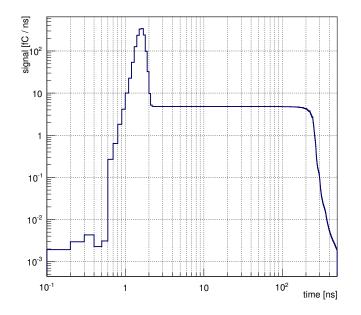

## 235 4.1 MicroMegas Detectors

The Micromegas signals from the anode strips (negative polarity signals) depending on the chosen gas gain and shaper integration time can be up to a maximum 250 fC, but typically

Figure 2: Overall connection diagram of the VMM.

half or even one fourth of the maximum. The simulated input current waveform is shown inFigure 4.

The fast electron current is followed by the positive ion current. One can notice two features. Since the ions are moving in a constant electric field the current is constant. Because of the short distance to the wire mesh ( $128 \,\mu m$ ) the total signal duration is  $\sim 200 \,\mathrm{ns}$  [4]. In addition to the current waveform and maximum input charge, the other relevant parameter is the electrode (anode strip) capacitance which varies from about 50 to 200-300 pF depending on the length of the strips.

#### 246 4.1.1 Dynamic Range and Noise Requirements

The dynamic range for the Micromegas detectors is determined by the maximum primary ionization charge, the fraction collected, and the maximum operating gas gain. Assuming a maximum gas gain of 40,000, the dynamic range is 320 fC. The noise is determined by the requirement of single primary electron detection with a threshold 5 times the RMS noise, a gas gain of 30,000, collecting half of the charge, and the maximum possible electrode capacitance of 200 pF. These conditions determine the required noise level to be at 0.5 fC or about 3,000 electrons RMS.

| F             | ix    | Detail                                                                                                                           | Simulation Result                                                                                                           |

|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| ADC jinearity |       | • filter ADC bias lines                                                                                                          | <ul> <li>periodic non-linearity removed</li> <li>probability of substantial improvement in yield</li> </ul>                 |

|               |       | <ul> <li>improve bias matching for uniformity, all ADCs</li> <li>fix saturation overshoot in output peak current, all</li> </ul> | <ul> <li>gain and saturation uniformity strongly<br/>improved</li> </ul>                                                    |

| Reset         |       | <ul> <li>add soft reset to soft-reset register</li> <li>merge reset paths in channel discriminator</li> </ul>                    | <ul> <li>soft-reset at ENA low now properly generated</li> <li>no locking occurs for any configuration, verified</li> </ul> |

| SFM           |       | <ul><li> add full-mirror to third stage</li><li> add two bits (SLH SLXH) for additional high-bias</li></ul>                      | • no failing channels at all process corners in SFM mode                                                                    |

| stlc          |       | • remove MA bridge and add MOSCAP for Antenna ratio                                                                              | • no failing channels at all process corners in 256 MC passes                                                               |

| Baseline      | yield | <ul> <li>use PMOS bias in second stage of amplifier</li> <li>increase drive in third stage of shaper</li> </ul>                  | • no failing channels at all process corners in 256 MC passes                                                               |

| Trim DAC      |       | <ul><li> double driver size in trimming amplifier</li><li> improve matching in trim current source</li></ul>                     | • VMM3a will cover > 32mV at all process corners                                                                            |

| Startup       |       | add soft reset to stop register                                                                                                  | • VMM3a won't need startup/register sequence                                                                                |

| DRC, LVS      |       | • locals in progress, chip-level queued                                                                                          |                                                                                                                             |

Figure 3: VMM3a: Status of fixes implemented from VMM3 and simulation updates.

#### 253 4.2 sTGC Detectors

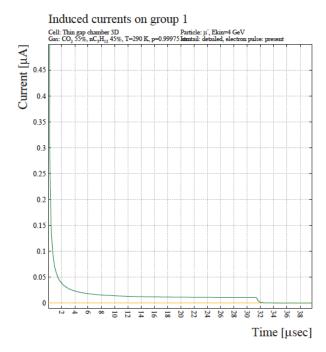

For the sTGC chambers, there are 3 different types of active elements on a detector: strips, 254 wires, and pads. All the three are read out via the VMM. Strips provide the precision coordinate 255 measurement for track reconstruction, wires for the second coordinate, and pads are used for 256 triggering purposes requiring a 3 out of 4 coincidence between the signals of pads in consecutive 257 layers. The wire signals are negative while both the strip and pad signals are positive. Hence 258 the need for the VMM to handle both polarities. A typical simulated current waveform from 259 an sTGC detector is shown in Figure 5. The total charge and the long ion tail impose specific 260 requirements on the processing of the sTGC signals and are outlined below. However VMM3a 261 simulations and updated sTGC requirements will be presented during the review. 262

#### 263 4.3 Wire Signals

- 1. The VMM should recover from wire signals of  $\langle Q_w \rangle = 6 \,\mathrm{pC}$  within 200 ns.

- 265 2. The linearity is not a critical factor here; however it is desirable for the linearity up to 266 2 pC to be known in order to apply offline corrections.

#### <sup>267</sup> 4.4 Pad Signals

- 1. In ADC mode, the VMM should recover from pad signals of  $\langle Q_p \rangle = \langle Q_w \rangle /2 =$ 3 pC within 250 ns.

- 270 2. The linearity is not a critical factor here; however it is desirable for the linearity up to 271 2 pC to be known in order to apply offline corrections.

Figure 4: Simulated current induced by the motion of electrons and positive ions during the avalanche formation within the  $128 \,\mu\text{m}$  amplification region of micromegas detector (the actual input to the VMM is of negative polarity).

- 3. In direct-timing-only mode (Time-over-Threshold and 6-bit ADC):

- (b) if the pulse charge is more than  $6 \,\mathrm{pC}$ , the dead time increases with the charge and at 50 pC is expected to reach  $\approx 1 \,\mu$ s from the peak.

#### 277 4.5 Strip Signals

- 1. The VMM should recover from strip signals of  $\langle Q_s \rangle = \langle Q_w \rangle / 6 = 1 \text{ pC}$  within 200 ns. The factor of 6 comes from the assumption that the signal will be distributed over three strips on average.

- 281 2. Linearity within  $\pm 2\%$  up to 2 pC is required.

## <sup>282</sup> 4.6 Input Capacitance and Rate per VMM

The capacitance of the largest pad on sTGC detectors will be 2nF or less, defining the

maximum capacitance the VMM must work within the requirements set out in the pre ceding sections, in particular in terms of dead time and recovery time.

286 2. The expected/estimated maximum rate at luminosity of  $7 \times 10^{34}$  is 0.8 MHz per VMM 287 channel for pads and 0.9 MHz per VMM channel for strips. An average strip multiplicity 288 of 4.7 is assumed in this, including from neighbor-on mode.

Figure 5: Simulated current induced by the motion of electrons and positive ions in an sTGC detector.

## 289 4.7 Input DC Current VMM channel

DC current in the input of a channel should not exceed 100 nA if the current is of the same polarity as the signal, or 1 nA for a DC current of opposite polarity.

## <sup>292</sup> 4.8 Dynamic Range and Noise Requirements

As mentioned in the previous sections the sTGC signals span a very large range from 1 pC on a given strip to about 50 pC on a pad. The dynamic range for the precision strip measurement is 2 pC . Assuming that one wants to measure 2.5% of this charge with a 2% resolution and a 200 pF electrode capacitance, the required noise level for a 25 ns integration time should be about 1 fC , or 6250 electrons. The noise for the digital signals from the pads with much larger capacitance (up to 2 nF) will be substantially higher, increasing at about 8 electrons per pF.

# <sup>299</sup> 5 Physical Description of the VMM and Layout recommenda <sup>300</sup> tions

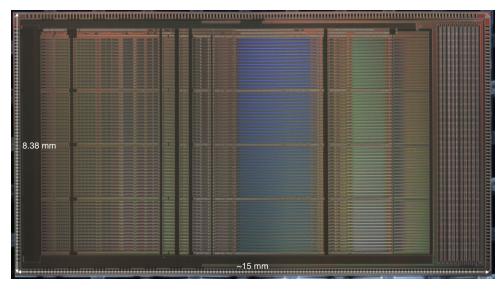

The VMM is a fully custom ASIC fabricated in the 130 nm Global Foundries 8RF-DM process (former IBM 8RF-DM). In this section the VMM3a is described. It should be noted that the pin assignment and layout are identical to those of the VMM3 version. In Table 3 the Input/ Output signals will be described.

The VMM3a will be packaged in a 400 ball, 1 mm pitch BGA. The device size is  $21 \times 21 \text{ mm}^2$ consistent with the pitch of the Micromegas detectors. The VMM3 layout size is  $15.308 \times$   $8.384 \text{ mm}^2$  and the die size  $15.308 \times 8.464 \text{ mm}^2$ . The die layout and size of the VMM3 is shown in Figure 6. The ball assignment is shown in Figure 7, and the detailed pin list and their functions in Table 1.

Figure 6: VMM3a die layout

| Α            | Vddp  | Vddp | Vddp | Vss | Vss | Vss | Vss | tdo | Vdd | Vdd   | V<br>ssad | V<br>ssad | V V<br>ssad ssad     | VV<br>ddad ddad | VV<br>ddad ddad | +SETT-               |           |               |

|--------------|-------|------|------|-----|-----|-----|-----|-----|-----|-------|-----------|-----------|----------------------|-----------------|-----------------|----------------------|-----------|---------------|

| в            | Veidp | Vddp | Vddp | Vss | Vss | Vss | Vss | pdo | Vdd | Vdd   | Vdd       | Vssd      | +TKO-                | + CKTP -        | SDI SDO         | CS SOK               | Vddp      | preamp +1.2V  |

| С            | iO    | i1   | i2   | i3  | Vss | Vss | Vss | mo  | Vdd | Vdd   | Vdd       | Vssd      | <b>+TKI -</b>        | +CKBC-          | +BNA-           | +CK6B-               |           | b             |

| D            | i4    | i5   | i6   | i7  | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Vsed      | +CKTK-               | +DT0-           | +DT1-           | +CKART-              | Vdd       | analog +1.2V  |

| E            | i8    | i9   | i10  | i11 | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Vsed      | +ART-                | +CKDT-          | + t0 -          | + t1 -               | Vss       | analog 0V     |

| F            | i12   | i13  | i14  | i15 | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Vssd      | + t2 -               | + t3 -          | + t4 -          | + t5 -               |           | J             |

| G            | i16   | i17  | i18  | i19 | Vss | Vss | Vss | Vdd | Vdd | Vssd  | Vsed      | Vssd      | + t6 -               | + t7 -          | + t8 -          | + t9 -               | V<br>ddad | ADC +1.2V     |

| н            | i20   | i21  | i22  | i23 | Vss | Vss | Vss | Vdd | Vdd | Vssd  | + t       | 10 -      | + t11 -              | + t12 -         | + t13 -         | + t14 -              | V<br>ssad | ADC 0V        |

| J            | i24   | i25  | i26  | i27 | Vss | Vss | Vss | Vdd | Vdd | Vssd  | + t       | 15 -      | <mark>+ t16</mark> - | + t17 -         | + t18 -         | <mark>+ t19 -</mark> | ssau      | 12001         |

| K            | i28   | i29  | i30  | i31 | Vss | Vss | Vss | Vdd | Vdd | Vssd  | + ť       | 20 -      | + t21 -              | + t22 -         | + t23 -         | + t24 -              | V ddd     | digital +1.2V |

|              | i32   | i33  | i34  | i35 | Vss | Vss | Vss | Vdd | Vdd | Valak | + t       | 25 -      | <mark>+ t26</mark> - | + t27 -         | + t28 -         | + t29 -              | Vssd      | digital 0V    |

| Μ            | i36   | i37  | i38  | i39 | Vss | Vss | Vss | Vdd | Vdd | Valak | + t       | 30 -      | + t31 -              | + t32 -         | + t33 -         | + t34 -              |           | ang.com o r   |

| Ν            | i40   | i41  | i42  | i43 | Vss | Vss | Vss | Vdd | Vdd | Vatak | + t       | 35 -      | <mark>+ t36</mark> - | + t37 -         | + t38 -         | + t39 -              |           | analog in     |

| Ρ            | i44   | i45  | i46  | i47 | Vss | Vss | Vss | Vdd | Vdd | Vable | Valat     | l Vatak   | + t40 -              | + t41 -         | + t42 -         | + t43 -              |           |               |

| R            | i48   | i49  | i50  | i51 | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Valak     | + t44 -              | + t45 -         | + t46 -         | + t47 -              |           | analog out    |

|              | i52   | i53  | i54  | i55 | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Valak     | + t48 -              | + t49 -         | + <b>t5</b> 0 - | + t51 -              |           |               |

| U            | i56   | i57  | i58  | i59 | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Valak     | + t52 -              | + t53 -         | + t54 -         | + t55 -              |           | digital SE IO |

| $\mathbf{V}$ | i60   | i61  | i62  | i63 | Vss | Vss | Vss | Vdd | Vdd | Vdd   | Vdd       | Vable     | + <b>t5</b> 6 -      | + t57 -         | + t58 -         | + t59 -              |           |               |

| W            | Vddp  | Vddp | Vddp | Vss | Vss | Vss | Vss | Vdd | Vdd | Vdd   |           |           | + t60 -              |                 | + t62 -         |                      | + xxx     | SLVS IO       |

| Υ            | Vddp  | Vddp | Vddp | Vss | Vss | Vss | Vss | Vdd | Vdd | Vdd   | ssad      | ssad      | ssad ssad            | ddad ddad       | VV<br>ddad ddad | +SETB -              |           |               |

|              | 1     | 2    | 3    | 4   | 5   | 6   | 7   | 8   | 9   | 10    | 11        | 12        | 13 14                | 15 16           | 17 18           | 19 20                |           |               |

Figure 7: VMM3a pinout (top view)

## <sup>310</sup> 5.1 Layout recommendations and requirements

<sup>311</sup> User should consult with MMFE8, pFEB, sFEB and VMM designers. The layout has undergone <sup>312</sup> several upgrades and it is still in progress, and there is no comprehensive document at this time.

## 313 6 Manufacturer

## 314 6.1 Wafer Processing

<sup>315</sup> The VMM will be fabricated in the Global Foundries (former IBM) 130 nm 8RF-DM CMOS <sup>316</sup> process through MOSIS. Because of its size it is more economical to be submitted in a cus-<sup>317</sup> tom dedicated run even for prototypes. The wafers will be thinned to 0.010" (250  $\mu$ m), diced, <sup>318</sup> inspected, and sorted to waffle packs.

## 319 6.2 Packaging

As mentioned in Section 5 the VMM3a will be packaged in a 400 ball BGA with 1 mm pitch. The design of the new substrate will start immediately after the layout is completed in consultation with the groups designing the front end cards, and the packaging house. We are in contact with three new packaging vendors, IMEC, NOVAPACK, and Signetics. All three have agreed to accept the project in spite of the low (by industry standards) volume of 50,000 chips at production.

## 326 6.3 Export License Issues

The design includes PROMPT circuit. The appropriate office at BNL has determined that the VMM does not need Export Administration Regulations (EAR) license and, therefore, it can be freely distributed to all of our NSW collaborators.

## 330 **7** Power

The VMM is designed to operate at a nominal voltage of 1.2 V. It requires four different supplies in order to minimize the contribution to the Equivalent Noise Charge (ENC) of the digital and mixed analog-digital circuits. These four power supplies are:

• Vddp: Charge amplifier supply connected to the sources of the p-channel input MOSFETs

- Vdd: Powers all other analog circuits

- Vddad: Mixed Analog–Digital (ADC)

- Vddd: Supplies the digital circuits and SLVS drivers

Table 2 summarizes the requirements and tolerances for the four supplies. The power dissipation

$_{339}$   $\,$  depends on the selected functionality and mode of operation. It ranges from  $500\,\mathrm{mW}$  to  $800\,\mathrm{mW}.$

For example the SLVS outputs can be disabled when not needed, e.g., in Micromegas operation

$_{\rm 341}~$  or the wire readout in the sTGC detectors.

| BGA Ball Function                                                                               |                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Ball/Pin name                                                                                   | Description-Comments                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Vdd,Vss                                                                                         | Analog supplies 1.2 V and grounds 0 V – 123 pins total, max current $400\mathrm{mA}$                                                                                                                                                                                                               |  |  |  |  |  |

| Vddad, VssadMixed-signal (ADC) supplies 1.2 V and grounds 0 V - 16 pins, max<br>current ~200 mA |                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Vddd, Vssd                                                                                      | Digital supplies 1.2 V and grounds 0 V 22 pins                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Vddp                                                                                            | Charge amplifier supplies $1.2 \text{ V}$ 12 pins, max current $\sim 150 \text{ mA}$                                                                                                                                                                                                               |  |  |  |  |  |

| i0-i63                                                                                          | Analog inputs ESD protected                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| mo                                                                                              | monitor multiplexed analog output                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| pdo                                                                                             | Peak Detector multiplexed output (not used in NSW).                                                                                                                                                                                                                                                |  |  |  |  |  |

| tdo                                                                                             | Time detector multiplexed analog output (not used by NSW).                                                                                                                                                                                                                                         |  |  |  |  |  |

| SETT                                                                                            | Ch 0 neighbor trigger, Custom LVDS - Bi-directional (chip-to-chip)                                                                                                                                                                                                                                 |  |  |  |  |  |

| CKBC                                                                                            | Bunch Crossing clock, SLVS input, Advances 12-bit Gray-code BC counter                                                                                                                                                                                                                             |  |  |  |  |  |

| CKTP                                                                                            | Test Pulse Clock, SLVS input                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| SDI                                                                                             | Configuration SPI data input, 1.2 V CMOS                                                                                                                                                                                                                                                           |  |  |  |  |  |

| SDO                                                                                             | Configuration SPI data output, Tristated if chip is not selected, CMOS                                                                                                                                                                                                                             |  |  |  |  |  |

| CS                                                                                              | Configuration SPI chip select, CMOS                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SCK                                                                                             | Configuration SPI clock, CMOS                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| TKI                                                                                             | BCR/OCR. SLVS input, Token input in analog mode                                                                                                                                                                                                                                                    |  |  |  |  |  |

| ТКО                                                                                             | Token output SLVS output, Used in analog mode only                                                                                                                                                                                                                                                 |  |  |  |  |  |

| ENA                                                                                             | <ul> <li>Acquisition start/stop and provides acquisition reset at falling edge:</li> <li>ENA high: acquisition is enabled</li> <li>internally enabled after 40 ns from ena high</li> <li>in two-phase (analog) mode is acquisition</li> <li>in continuous (divital) mode is acquisition</li> </ul> |  |  |  |  |  |

| CK6B                                                                                            | <ul> <li>in continuous (digital) mode is acquisition and readout</li> <li>6-bit direct output clock, SLVS input</li> </ul>                                                                                                                                                                         |  |  |  |  |  |

| CK0B                                                                                            | Level-0 accept (L0). Token clock (non-NSW use), SLVS input                                                                                                                                                                                                                                         |  |  |  |  |  |

| DT0                                                                                             | First data line in digital DDR mode L0, Data 1 in continuous mode<br>(flag and address in analog mode), SLVS output                                                                                                                                                                                |  |  |  |  |  |

| DT1                                                                                             | Second data line (first bit) in digital DDR mode L0, Flag and Data 0 line in continuous mode, SLVS output                                                                                                                                                                                          |  |  |  |  |  |

| CKART                                                                                           | Address in Real Time (ART) clock, SLVS input                                                                                                                                                                                                                                                       |  |  |  |  |  |

| ART                                                                                             | ART output, SLVS output                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| CKDT                                                                                            | Data clock SLVS input                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| ttp0-ttp63                                                                                      | Direct digital outputs, SLVS output                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SETB                                                                                            | ch63 neighbor trigger (see SETT)                                                                                                                                                                                                                                                                   |  |  |  |  |  |

## Table 1: Pad/Pin Assignment/Function

| Supply | Voltage[V]  | Ripple                                      | Max Current [mA] |

|--------|-------------|---------------------------------------------|------------------|

| Vddp   | $1.2\pm5\%$ | $<10\mu\mathrm{V}\;\mathrm{rms}$ , 1–10 MHz | 150              |

| Vdd    | $1.2\pm5\%$ | $<100\mu\mathrm{V}~\mathrm{rms}$ , 1–10 MHz | 400              |

| Vddad  | $1.2\pm5\%$ | $<$ 100 $\mu V~\mathrm{rms}$ , 1–10 MHz     | 200              |

| Vddd   | $1.2\pm5\%$ | $<1\mathrm{mV}$ rms, 1–10 MHz               | 150              |

Table 2: VMM Power Supply Requirements

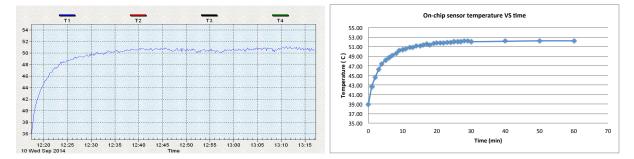

## 342 8 Cooling

As mentioned already the VMM power dissipation depends on the features used with a maximum of  $\sim 1 \,\mathrm{W}$ . Although not excessive, enclosed in a Faraday cage in the high density environment of the NSW (especially in the case of Micromegas detectors), cooling of the VMM chips is mandatory. A system with water as coolant is being designed by the teams working on the detectors.

The IBM CMOS8RF Design Manual specifies the operating temperature range to be from -55 °C to 125 °C. However device life time degrades rapidly at high temperatures. The case temperature should be kept below 50 °C and preferably in the range 30–40 and should be verified and compared to the junction temperature provided by the VMM ASIC. The VMM includes a temperature sensor which can be read out by appropriately programming the monitor output and digitized by the SCA setting (in configuration mode) scmx = 0, sm5–sm0 = 000100 (see Table 6). The die temperature is approximately given by:

$$^{\circ}\mathrm{C} = \frac{725 - V_{\mathrm{sensor}}}{1.85}$$

where  $V_{\text{sensor}}$  is the temperature sensor reading in mV. The case temperature of a single-chip

Figure 8: Left plot, the VMM case temperature. Right plot, the junction temperature as a function of time after turn-ON

348

<sup>349</sup> board was measured from turn ON until thermal equilibrium and was compared with the die

$_{350}$  temperature. The results are shown in Figure 8. The difference of about 2 °C is consistent with

the typical junction to case thermal resistance for BGA devices of similar size,  $\sim 1$  °C/W.

## 352 9 Input and Output

The input and output connections of the VMM are shown in Table 3. It describes the name of the signal and BGA ball address, the connection destination and direction, the electrical specification and a short description.

The single-ended signals are 1.2 V CMOS. The SLVS signals conform to the SLVS-400 JEDEC standard.

The *sett, setb* signals which, are used for the inter-chip communication of the neighbor logic, are custom bi-directional LVDS signals.

## <sup>360</sup> 10 Detailed Functional Description and Specifications

As mentioned already, the VMM has four independent data paths and can operate in one of two modes, two-phase (analog) and continuous (digital). Configuration of the ASIC is yet another mode. In the following sections these modes and the relevant specifications will be described in detail.

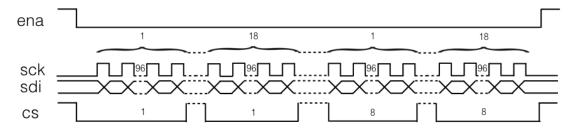

## 365 10.1 Configuration Process

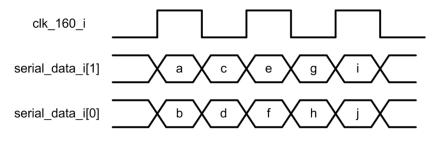

The ASIC can be put in configuration mode by having the ena signal low and the cs low. When 366 in the configuration mode, the ASIC registers are accessible through the SPI clock sck and 367 the data inputs sdi. The data transmitted are shifted at the falling edge of sck in groups of 368 96-bits and latched when the cs is high. The contents of the configuration register is available 369 at the *sdo* output for daisy-chain configuration. For the NSW, up to 8 VMM devices will be 370 mounted on a front end card and they will be individually configurable. In this mode there are 371 common data input, data output, clock buses and individual chip select pins. For this reason if 372 a VMM is not selected its configuration data output, sdo, is tri-stated. The timing diagram of 373 the configuration of up to  $8 \times VMMs$  is shown in Figure 9. 374

Figure 9: Configuration timing diagram of 8×VMMs.

The configuration is  $18 \times 96$ -bits of which  $2 \times 96$ -bits are the global registers and the rest are channel registers. Each of the 64 channels has a 24-bit configuration. The list of registers is shown in Tables 6,5. The sequence of registers to be written is global bank-1, channel registers, global bank-2. The first bit to write is the last bit of global bank-2 and the last bit to write is the global bank-1 first bit. The sequence is shown in Table 4.

Version: v1.0– April 23, 2018– 18 of 40

| Table 3: Input and Output Signals of the VMM3a. |                 |                         |                                 |                                                                                    |  |  |

|-------------------------------------------------|-----------------|-------------------------|---------------------------------|------------------------------------------------------------------------------------|--|--|

| Name,<br>Position                               | Con-<br>nection | In,<br>Out<br>or<br>I/O | Type of<br>Signal or<br>Max/Min | Description                                                                        |  |  |

| sett<br>A19-20                                  | VMM             | I/O                     | Custom LVDS<br>Bi-directional   | Channel 0 force-neighbor signal                                                    |  |  |

| setb<br>Y19-20                                  | VMM             | I/O                     | Custom LVDS<br>Bi-directional   | Channel 63 force-neighbor signal                                                   |  |  |

| ckbc (BCclk)<br>C15-16                          | ROC             | In                      | SLVS                            | Bunch crossing clock of 40 MHz /<br>External trigger signal                        |  |  |

| cktp (Test Pulse)<br>B15-16                     | ROC             | In                      | SLVS                            | Test pulse clock                                                                   |  |  |

| cktk (Level-0)<br>D13-14                        | ROC             | In                      | SLVS                            | Token clock / L0 (digital NSW mode)                                                |  |  |

| ckdt (ROclk)<br>E15-16                          | ROC             | In                      | SLVS                            | Data clock                                                                         |  |  |

| ckart (ARTclk)<br>D19-20                        | ROC             | In                      | SLVS                            | ART clock                                                                          |  |  |

| sdi<br>B17                                      | SCA             | In                      | CMOS                            | Configuration data input                                                           |  |  |

| sdo<br>B18                                      |                 | Out                     | CMOS                            | Configuration data output (not<br>used, HiZ state in NSW)                          |  |  |

| cs<br>B19                                       | SCA             | In                      | CMOS                            | Chip Select, active low                                                            |  |  |

| sck<br>B20                                      | SCA             | In                      | CMOS                            | Input SPI clock                                                                    |  |  |

| t0-t63<br>E17-W20                               | TDS             | Out                     | SLVS                            | Direct digital outputs                                                             |  |  |

| mo<br>C9                                        | SCA             | Out                     | 0-1 V                           | Analog output for calibration                                                      |  |  |

| tki (BCR/OCR)<br>C13-14                         | ROC             | In                      | SLVS                            | Token input (an. mode) / (BCR-<br>OCR) / acceptance window in<br>non-L0 cont. mode |  |  |

| tko<br>B13-14                                   |                 | Out                     | SLVS                            | Token output (analog mode, not<br>used in NSW)                                     |  |  |

| ena (ENA/Soft Reset)<br>C17-18                  | ROC             | In                      | SLVS                            | Acquisition start/stop                                                             |  |  |

| ck6b<br>C19-20                                  | TDS             | In                      | SLVS                            | 6-bit ADC Clock                                                                    |  |  |

| art<br>E13-14                                   | ART2GBT         | Out                     | SLVS                            | Address in Real Time                                                               |  |  |

| data0<br>D15-16                                 | ROC             | Out                     | SLVS                            | data line                                                                          |  |  |

| data1<br>D17-18                                 | ROC             | Out                     | SLVS                            | data line first bit, flag in cont.                                                 |  |  |

VMM Specifications

| Register Type                  | Sequence                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| global registers - first bank  | sp sdp sbmx sbft sbfp sbfm slg sm5:sm0 scmx<br>sfa sfam st1:0 sfm sg2:0 sng stot sttt ssh<br>stc1:0 sdt9:0 sdp9:0 sc010b:sc110b sc08b:sc18b<br>sc06b:sc26b s8b s6b s10b sdcks sdcka sdck6b<br>sdrv stpp res00 res0 res1 res2 res3 slvs s32 stcr<br>ssart srec stlc sbip srat sfrst slvsbc slvstp slvstk<br>slvsdt slvsart slvstki slvsena slvs6b sL0enaV slh<br>slxh stgc nu nu nu nu reset reset |

| channel register (64×)         | sc sl st sth sm sm<br>x sd0:sd4 sz010b:sz410b sz08b:sz38b sz06b:sz26b nu                                                                                                                                                                                                                                                                                                                          |

| global registers - second bank | nu0:30 nskipm_i sL0cktest sL0dckinv sL0ckinv<br>sL0ena truncate_i0:5 nskip_i0:6 window_i0:2<br>rollover_i0:11 l0offset_i0:11 offset_i0:11 nu0:7                                                                                                                                                                                                                                                   |

Table 4: Sequence of Configuration Registers of the VMM3.

| Table 5: | Channel | Configuration | Registers | of the VMM. |

|----------|---------|---------------|-----------|-------------|

|----------|---------|---------------|-----------|-------------|

| Channel bits (defaults are 0)          | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| sc [0 1]                               | large sensor capacitance mode ([0] $<\!\!\sim\!\!200\mathrm{pF}$ , [1] $>\!\!\sim\!\!200\mathrm{pF}$ ) |

| sl [0 1]                               | leakage current disable [0=enabled]                                                                    |

| st [0 1]                               | 300 fF test capacitor [1=enabled]                                                                      |

| sth [0 1]                              | multiplies test capacitor by 10                                                                        |

| sm [0 1]                               | mask enable [1=enabled]                                                                                |

| sd0-sd4 [0:0 through 1:1]              | trim threshold DAC, $1 \text{ mV}$ step ([0:0] trim $0 \text{ V}$ , [1:1] trim $-29 \text{ mV}$ )      |

| smx [0 1]                              | channel monitor mode ([0] analog output, [1] trimmed threshold))                                       |

| sz010b, sz110b, sz210b, sz310b, sz410b | 10-bit ADC offset subtraction                                                                          |

| sz08b, sz18b, sz28b, sz38b             | 8-bit ADC offset subtraction                                                                           |

| sz06b, sz16b, sz26b                    | 6-bit ADC offset subtraction                                                                           |

| Global bits (defaults are 0)       | Description                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| sp                                 | input charge polarity ([0] negative, [1] positive)                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| sdp                                | disable-at-peak                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

| sbmx                               | routes analog monitor to PDO output                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| sbft [0 1], sbfp [0 1], sbfm [0 1] | analog output buffers, [1] enable (TDO, PDO, MO)                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| slg                                | leakage current disable ([0] enabled)                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| sm5-sm0, scmx                      | monitor multiplexing.                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|                                    | <ul> <li>Common monitor: scmx, sm5-sm0 [0 000001 to 000100], pulser DAC (after pulser switch), threshold DAC, bandgap reference, temperature sensor)</li> <li>channel monitor: scmx, sm5-sm0 [1 000000 to 111111], channels 0 to 63</li> </ul> |  |  |  |  |  |  |  |  |  |  |

| sfa [0 1], sfam [0 1]              | ART enable (sfa [1]) and mode (sfam [0] timing at threshold, [1] timing at peak)                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| st1,st0 [00 01 10 11]              | peaktime $(200, 100, 50, 25 \text{ ns})$                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| sfm [0 1]                          | enables dynamic discharge for AC coupling ([1] enable                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| sg2,sg1,sg0 [000:111]              | gain $(0.5, 1, 3, 4.5, 6, 9, 12, 16 \mathrm{mV/fC})$                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

| sng                                | neighbor (channel and chip) triggering enable                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| stot $[0 \ 1]$                     | timing outputs control 1 (s6b must be disabled)                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

|                                    | • stpp,stot[00,01,10,11]: TtP,ToT,PtP,PtT                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

|                                    | • TtP: threshold-to-peak                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|                                    | • ToT: time-over-threshold                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|                                    | • PtP: pulse-at-peak (10ns) (not available with s10b)                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|                                    | • PtT: peak-to-threshold (not available with s10b)                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| sttt [0 1]                         | enables direct-output logic (both timing and s6b)                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| ssh [0 1]                          | enables sub-hysteresis discrimination                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| stc1,stc0 [00 01 10 11]            | TAC slope adjustment (60, 100, 350, 650 ns )                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| sdt9-sdt0 [0:0 through 1:1]        | coarse threshold DAC                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

| sdp9-sdp0 [0:0 through 1:1]        | test pulse DAC                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| sc010b,sc110b                      | 10-bit ADC conv. time (increase subtracts 60 ns)                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| sc08b,sc18b                        | 8-bit ADC conv. time (increase subtracts 60 ns)                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |

| sc06b, sc16b, sc26b                | 6-bit ADC conversion time                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| s8b                                | 8-bit ADC conversion mode                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| s6b                                | enables 6-bit ADC (requires sttt enabled)                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| s10b                               | enables high resolution ADCs (10/8-bit ADC enable)                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| sdcks                              | dual clock edge serialized data enable                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| sdcka                              | dual clock edge serialized ART enable                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| sdck6b                             | dual clock edge serialized 6-bit enable                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| sdrv                               | tristates analog outputs with token, used in analog mode                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| stpp [0 1]                         | timing outputs control 2                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| slvs                               | enables direct output IOs                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| stcr                               | enables auto-reset (at the end of the ramp, if no stop occurs)                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |

| ssart                              | enables ART flag synchronization (trail to next trail)                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

Table 6: Global Configuration Registers of the VMM3.

| Global bits (defaults are 0) | Description                                                    |

|------------------------------|----------------------------------------------------------------|

| s32                          | skips channels 16-47 and makes 15 and 48 neighbors             |

| stlc                         | enables mild tail cancellation (when enabled, overrides sbip)  |

| srec                         | enables fast recovery from high charge                         |

| sbip                         | enables bipolar shape                                          |

| srat                         | enables timing ramp at threshold                               |

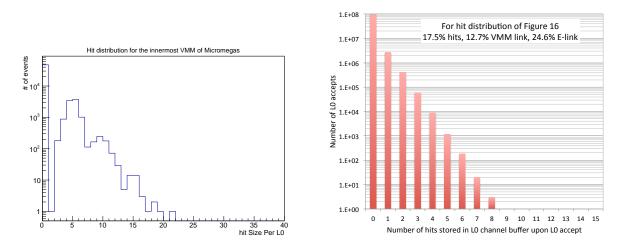

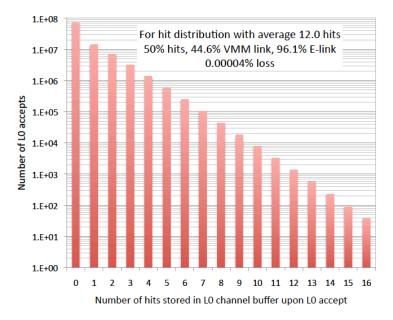

| sfrst                        | enables fast reset at 6-b completion                           |