# SAMPA V3 Specification

Revision 0.2

Arild Velure<sup>1</sup> Bruno Sanches<sup>2</sup>

September 20, 2018

<sup>1</sup>e-mail: Arild.Velure@cern.ch

$^2 e\text{-mail: Bruno.Caval cante.De.Souza.Sanches@cern.ch}\\$

## Revision

- **0.1** Initial draft

- **0.2** Functional description, Interfaces and protocols and Circuit description sections modified. Reviewer: Raul Acosta Hernandez

# **Contents**

| Func | ctional d | escription                             | 6  |

|------|-----------|----------------------------------------|----|

| 1.1  | Analog    | front-end                              | 6  |

| 1.2  | Analog    | to digital converter                   | 6  |

| 1.3  | Pre-trig  | ger samples delay                      | 7  |

| 1.4  | Digital   | signal conditioning                    | 7  |

|      | 1.4.1     | First baseline correction              | 8  |

|      | 1.4.2     | Digital shaper                         | 10 |

|      | 1.4.3     | Baseline correction and subtraction II | 14 |

|      | 1.4.4     | Baseline correction III                | 15 |

| 1.5  | Compre    | ession                                 | 17 |

|      | 1.5.1     | Huffman compression                    | 17 |

|      | 1.5.2     | Zero suppression                       | 17 |

|      | 1.5.3     | Lossy data compression                 | 19 |

| 1.6  | Channe    | l ordering                             | 20 |

| 1.7  | Data fo   | rmatting unit and Ring buffer          | 20 |

|      | 1.7.1     | Data formatting unit (DFU)             | 20 |

|      | 1.7.2     | Ring buffer                            | 21 |

| 1.8  | Serializ  | ing                                    | 23 |

|      | 1.8.1     | Standard Modes                         | 23 |

|      | 1.8.2     | Test Modes                             | 23 |

| 1.9  | Event n   | nanaging                               | 23 |

|      |           | haining                                | 24 |

|      | •         | Neighbor module                        | 24 |

|   | 1.11 | Direct . | ADC serialization mode    | 25 |

|---|------|----------|---------------------------|----|

| 2 | Inte | rfaces a | nd protocols              | 27 |

|   | 2.1  | Analog   | front-end                 | 27 |

|   | 2.2  | Slow C   | ontrol                    | 27 |

|   | 2.3  | Serial i | nterface                  | 28 |

|   |      | 2.3.1    | Protocol                  | 29 |

|   |      | 2.3.2    | Heartbeat packet          | 29 |

|   |      | 2.3.3    | Sync packet               | 30 |

|   |      | 2.3.4    | Types of packets          | 31 |

|   | 2.4  | Daisy o  | haining                   | 32 |

|   | 2.5  | Direct . | ADC serialization         | 34 |

|   | 2.6  | Test int | erfaces                   | 35 |

|   |      | 2.6.1    | JTAG                      | 35 |

|   |      | 2.6.2    | Scanchain                 | 37 |

|   |      | 2.6.3    | Memory built in tester    | 38 |

|   | 2.7  | Hardwa   | are address               | 39 |

|   | 2.8  | Sync an  | nd trigger                | 39 |

|   | 2.9  | Clock a  | and reset                 | 40 |

|   |      | 2.9.1    | Clock                     | 40 |

|   |      | 2.9.2    | Reset                     | 41 |

| 3 | Pori | isters   |                           | 45 |

| J | 3.1  |          | registers                 |    |

|   | 3.1  | 3.1.1    | Pin status                |    |

|   |      | 3.1.2    | Event management          |    |

|   |      | 3.1.2    | Channel register access   |    |

|   |      | 3.1.4    |                           |    |

|   |      |          | Channel ordering          |    |

|   |      | 3.1.5    | ADC configuration         |    |

|   |      | 3.1.6    | Serial link configuration |    |

|   |      | 3.1.7    | Data compression          |    |

|   |      | 3.1.8    | Power saving features     | 50 |

|   |      | 3.1.9    | Test functionality              | . 51 |

|---|------|----------|---------------------------------|------|

|   | 3.2  | Channe   | el specific registers           | . 57 |

|   |      | 3.2.1    | Data path configuration         | . 58 |

|   |      | 3.2.2    | Digital shaper                  | . 58 |

|   |      | 3.2.3    | BC1                             | . 59 |

|   |      | 3.2.4    | BC2                             | . 60 |

|   |      | 3.2.5    | BC3                             | . 62 |

|   |      | 3.2.6    | Zero suppression                | . 62 |

| 4 | Circ | uit desc | ription                         | 64   |

|   | 4.1  | Analog   | gue front-end                   | . 64 |

|   | 4.2  | ADC .    |                                 | . 64 |

|   | 4.3  | Config   | urable Reference Voltage Source | . 64 |

|   | 4.4  | Triple l | Modular Redundancy              | . 65 |

|   | 4.5  | Filters  | Data-path                       | . 65 |

|   | 4.6  | Pre-trig | gger samples delay              | . 67 |

|   | 4.7  | Baselin  | ne Correction I                 | . 67 |

|   | 4.8  | Digital  | shaper                          | . 70 |

|   | 4.9  | Baselin  | ne Correction II                | . 72 |

|   | 4.10 | Baselin  | ne Correction III - Slope based | . 74 |

|   | 4.11 | Huffma   | an                              | . 74 |

|   | 4.12 | Zero su  | appression                      | . 74 |

|   | 4.13 | Data fo  | ormatting                       | . 78 |

|   | 4.14 | Serializ | zing                            | . 78 |

|   | 4.15 | Direct . | ADC serialization mode          | . 79 |

| 5 | Data | sheet    |                                 | 81   |

|   | 5.1  | Electric | cal specifications              | . 81 |

|   |      | 5.1.1    | Power supplies                  |      |

|   |      | 5.1.2    | ADC voltage reference           |      |

|   |      | 5.1.3    | Decoupling                      |      |

|   |      | 5.1.4    | Absolute maximum ratings        |      |

|     | 5.1.5   | Digital IO pad characteristics       | 82 |

|-----|---------|--------------------------------------|----|

|     | 5.1.6   | Power consumption                    | 82 |

|     | 5.1.7   | SLVS termination                     | 82 |

|     | 5.1.8   | Internal pull-up/pull-down           | 83 |

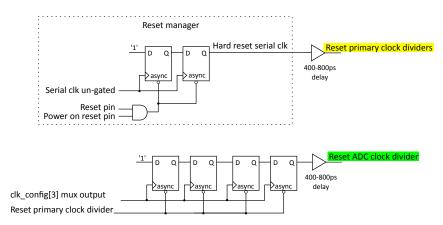

|     | 5.1.9   | Reset generation                     | 83 |

|     | 5.1.10  | Configuration pins pull-up/pull-down | 83 |

|     | 5.1.11  | Floating/unused inputs               | 84 |

|     | 5.1.12  | I2C                                  | 84 |

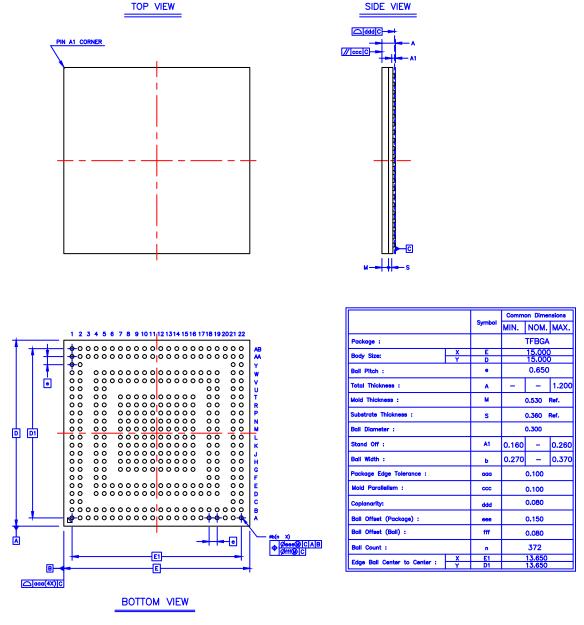

| 5.2 | Packag  | e description                        | 85 |

|     | 5.2.1   | Mechanical characteristics           | 85 |

|     | 5.2.2   | Pinout                               | 85 |

| 5.3 | Related | documentation                        | 92 |

| 5.4 | Known   | issues                               | 93 |

|     | 5.4.1   | V2                                   | 93 |

|     | 542     | V3/vA                                | 05 |

# **Chapter 1**

# **Functional description**

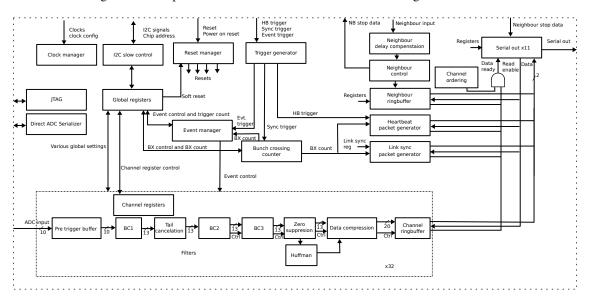

This section describes the functional operation of the main blocks of the SAMPA ASIC.

## 1.1 Analog front-end

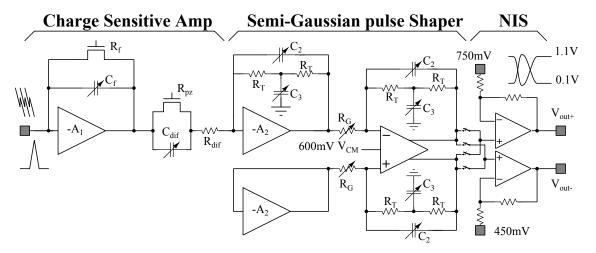

The front-end block is composed of a positive/negative polarity Charge Sensitive Amplifier (CSA) with a capacitive feedback  $C_f$  and a resistive feedback  $R_f$  connected in parallel, a Pole-Zero Cancellation (PZC) network, a high pass filter, two bridged-T second order low pass filters, a non-inverting stage, as shown in figure 1.1.

The first shaper is a scaled-down version of the CSA and generates the two first poles and one zero. A copy of the first shaper connected in unity gain configuration is implemented in order to provide a differential mode input to the next stage.

The second stage of the shaper is a fully differential second order bridged-T filter and it includes a Common-Mode Feed-Back network (CMFB). The non-inverting stage adapts the DC voltage level of the shaper output to use the full dynamic range of the ADC. It consists of a parallel connection of two equally designed Miller compensated amplifier.

The gain, polarity and shaping time of the front-end is programmable through external pins.

# 1.2 Analog to digital converter

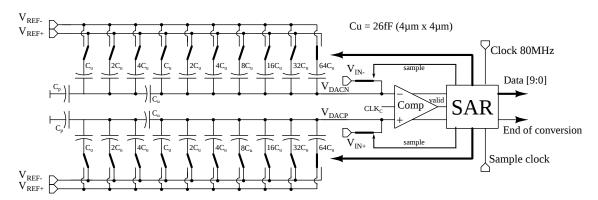

The ADC is based on a split capacitor fully differential successive approximation (SAR) topology. The SAR topology allows for low power with reasonable sample rates and resolution. The ADC has a resolution of 10-bit and a sample rate up to 20 Msamples/s. The block diagram of the ADC is shown in figure 1.2. The main parts of the circuit are: capacitive array, switches, comparator and the SAR control logic. The capacitor array is used to perform sample & hold and the digital to analog converter functions.

Figure 1.1: Block diagram of the analog front-end.

Figure 1.2: Block diagram of the ADC.

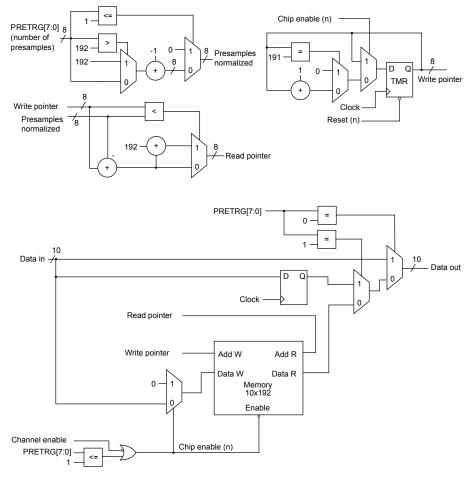

# 1.3 Pre-trigger samples delay

When running with an externally provided trigger signal, it is often needed to compensate for the delay between the triggering event and the reception of the trigger signal on the device. This compensation is done by delaying the incoming data by the same amount as the trigger signal. If one also wants to look at data prior to the triggering event, it is also possible to add more delay. It is possible to delay the data by up to 192 ADC cycles, corresponding to  $19.2 \,\mu\text{s}$  at  $10 \,\text{MHz}$ .

The configuration does not alter the length of the processing time window, it merely moves the trigger point in the sample stream earlier in time then when the trigger was received.

# 1.4 Digital signal conditioning

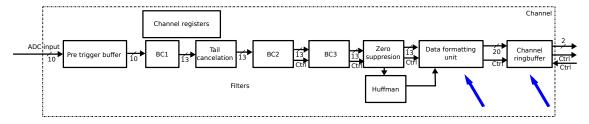

The objective of the Digital Signal Condition (DSC) is to increase the efficiency of the data compression algorithms (e. g. zero suppression). The DSC implements, in several subsequent stages (pipeline), different algorithms to condition and shape the signal. The DSC is comprised of four main building blocks

**Baseline Correction I (BCI)** It is the first stage of the data processor. It's main task is to remove the low frequency perturbations and systematic effects. This filter has different modes of operation depending on the application.

**Digital Shaper (DS)** It can be use for two different applications; tail cancellation or peaking time correction. A fourth order IIR filter is implemented. The choice of the filter parameters configure the system for one of the applications:

- Tail cancellation: an accurate cancellation of the signal tail is required in order to perform

the zero suppression efficiently. Since the filter coefficients for each channel are fully programmable and re-configurable, the circuit is able to cancel a wide range of signal tail shapes.

- Peaking time correction: some applications need the modification of the peaking time to

**Baseline Correction II** (**BCII**) This unit applies a baseline correction based on a moving average filter. This scheme removes non-systematic perturbations of the baseline that are superimposed to the signal. At the output of this block, the signal baseline is constant with an accuracy of 1 Least Significant Bit (LSB).

**Baseline Correction III (BCIII)** This unit applies a baseline correction through a slope based filter. It is provided as an alternative to the BCII filter as the BCII filter can potentially get stuck outside its thresholds in cases of very large perturbations.

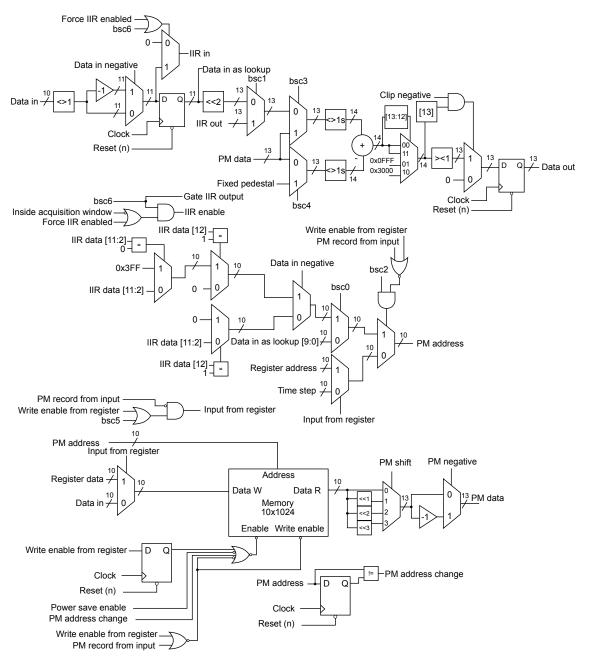

#### 1.4.1 First baseline correction

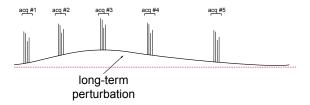

The perturbations affecting the signal from a gas chamber can be:

- Low-frequency spurious signals (in the range of less than one kilohertz). These perturb the detector signal by shifting its baseline by an amount that is almost constant (less than one ADC count) inside the processing time window. This type of signal perturbation could for instance be caused by

- Environmental changes e.g. drifts in temperature and voltage.

- Environmental variations due to differences in placement in the detector.

- Manufacturing/process variations.

Figure 1.3: Example of long term perturbations.

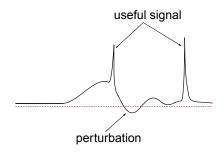

• Signal perturbations created by systematic effects, like those related to triggering of the detector, which affect the signal in terms of a superimposed noise pattern.

Figure 1.4: Example of gating perturbations.

To cope with the first effect, an IIR filter is implemented right at the output of the ADC. It has a programmable response time of  $\tau = 2^n$  sampling periods, where n is a value between zero and eight which needs to be adjusted to fit the (high frequency) noise of the environment. As the signals we are interested in also have a low frequency component, which should not be disturbed or taken into account for the baseline correction, the IIR filter has to be protected against these. There are two ways foreseen to do so to interrupt the IIR update (both maskable):

ALTRO description, not updated

- · during data acquisition

- If a signal is to far away from the actual calculated baseline

As the different modes of operation do not always allow to specify the acquisition window before the data is processed the first option is not enough. Furthermore in typical environments it is likely to have physical pulses even if there is no trigger. The second option on the other hand does have a start-up problem, as the initial baseline is not known. To deal with that the baseline thresholds are disabled for a fixed period of 5 time the programmed  $\tau$  to make sure, the baseline being reasonable good calculated.

ALTRO description, not updated

To remove systematic effects, a pattern memory (pedestal memory) is used. If the memory is programmed beforehand with the shape of the systematic perturbation, then the shape can be subtracted from the input signal for each triggered acquisition. Alternatively, the memory can be used as a Look-Up Table (LUT) to perform non-linear conversion or to equalize the response across different channels. As a test feature, this memory can inject a pattern in the processing chain to allow the testing of all the logic downstream without the need of an external analogue signal.

The two aforesaid circuits allow for 3 different modes of operation: subtraction mode, conversion mode and test mode. Some of these modes of operation can be combined allowing numerous configurations of the BC1 circuit. The most relevant configurations have been summarized in table 1.1 while the complete list is reported in table 3.19. Hereafter we describe the main modes of operation.

**Subtraction mode** In this mode of operation, the BC1 performs the subtraction of spurious signals from the input-signal values. The subtracted signal can be fixed (fixed subtraction mode), time-dependent (time-dependent subtraction mode) or self-calibrated (self-calibrated subtraction mode).

**Fixed-subtraction mode** The value to be subtracted from the input signal is constant and stored in a configuration register.

**Time-dependent subtraction mode** The time-dependent pedestal values which are to be subtracted from the incoming signal are stored in a memory (pedestal memory) that, in this configuration,

is addressed by a time counter started by the trigger signal. The 10-bit word values in the memory can be chosen to have an accuracy of 2, 1, 0.5 or 0.25 ADC counts.

**Self-calibrated subtraction mode** The value to be subtracted is computed as cumulative average of a programmable number of samples (n) of the input signal outside the processing time window.

$$Out = ADC - baseline (1.1)$$

ALTRO formula, not updated

$$baseline' = \frac{(2^n - 1) \cdot baseline + ADC}{2^n}$$

(1.2)

While the fixed-mode and time-dependent-mode are exclusive, any of them can be combined with the self-calibrated mode as shown in table 1.1.

Conversion mode The circuit can perform a memory (static) conversion of the input signal of the type  $y_n = F(x_n)$ . At any cycle n, the output  $y_n$  depends at most on the input sample  $x_n$  at the same time, but not on past or future samples of the input. The output values  $y_n$  are stored in the pedestal memory addressed, in this case, by the input values  $x_n$ . The conversion mode can work concurrently to the self-calibrated subtraction mode and to the fixed subtraction mode.

**Test mode** The LUT can be used to generate a pattern to be injected into the processing chain for test purposes. It also supports subtraction a constant value.

Finally, the BC1 circuit provide also the possibility of inverting the input signal polarity (1's complement). The pedestal memory is accessible, in write and read mode.

| Modes of operation |                | Main configurations |            |                 |                  |              |                    |            |

|--------------------|----------------|---------------------|------------|-----------------|------------------|--------------|--------------------|------------|

|                    |                | din - FPD           | din - f(t) | din - VPD - FPD | din - VPD - f(t) | f(din) - FPD | f(din - VPD) - FPD | f(t) - FPD |

|                    | Fixed          | x                   |            | х               |                  | x            | x                  | x          |

| Subtraction mode   | Time-dependent |                     | x          |                 | x                |              |                    |            |

|                    | Variable       |                     |            | x               | x                |              | X                  |            |

| Conversion mode    |                |                     |            |                 |                  | x            | X                  |            |

| Test mode          |                |                     |            |                 |                  |              |                    | x          |

**Table 1.1:** BC1 baseline correction and subtraction modes. Legend: din: data input (samples); f(t): LUT data; FPD: fixed pedestal data value; VPD: variable pedestal data value; f(din): converted data.

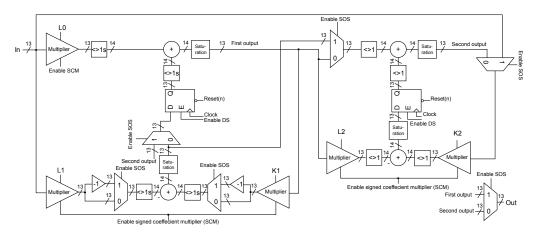

#### 1.4.2 Digital shaper

Merge descriptions

#### **ALTRO** description

The SAMPA can be suited for a wide class of applications. One of its applications is the readout of the cathode pad plane of a conventional multi-wire proportional chamber. In this detector, the necessary signal amplification is provided by an ionization avalanche created in the vicinity of the anode wires. Moving from the anode wire towards the surrounding electrodes, positive ions, created in the avalanche, induce a positive current signal on the pad plane. This current signal is characterized by a fast rise time (less than 1 ns) and a long tail with a rather complex shape, which depend on the details of the wires and pad geometry.

**ALTRO** description, not updated

The signal tail increases the superimposition of subsequent pulses (pile-up) rendering the zero suppression quite inefficient. In order to minimize such effect, the SAMPA incorporates a filter for the cancellation of the signal tail. The algorithm used for the tail cancellation is the same that it was used in ALTRO chip. It is explained hereafter. The signal is approximated by the sum of 4 exponential functions:

$$is(t) = I_0 \times \sum_{i=1}^4 A_i \times e^{-\frac{t}{\alpha \cdot \tau_i}} + r(t) \begin{cases} \tau_1 \ll \tau_2 \ll \tau_3 \ll \tau_4 \\ \sum_{i=1}^4 A_i = 1 \end{cases}$$

(1.3)

Where r(t) is a residual function due to the approximation error. The sum of the gains  $A_i$  should be equal to 1 so that input and output have the same amplitude. The time function equation (1.3) can be expressed in the Z domain as:

$$Is(z) = I_0 \times \sum_{i=1}^{4} \frac{A_i}{1 - exp(\frac{T}{\alpha \cdot \tau_i} \cdot z^{-1})} + R(z)$$

(1.4)

The signal is passed through a linear network that cancels all but the fastest of the exponential terms. The n-1 pole-zero network has a transfer function that expressed in the Z domain is:

$$H(z) = \frac{(1 - exp(\frac{T}{\alpha \cdot \tau_2}) \cdot z^{-1})(1 - exp(\frac{T}{\alpha \cdot \tau_3}) \cdot z^{-1})}{1 - L_1 z^{-1} + L_2 z^{-2} + L_3 z^{-3}})$$

(1.5)

The numerator of F(z) will perfectly cancel all the poles of Is(z) except one. The constants L1, L2 and L3 are chosen such that the numerator of the expanded form of Is(z) disappears. The response of this linear network to the incoming signal is the convolution in the time of the impulse response function of the filter and the signal itself:

$$is(t) * f(t) = I_0 e^{-\frac{t}{\alpha \cdot \tau_0}} + r(t) * f(t)$$

(1.6)

One can easily observe from this expression that the performance of the tail cancellation is strongly related to r(t). The remaining fast exponential is a constraint of the system and can be chosen such that:

$$e^{-\frac{t}{\alpha \cdot \tau_i}} < 0.1\% \qquad t \ge 1\mu s \tag{1.7}$$

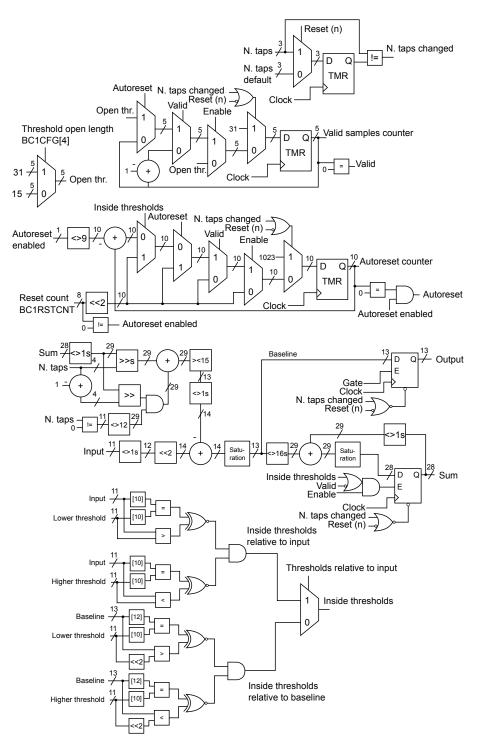

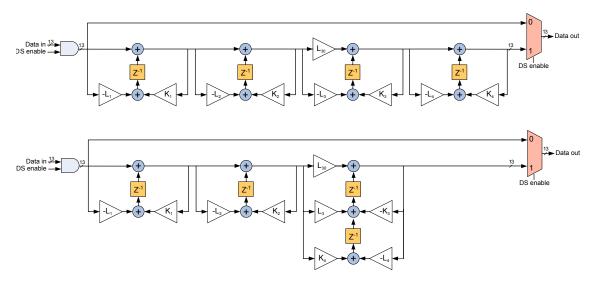

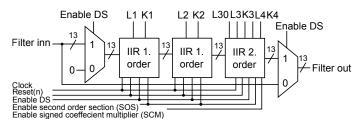

The filter considered is an IIR filter of order 4. The filter is composed of 4 first order filters in cascade, although just 3 first order filters are used in this application. The filter is flexible in the configuration of the digital signal processing operation by changing 8 programmable and accessible coefficients, K1, K2, K3, L1, L2 and L3, for each filter. In this case, K4=L4=0.

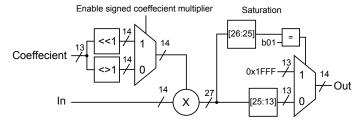

The processing performed is shown in figure 1.5.

#### **S-ALTRO** description

Figure 1.5: Tail cancellation scheme.

There are different architectures possible for the IIR filter. The possibility to implement complex-conjugate poles/zeros (second order) and the advantage of lower sensitivity to quantification error (cascade form) make optimal the cascade combination of two second order filters.

The different architectures for IIR filters have been compared in terms of hardware resources, overflow and errors due to round-off and coefficient quantification. Being the transposed form the optimal architecture in this application, mainly because the overflow in the internal nodes is not a problem for fast impulses in the input.

#### Quantization analysis

When the parameters of the system are quantized, the poles and zeros move to a new position in the z-plane. Obviously, the frequency response is perturbed from its original value. This effect could modify the specifications of the original filter, or an IIR filter might even become unstable. Coefficient quantization errors are more sensitive to high order sections. There are two ways to reduce the order through the transfer functions decomposition in sections of less order: cascade-form and parallel-form. The cascade-form is the less sensitive to coefficient quantization [1??]. These effects were studied via the implementation of the transfer functions of the filters in Matlab. The outputs show that 13bits second order filters in cascade form do not have coefficient quantization effects in the output.

#### Round-off analysis

The simple linear-noise model presented (Figure ??) allows to characterize the noise generated in the system (using Matlab) by averages such as the mean and variance and to determine how these averages are modified by the system.

$$\sigma_{ADC}^2 = \frac{2^{2 \cdot bits}}{12} (V_{max} - V_{min})^2 \tag{1.8}$$

$$\sigma_{er}^2 = \frac{2^{2 \cdot bits}}{12} (V_{max} - V_{min})^2; \qquad \sigma_{ei}^2 = \sum_{i=0}^n \sigma_{er}^2$$

(1.9)

$$\sigma_{y_noise}^2 = \sigma_{ADC}^2 \cdot \sum_{n = -\infty}^{\infty} |h[n]|^2 + \sigma_{ei}^2 \cdot \sum_{n = -\infty}^{\infty} |h_e[n]|^2$$

(1.10)

$$\sigma_x^2 = \frac{1}{12} (V_{max} - V_{min})^2 \tag{1.11}$$

| resolution                       | SNR      |

|----------------------------------|----------|

| ADC (10 bits)                    | 66.22 db |

| ADC (10 bits) + Shaper (10 bits) | 53.99 db |

| ADC (10 bits) + Shaper (11 bits) | 59.30 db |

| ADC (10 bits) + Shaper (12 bits) | 63.25 db |

| ADC (10 bits) + Shaper (13 bits) | 65.27 db |

Table 1.2: Signal to noise ratio of the filter

$$\sigma_y^2 = \sigma_x^2 \cdot \sum_{n = -\infty}^{\infty} |h[n]|^2 \tag{1.12}$$

$$SNR(db) = 10 \cdot \log \left( \frac{\sigma_y^2}{\sigma_{y_n oise}^2} \right)$$

(1.13)

A common objective in round-off analysis is to choose the digital word length such that the digital system is a sufficiently accurate realization of the desired linear system and at the same time requires a minimum of hardware or software complexity. The digital word length can be changed only in steps of 1 bit, the addition of 1 bit to the data-path reduces the size of quantification error analysis by factor of 2. Table ?? shows the signal to noise ratio of the system. Following a commitment between accuracy system and hardware complexity, it is added two extra bits (LBS) in the data path.

#### Overflow analysis

The possibility of overflow is an important consideration in the implementation of IIR systems using fixed-point arithmetic. In this architecture the internal values are calculated from a subtraction of the input and the output value (Figure ??), the internal values does not increase as much as the other architectures. The transposed form is the only configuration with no overflow error for this application.

#### Tail cancellation parameters

The eight parameters for the Digital Shaper can be set individually on each input of the channel in order to maximize its effect. The optimal parameters for the tail cancellation can be found with the following algorithms.

• Mota method (real poles/zeros): in this method is proposed to divide the complex ion tail into its various effects and consider them separately. In order to suppress a given effect, a correction function with an opposite impulse response behavior should be chosen. The parameters are calculated via recursive formulas proposed in [2??]. Next equations show the relation between Mota method

parameters and S-ALTRO parameters.

$$b_{12} = L_2 + L_3 \tag{1.14a}$$

$$b_{13} = L_2 \cdot L_3 \tag{1.14b}$$

$$a_{12} = K_2 + K_3 \tag{1.14c}$$

$$a_{13} = K_2 \cdot K_3 \tag{1.14d}$$

$b_{22}$ ,  $b_{23}$ ,  $a_{22}$ ,  $a_{23}$  can be used for height normalization [2??]

Riegler method (real poles/zeros): this method approximates the input signal by a sum of exponentials. The model function to calculate the parameters is determinate by the convolution of the IRF and the signal [3??] Following equations show the relation between Riegler method parameters and S-ALTRO parameters.

$$b_{12} = e^{-1/\tau_2} + e^{-1/\tau_3} \tag{1.15a}$$

$$b_{22} = e^{-1/\tau_2} \cdot e^{-1/\tau_3} \tag{1.15b}$$

$$a_{12} = e^{-1/\tau_a} + e^{-1/\tau_b} \tag{1.15c}$$

$$a_{22} = e^{-1/\tau_a} \cdot e^{-1/\tau_b} \tag{1.15d}$$

$b_{22}$ ,  $b_{23}$ ,  $a_{22}$ ,  $a_{23}$  can be used for height normalization [3??]

• New method (complex poles/zeros): still it's being studied...

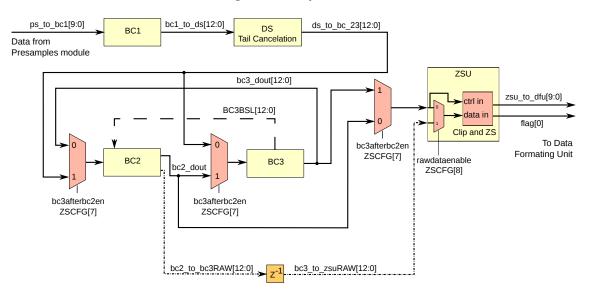

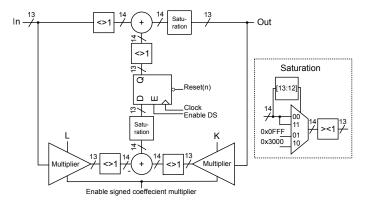

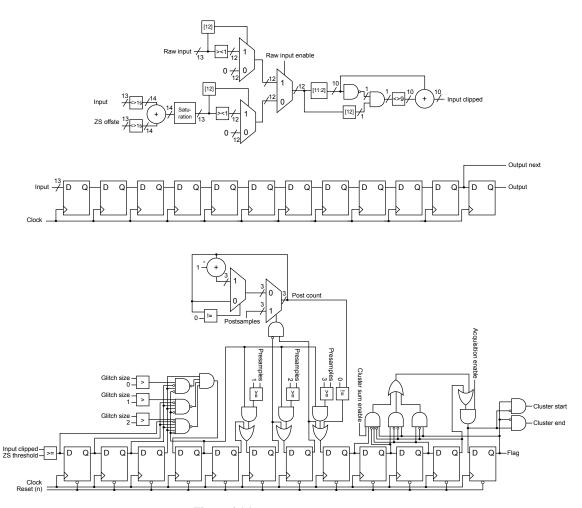

#### 1.4.3 Baseline correction and subtraction II

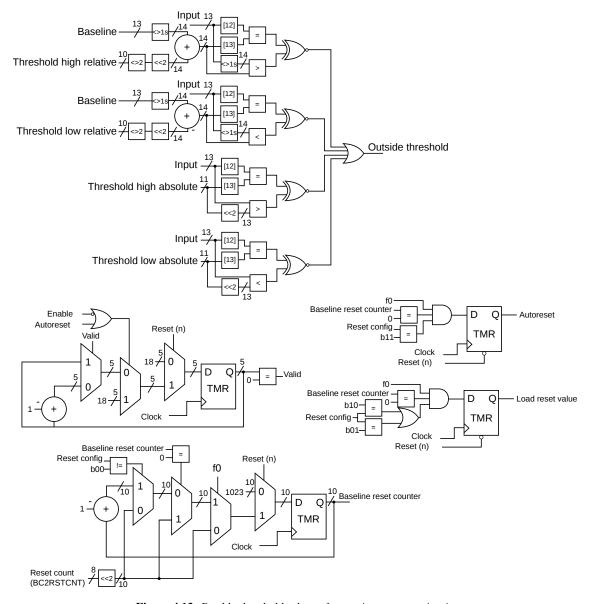

A second level of baseline correction can be applied to the signal to correct for signal perturbations created by non-systematic effects. This level of correction is based on a moving average filter. This functionality is performed in two different levels, one is the generation of the window to perform the average of the baseline (acceptance window), and the other is the correction itself. The correction of the baseline is based on a moving average filter.

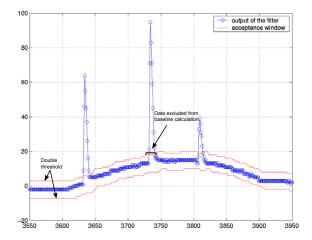

The acceptance window is based on a double threshold scheme, one above and one below, that follows the slow variations of the signal (figure 1.6). Inside the acceptance window, the baseline is updated according to the following equation:

$$y(n) = \frac{1}{M+1} \sum_{k=0}^{M} x(n-k) \qquad M = 1, 3, 5 \text{ or } 7$$

(1.16)

This value is the result of the moving average of a signal x(n). In case all previous values were inside the threshold, then it is the average of this sample and the previous 1, 3, 5 or 7 (depending on the configuration) and the current sample value will be corrected with this value.

When there is a fast variation in the signal, like a pulse, the samples would pass out of the acceptance window, and therefore excluded from the baseline calculation. In this case the value of the samples are

corrected with the value calculated by the moving average filter for the last sample that was inside the window.

**Figure 1.6:** *Moving average principle.*

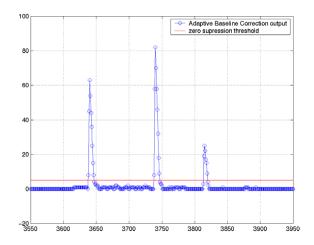

Figure 1.7: Data after adaptive baseline correction.

A setting to additionally exclude a programmable number of samples before and after any pulse that passes out of the exclusion thresholds is available. This could be helpful if the baseline is generally very stable.

To combat some of the problems that were experienced previously with the ALTRO BC2 filter, where the filter was sometimes seen to get stuck outside the threshold ranges, a configurable auto reset feature have been implemented to solve this.

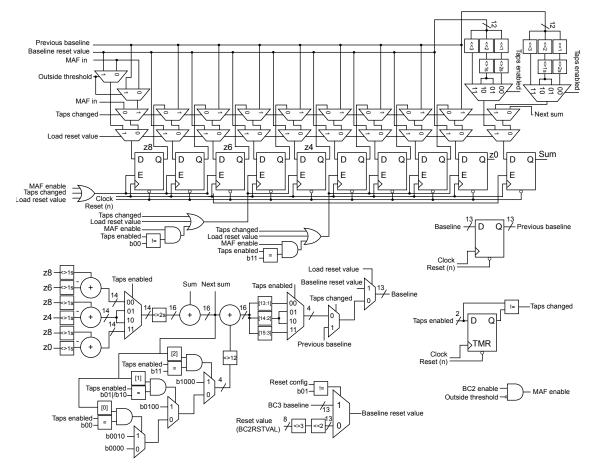

### 1.4.4 Baseline correction III

Conventional linear filters like the BC1 and BC2 have been used in the past in particle detector experiments and are useful for the task, but in some exceptional cases they can end up in a failure mode in where the baseline of the signal shifts to outside the thresholds of the filter and the filter stops to operate.

In general the filter has a max slope that can be handled before it needs to be reset or the thresholds need to be changed.

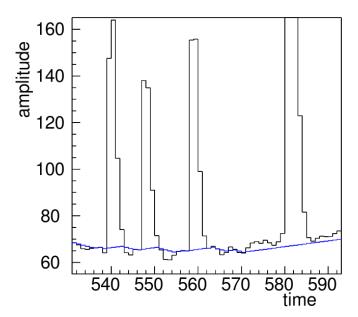

A new nonlinear filter called BC3 has been included which does not have any thresholds. This makes the baseline tracking free of dead areas and the need for fine tuning of configurations. The main idea behind this filter is to always follow the baseline, but with a limited slope configurable per channel. The slope parameter can be set individually for the up and down slope.

The output signal h(t) is expressed as a function of the input f(t) as follow:

$$h(t) = f(t) - g(t)$$

(1.17)

Where g(t) is the tracked slope baseline value and can be expressed as:

$$g(t) = g(t-1) + \begin{cases} slope \uparrow & \text{if } f(t) > g(t-1) \\ 0 & \text{if } f(t) = g(t-1) \\ -slope \downarrow & \text{if } f(t) < g(t-1) \end{cases}$$

(1.18a)

$$g(0) = f(0) \quad \text{(arbitrary)} \tag{1.18b}$$

The filter has also a maximal slope as BC2, but exceeding it causes only a time-limited deviation. As the filter does not have acceptance thresholds it also does not stay constant during an input pulse so the output pulse will be slightly affected.

Figure 1.8 demonstrates the standard behavior of the filter when changes of the baseline and different input pulses are applied.

**Figure 1.8:** *BC3 filtering principle.*

## 1.5 Compression

Even though the SAMPA has enough output data links to handle reading out raw data, it is often not practical or economically feasible to do a raw readout. Different compression methods are provided to reduce the data amount enough so that fewer serial data links can be used. Both lossless and lossy compressions are available, depending on the detectors needs and resources.

**Huffman** This compression method is a lossless compression, ie. no information is lost. It uses differential encoding of the data combined with a lookup table to reduce the length of each word. This method is useful for detectors that want all data, but has limited bandwidth available. Depending on the detector data, it has a compression factor close to or better than zero suppression.

**Zero suppression** This method removes all data below a given threshold, leaving only cluster data. As the data which is in between clusters are lost, it is a lossy encoding. This method is highly dependent on having a stable baseline to achieve good compression and minimal loss of information, so digital signal conditioning might be needed.

**Zero suppression with cluster sum** This method operates on the same principle as zero suppression, but it additionally integrates the sample values in the cluster into one value. This compression method is suitable for detectors that have very clean signals and where only the time for the start of the cluster and the area is of interest.

#### 1.5.1 Huffman compression

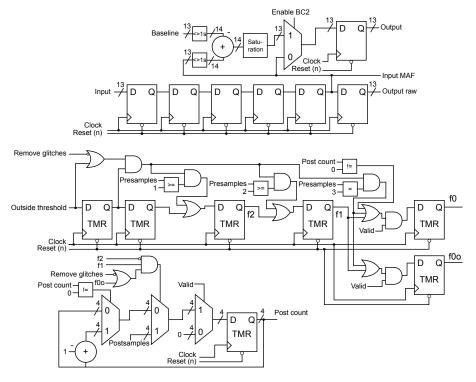

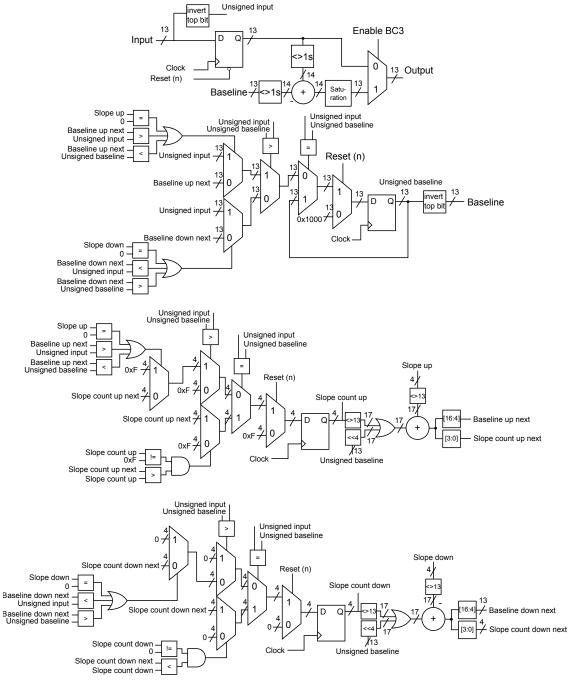

#### 1.5.2 Zero suppression

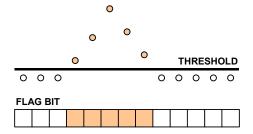

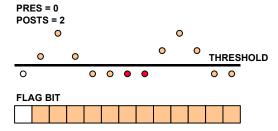

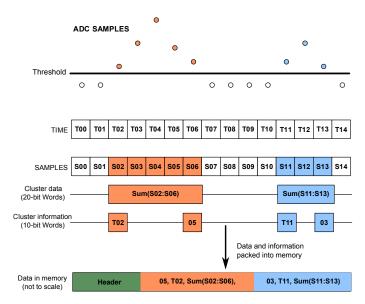

The basic pulse detection scheme is fixed thresholding: samples of value smaller than a constant decision level (threshold) are rejected. When a sample is found above the threshold, it is considered the start of a pulse (figure 1.9).

Figure 1.9: Basic detection scheme.

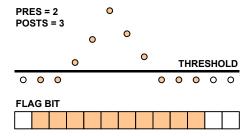

In order to keep enough information for further feature extraction, the complete pulse shape must be recorded. Therefore, a sequence of samples (pre-samples) before the signal overcome the threshold and a sequence of samples (post-samples) after the signal returns below the threshold are also recorded (figure 1.10). The number of presamples and the number of post-samples can vary independently in the range between 0 and 3 for pre-samples and 0 to 7 for post-samples.

**Figure 1.10:** Feature extraction with two extra samples before pulse and three after.

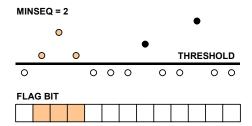

To reduce the impulsive noise sensitivity, a glitch filter checks for a consecutive number of samples above threshold, confirming the existence of a real pulse (figure 1.9). The minimum sequence of samples above the threshold (glitch filter) which defines a pulse can vary from 1 to 3, not including any pre- or post-samples.

**Figure 1.11:** Glitch filtering with minimum samples above threshold of 2. Samples in solid black are treated as if they were below the threshold.

The pulse thus identified and isolated must be tagged with a time stamp, in order to be synchronized with the trigger decision for validation. Otherwise the timing information would be lost by the removal of a variable number of samples between accepted pulses. This requires the addition of a time data to the set of sample data. Besides that, in a data format where the addition of flag bits is not allowed, a further word is needed to distinguish the sample data from the time data. This extra word represents the number of words in the set. Since for each new set of data we have two extra words, the merging of two consecutive sets, which are closer than 3 samples, is performed (figure 1.12).

In case of the cluster sum mode, the data in one cluster is summed together into a 20 bit word and the requirement for the minimum distance between clusters is then changed to 3.

Figure 1.12: Merging of close clusters. Samples in red are included to make one complete cluster.

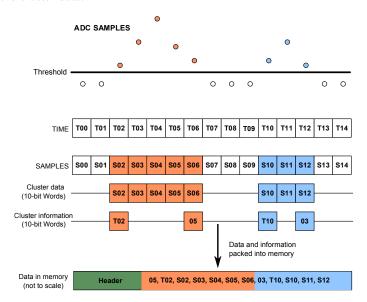

#### 1.5.3 Lossy data compression

Due to the removal of a variable number of samples between accepted clusters in the lossy encodings (zero suppression, cluster sum), the timing information would be lost in the process. This requires the addition of a time-data to each accepted set of samples. Since 1023 is the maximum length of the data stream that can be processed by the SAMPA chip, the time information can be encoded in a 10-bit word. The principle is to label each sample with a time-stamp that defines the time distance from the trigger signal. The time information added to each cluster during the formatting phase corresponds to the time-stamp of the first sample in the cluster.

The SAMPA data format does not make use of extra flag bits to distinguish the samples data from the time-data, but introduces a further word for each accepted cluster, which represents the number of samples in the cluster. In the ALTRO, the cluster size data included also the time information data and cluster information data in the count of the total number of words in the cluster, the SAMPA does not count them into the total.

These new 10-bit words, time data and number of samples per cluster, are introduced at the beginning of the cluster (figure 1.13) in contrast to how it operated in the ALTRO chip where the information words were located after the cluster data.

Figure 1.13: The SAMPA data format for zero suppression encodings.

A header of five 10-bit words (50 bits in total) are inserted at the start of a processing time window, where among other things the total length of the compressed data stream is recorded. See section §2.3.1 for more information on the header format.

**Figure 1.14:** The SAMPA data format for zero suppression encoding with cluster sum. The sum part is 2 words.

## 1.6 Channel ordering

# 1.7 Data formatting unit and Ring buffer

The Data Formatting Unit (DFU) and the Ring buffer are the last two blocks of each channel as shown in figure 2.9. The DFU generates the packet format for serial transmission and the Ring buffer provides a temporary storage for the data and headers.

Figure 1.15: DFU + RB in channel circuit diagram.

### 1.7.1 Data formatting unit (DFU)

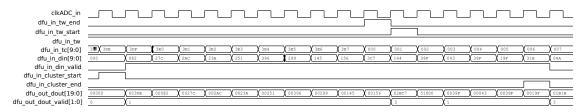

Data arriving from Zero Suppression block or Huffman compressor is analyzed in the DFU block and cluster information as number of samples and timing is inserted for the generation of the payload part of packets for serial transmission (see section §1.5.3). Optionally, payloads can be generated from raw data. It can also generate data compression as the sum of all the cluster samples, denominated cluster sum mode. These options can be configured through VACFG global register.

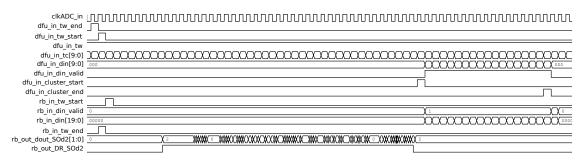

The DFU receives information of start and end of time window (tw\_start and tw\_end) and a time count that is restarted at the beginning of each time window, see figure 1.16. It also receives signals to determine

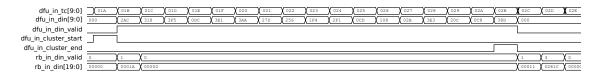

the start and end of each cluster (cluster\_start and cluster\_end). The number of samples of each cluster is counted and transmitted to the Ring buffer along with the value of the last sample in the 20 bits dout signal. The time count of the sample that arrives one cycle early is added at the beginning of the cluster. See these details in figure 1.17.

**Figure 1.16:** Waveforms of time window, cluster and data DFU inputs.

Figure 1.17: Control signals of time window and cluster and data DFU input/output.

If a cluster starts in one time window and ends in the following, for example in continuous mode, at the output it is divided in two clusters as in figure 1.18.

Figure 1.18: Cluster starting in one time window and ending in the next one.

In cluster sum mode, the DFU transmit to the ring buffer the time count of the first sample of the cluster when the cluster starts. When the cluster ends the first word at the output of the DFU is the cluster size, then the sum of values of the samples in the cluster. See figure 1.19 for details.

#### 1.7.2 Ring buffer

The Ring Buffer contains two temporary memories one for payloads, data memory of 10 bits X 6144 words, and another for headers, header memory of 10 bits X 256 words. These memories allow simultaneous reading and writing operations at different rates through two ports in each one. IP memory manufacturing defects can be detected through a built in test block in ring buffer block. Also, if an error occurs in header memory it can be corrected using Hamming code. Two or more errors per header can be detected but not corrected. Being the last block of each channel, it interfaces with the serial output block. As the reading can be slower than the writing of data or headers, memory overflow can occur. For the data memory overflow header packets are generated indicating number of words of payload zero (data truncated

**Figure 1.19:** Waveforms of DFU and Ring Buffer signals in cluster sum mode

packet type). If the header memory overflows the packets are discarded. But in both cases the Ring Buffer recovers and continue to write to and read packets from memory correctly. Empty packets generation and transmission, when there is no any sample value above the zero suppression threshold in a time window, can be configured through the VACFG global register.

The Ring Buffer generates the headers of the packets adding bunch crossing count for event counting, packet type, payload parity information, hardware address, channel address, number of words in the associated payload, hamming code for header error detection and correction and header parity information. For more details about headers see section §2.3.

The data is received from the DFU including time count and cluster size. The tw\_start\_ADC and tw\_end\_ADC signals establish the limits of the time window and they arrive to the ring buffer one cycle later than those for the DFU. The clusters in a time window are included in a payload and the header generated. When a packet is ready to be transmitted, the DR\_SOD2 signal is set to '1'. The figure 1.20 shows details.

Figure 1.20: Waveforms of input/output signals of DFU and Ring Buffer

When in trigger mode if a trigger pulse is received before time window end a trigger too early packet type is generated. At the trg\_overlap input a pulse is generated indicating that this type of packet is to be generated by the Ring buffer. Also, at the end of the time window a new packet is then initiated. A trg\_overlap pulse generation example is in figure 1.21.

Figure 1.21: Waveforms of ring buffer input/output signals when trigger early

### 1.8 Serializing

The SAMPA allows the configuration of the functionality of the 11 data output pins. Configurations are for the standard modes, i.e. modes intended for normal usage, and test modes.

#### 1.8.1 Standard Modes

The SAMPA read-out may be performed in DSP mode or in Direct ADC Serialization mode (DAS mode). When in DSP mode all the processing capabilities of the SAMPA and up to eleven serial links at 80, 160 or 320 Mbps are available. To this mode be enabled the clk\_config[6] and the sme input pins must to be in '0' and the BYPASS global register also in 0x0 (default value). By default the number of enabled serial links is four, but it may be modified through the SOCFG[3:0] global register. See section §2.3 for more details about the serial interface and protocol. In daisy chaining NBflowstop\_out\_SO5 output pin is used to halt the transmission of data from an upstream device. See section §2.4. This is its default functionality. However, it can be used as the fifth serial link when enabling six or more links through SOCFG[3:0].

When in Direct ADC Serialization mode, the samples of the 32 ADCs and the end of conversion signal are multiplexed to the 11 data output pins and sequentially transmitted at the serial output clock frequency. To enable the DAS mode the clk\_config[6] and the trigger pin (trg) must be in '1' and the heartbeat trigger (hb\_trg) input pin must be in '0'. The BYPASS global register must also be in 0x0 (default value). See section §2.5 and section §4.15.

#### 1.8.2 Test Modes

The 11 data outputs, SerialOut[4:0], NBflowstop\_out\_SO5 and sdo[4:0], may also be set to work in ADC combo data mode for testing with clk\_config[6] and hb\_trg in '1'. In this mode, the output data and the end of conversion of a selected ADC is directly connected to the output pins. The ADC selection is performed using the sme and the hardware address (hadd) input pins.

The SerialOut[0] output may be used for internal memory test indicating errors through pulses. This mode is enabled setting the input pin sme. SerialOut[0] may also be configured to bypass one of 14 signals according to the BYPASS global register. See table 3.13 for specifics.

Other test functionality is the bypass in daisy chaining. In this case NBflowstop\_out\_SO5 output pin is NBflowstop\_in enabled through BYPASS and SOCFG[5] registers.

# 1.9 Event managing

SAMPA supports two read-out modes: continuous mode and external triggered. In continuous mode a new time window is started when the previous one has ended. The length of the time window can be set up to 1024 samples long. In triggered mode, upon reception of the external trigger, a new time window is started. At the end of the time window, the SAMPA will go back to being idle until the next trigger arrives. The trigger is sent either via an external pin with a maximum latency of 192 times the sample rate. All 32

channels of the SAMPA uses the same time frame. If an external trigger signal is received in continuous mode, the current time window is ended and a new one is started immediately without loss of information. In this way it is possible to align the time frames across different SAMPA chips.

Normally there will be sent a packet containing a header and the compressed data pertaining to the completed time window, one packet per channel, each time a time window is completed. Though an option is available to disable sending of packets that contain no data, where there was no data above the zero suppression threshold.

The SAMPA has an internal 20 bit counter, that runs on the LHC 40 MHz clock, called the bunch crossing counter. At the start of each new time window the value of this counter is captured and added to the header of the packet for that time window as a bunch crossing id. If the ADC sampling clock is derived from the same source clock as the 40 MHz clock it is possible to use this value as an event number id by calculating:

$$event num = \frac{bx counter}{time window length \cdot \frac{40MHz}{F_s}}$$

(1.19)

On reception of a bunch crossing sync trigger the SAMPA will reset the counter. In this way it is possible to align the bunch crossing id across different SAMPA chips.

If the 40 MHz or the ADC sampling clock is set up to be internally derived from another clock, then the phase difference between these clocks for one SAMPA versus another might not be the same after a cold start. This would present it self as differences in a few counts of the bunch crossing id for devices that are synchronously triggered. To synchronize the internal clocks the devices need to be also reset at the same time or the reset signal must be applied to one device so that it lines up with the others.

For off-site synchronization the SAMPA provides the generation of a specially crafted heart beat packet once a heart beat trigger signal is provided. The packet contains among other things the bunch crossing ID when the trigger arrived and the chip address.

# 1.10 Daisy chaining

To simplify wiring and for detectors with very low data rates a daisy chaining option has been implemented which lets multiple SAMPAs share a single serial link. Each SAMPA uses a data input port, a data output port and busy in and busy out signals. When a device receives a busy signal from a device downstream it will pause its transmission until the downstream device is ready for receiving data again.

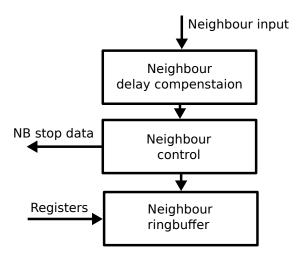

#### 1.10.1 Neighbor module

The serial link of the device upstream (neighbor) is connected to the dinN input pin of the device that shares the single serial link (master). The packets arriving at the master are then received by the neighbor block. This module is composed by three main sub blocks as seen in figure 1.22.

The delay compensation block is to avoid metastability caused by the same serial output frequency of neighbor and master devices. A delay can be set through the NBCFG[5:0] global register. This register also allows the configuration of device priorities. See 3.1.6 for more details. The delayed input signal is also

Figure 1.22: Neighbor block diagram.

available at the output of the neighbor block for the bypass option at the serial output block for testing.

After the delay is applied to the input signal, the hamming code of headers is decoded and the header can be corrected. If the header is not correctable then the packet is discarded.

The received packets are then stored in the neighbor ring buffer block using a data memory of 2 KW and a header memory of 256 W. To avoid the loss of packets due to memory overflow, the neighbor control generates a NBflowStop\_SO5 signal to the upstream device to halt packet transmission. The internal signal h\_full indicates that the arriving of a new packet can produce header memory overflow. Similarly, the d\_full is an indication that the arriving of a new packet can produce data memory overflow. The activation of any of these signals activates the NBflowStop\_SO5 and the neighbor SAMPA waits the NBflowStop\_SO5 deactivation to transmit a new packet. In the example of the figure 1.22 the data is received by the dinN input. When the data memory is full the d\_full signal is activated and then the NBflowStop\_SO5 signal, when the current packet is finished, at dinN sync packets are received until NBflowStop\_SO5 is deactivated and a new packet transmission is initiated.

Figure 1.23: Neighbor block diagram.

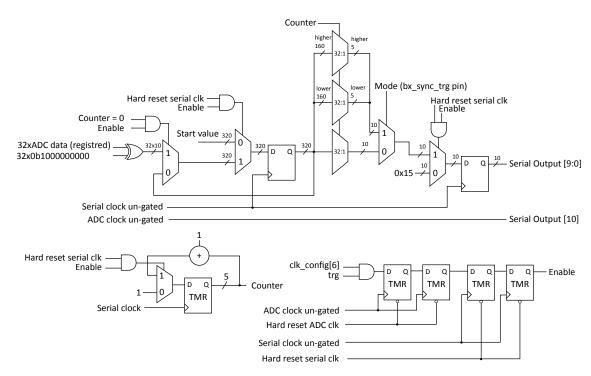

### 1.11 Direct ADC serialization mode

For detectors that would not prefer to use the data handling capabilities of the SAMPA, a mode is available where the raw ADC samples are directly serialized and the rest of the digital circuitry is powered down. This mode operates with a serialization speed of 32 times the ADC sampling speed. Two data transmission modes are available:

**Normal mode** The 10 bit data for channel 0 will be put on the serial link 9-0 in the first cycle, in the consecutive cycle the data for channel 1 will be put out and so on.

**Split mode** The serial link 4-0 will be used by channel 0-15 and link 5-9 will be used by channel 16-31. In the first cycle the 5 lower bits for channel 0 will go on link 4-0 and the 5 lower bits for channel 16 will go on link 9-4. On the consecutive cycle the 5 upper bits for channel 0 will go on link 4-0 and the 5 upper bits for channel 16 will go on link 9-4 and so on. This mode enables the data for channel 0-15 and 16-31 to be sent to two different upstream receivers.

A 32 cycle sync pattern is provided for synchronization to the stream when the direct ADC serialization mode is enabled. To be able to monitor for phase shifts in the ADC clock caused by single event upsets in the internal clock divider one can monitor the 11th serial link which provides the internally generated clock directly outputted.

# Chapter 2

# **Interfaces and protocols**

This section describes the protocols and properties of the various interfaces for the SAMPA.

# 2.1 Analog front-end

The analog front-end can be configured to operate at two shaping time settings controlled by the CTS pin, three sensitivity settings controlled by the CG[1:0] pins and positive/negative input charge polarity controlled by the POL pin. Table 2.1 summarize the possible configurations.

| Polarity | POL  |

|----------|------|

| Positive | low  |

| Negative | high |

|          |      |

<sup>(</sup>a) Pulse polarity configuration

| Gain     | Shaping time | CTS   | CG0  | CG1  |

|----------|--------------|-------|------|------|

| 30 mV/fC | 160 ns       | low   | high | high |

| 20 mV/fC | 160 ns       | low   | low  | high |

| 4 mV/fC  | 300 ns       | high  | low  | low  |

|          | Unsupported  | modes |      |      |

| 9 mV/fC  | 160 ns       | low   | low  | low  |

| 33 mV/fC | 160 ns       | low   | high | low  |

| 16 mV/fC | 300 ns       | high  | low  | high |

| 11 mV/fC | 300 ns       | high  | high | low  |

| 17 mV/fC | 300 ns       | high  | high | high |

|          |              |       |      |      |

(b) Gain and shaping time configuration

Table 2.1: Analog Front-end configurations

### 2.2 Slow Control

The slow control of the SAMPA is done with I2C. Pin positioning is given in table 2.2.

The protocol follows the I2C standard [1] and uses the 10-bit addressing scheme and address increment on continued read/write operations. It can operate from 100 kHz to 5 MHz. A watchdog is implemented that

| Pin 1 | Name | Dir | Type                             | Description |

|-------|------|-----|----------------------------------|-------------|

| D21   | SDA  | I/O | LVCMOS (1.2 V)<br>LVCMOS (1.2 V) | I2C data    |

**Table 2.2:** *Slow control interface pins.*

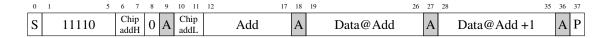

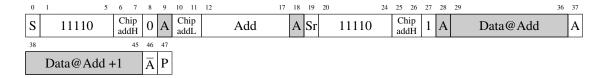

will time out if the time between two falling edges of SCL is more than 512 BX clock cycles (generally  $12.5\,\mu s$ ). Clock stretching is not in use. The protocol is shown in table 2.1 and table 2.2 with the description in table 2.3. Boxes marked in gray are bits sent by the SAMPA.

Figure 2.1: Format for writing to the SAMPA.

Figure 2.2: Format for reading from to the SAMPA.

| Name           | Bits | Description                                  |

|----------------|------|----------------------------------------------|

| S              | 1    | I2C start                                    |

| Sr             | 1    | I2C start repeat                             |

| A              | 1    | I2C acknowledge                              |

| $\overline{A}$ | 1    | I2C not acknowledge                          |

| P              | 1    | I2C stop                                     |

| 11110          | 5    | Fixed preamble address for 10 bit addressing |

| Chip addH      | 2    | Chip address [3:2]                           |

| Chip addL      | 2    | Chip address [1:0]                           |

| Add            | 6    | Register address                             |

| Data           | 8    | Register data to be read/written             |

**Table 2.3:** Protocol bit field descriptions of I2C.

## 2.3 Serial interface

The SAMPA is equipped with eleven SLVS [2] serial links clocked in relation to the serial clock provided by the interfacing device. The relevant pins for the serial interface is shown in table 2.4.

| Pin  | Name                | Dir | Type | Description      |

|------|---------------------|-----|------|------------------|

| L19  | SerialOut+[0]       | О   | SLVS | Serial link 0 p  |

| L18  | SerialOut-[0]       | О   | SLVS | Serial link 0 n  |

| M22  | SerialOut+[1]       | 0   | SLVS | Serial link 1 p  |

| M21  | SerialOut-[1]       | 0   | SLVS | Serial link 1 n  |

| K22  | SerialOut+[2]       | 0   | SLVS | Serial link 2 p  |

| K21  | SerialOut-[2]       | 0   | SLVS | Serial link 2 n  |

| H22  | SerialOut+[3]       | 0   | SLVS | Serial link 3 p  |

| H21  | SerialOut-[3]       | 0   | SLVS | Serial link 3 n  |

| J19  | SerialOut+[4]       | 0   | SLVS | Serial link 4 p  |

| J18  | SerialOut-[4]       | 0   | SLVS | Serial link 4 n  |

| G19  | NBflowstop_out_SO5+ | 0   | SLVS | Serial link 5 p  |

| G18  | NBflowstop_out_SO5- | 0   | SLVS | Serial link 5 n  |

| C22  | sdo+[0]             | 0   | SLVS | Serial link 6 p  |

| C21  | sdo-[0]             | 0   | SLVS | Serial link 6 n  |

| Y22  | sdo+[1]             | 0   | SLVS | Serial link 7 p  |

| Y21  | sdo-[1]             | 0   | SLVS | Serial link 7 n  |

| B22  | sdo+[2]             | 0   | SLVS | Serial link 8 p  |

| B21  | sdo-[2]             | 0   | SLVS | Serial link 8 n  |

| AB20 | sdo+[3]             | 0   | SLVS | Serial link 9 p  |

| AA20 | sdo-[3]             | 0   | SLVS | Serial link 9 n  |

| B20  | sdo+[4]             | 0   | SLVS | Serial link 10 p |

| A20  | sdo-[4]             | О   | SLVS | Serial link 10 n |

Table 2.4: Serial interface pins.

### 2.3.1 Protocol

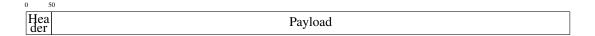

The data sent from the SAMPA consists of a fixed length header and a variable length data payload. The combined header and payload is here on referred to as a packet. The data is written LSB first on rising edge of the clock. The data payload contains zero suppressed and run length encoded samples in a forward linked list in a similar way as for the previous ALTRO chip, though the ALTRO uses a back linked list instead.

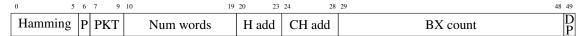

Figure 2.3: Format of serial data header.

Figure 2.4: Format of serial data. Length of payload is variable and given in the header information.

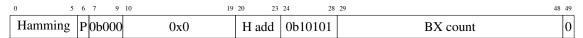

### 2.3.2 Heartbeat packet

Heartbeat packets are specially crafted packets that have the same format as a header (50 bits) with the packet type marked as heartbeat type. They are initiated by a single pulse on the heartbeat trigger pin

| Name      | Bits | Description                              |

|-----------|------|------------------------------------------|

| Hamming   | 6    | Hamming code                             |

| P         | 1    | Parity (odd) of header including hamming |

| PKT       | 3    | Packet type, see table 2.6               |

| Num words | 10   | Number of 10 bit words in data payload   |

| H add     | 4    | Hardware address of chip                 |

| CH add    | 5    | Channel address                          |

| BX count  | 20   | Bunch-crossing counter (40MHz counter)   |

| DP        | 1    | Parity (odd) of data payload             |

Table 2.5: Protocol bit field descriptions of data sent from the SAMPA.

| Data | 1024<br>words | 1025<br>words | Heartbeat | Sync | Trigger<br>too early | Data truncated | Num<br>words [0] | PKT [2] | PKT [1] | PKT [0] |

|------|---------------|---------------|-----------|------|----------------------|----------------|------------------|---------|---------|---------|

| X    |               |               |           |      |                      |                | 0                | 1       | 0       | 0       |

| X    | X             |               |           |      |                      |                | 0                | 1       | 0       | 1       |

| X    |               | X             |           |      |                      |                | 1                | 1       | 0       | 1       |

| X    |               |               |           |      | X                    |                | 0                | 1       | 1       | 0       |

| X    | X             |               |           |      | X                    |                | 0                | 1       | 1       | 1       |

| X    |               | X             |           |      | X                    |                | 1                | 1       | 1       | 1       |

|      |               |               | X         |      |                      |                | 0                | 0       | 0       | 0       |

| X    |               |               |           |      |                      | X              | 0                | 0       | 0       | 1       |

|      |               |               |           | X    |                      |                | 0                | 0       | 1       | 0       |

| X    |               |               |           |      | X                    | X              | 0                | 0       | 1       | 1       |

**Table 2.6:** Packet type coding (PKT).

(hb\_trg) and the bunch crossing counter is saved the moment the trigger is detected.

The heartbeat packets are only sent on serial link 0 and has the highest priority, it will be sent after the transmission of the current packet has been completed.

Figure 2.5: Format of heartbeat packet.

#### Heartbeat trigger

This is the trigger signal for the heartbeat packet. It is sampled on the rising edge of the 40 MHz bunch crossing clock. See section §2.8

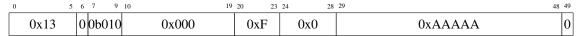

### 2.3.3 Sync packet

A sync packet is a specially crafted packet that has the same general format as a header (50 bits), but with the packet type marked as sync type and the other fields having a fixed value independent of the state of the chip. As the sync packets have a fixed pattern it is possible for the receiving system to use the pattern to synchronize against the incoming data stream. Sync packets are transmitted, to keep the link active, whenever there is no data available in the channel buffers to send.

It is possible to force the transmission of a sync packet by sending a command through the slow control, this will create a sync packet with a higher priority than the channel packets so the sync would be sent after the current channel packet is sent on all links. Two consecutive sync packets are always sent in this case.

Figure 2.6: Format of sync packet.

### 2.3.4 Types of packets

The packet type codes are in table 2.6. They are classified as:

**data**: [Num words [0], PKT] = 0x4. Data packets are those that contain input signal information. Empty packets are also considered as data type. The number of words of the payload is zero in empty packets, and they are generated when there are no pulses above the zero suppression threshold. No other kind of singularity is notified in this type of packet.

**payload of 1024 words**: [Num words [0], PKT] = 0x5. It is a particular type of packet whose payload is of 1024 words.

**payload of 1024 words and trigger early**: [Num words [0], PKT] = 0x7. It is a particular type of packet whose payload is of 1024 words, and its time window was generated by a trigger pulse that arrived before the previous time window had finished.

**payload of 1025 words**: [Num words [0], PKT] = 0xD. It is a particular type of packet whose payload is of 1025 words.

**payload of 1025 words and trigger early**: [Num words [0], PKT] = 0xF. It is a particular type of packet whose payload is of 1025 words, and its time window was generated by a trigger pulse that arrived before the previous time window had finished.

data packet and trigger early: [Num words [0], PKT] = 0x6. It is a normal data type packet, and its time window was generated by a trigger pulse that arrived before the previous time window had finished.

**heartbeat**: [Num words [0], PKT] = 0x0. It is a heartbeat type packet. That is a packet that indicates that the SAMPA chip responds correctly.

**data truncated**: [Num words [0], PKT] = 0x1. It is a data type packet without payload due to the data memory overflow in ring buffer.

**sync**: [Num words [0], PKT] = 0x2. It is a sync packet. It is a packet for the receiver synchronization.

data truncated and trigger early: [Num words [0], PKT] = 0x3. It is a data type packet without payload due to the data memory overflow in ring buffer and its time window was generated by a trigger pulse that arrived before the previous time window had finished.

## 2.4 Daisy chaining

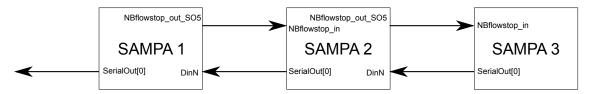

To adapt the SAMPA for detectors with very low data rates a daisy chaining option has been implemented which lets multiple SAMPAs share a single serial link. Each SAMPA has a data input port (DinN) and two data-control signals for this purpose. A connection diagram can be seen in figure 2.7.

The upstream device is set up to run with one serial downlink and the Nbflowstop\_out\_SO5 signal from the downstream device is connected to the Nbflowstop\_in of the upstream device. The NBflowstop signals acts as a busy signal and tells the upstream device to halt its transmission of data after the current packet is done. While waiting to send data again the upstream device will send sync packets to keep the communication in sync.

The downstream device has the serial out of the upstream device connected to its DinN connection. Sync packets arriving on the link will be filtered and only heartbeat and data packets will be retransmitted. The downstream device selects to send packets from either internally or from the upstream link in an equally shared fashion, depending on how many devices in total there are upstream. The Nbflowstop\_in signal of the last device downstream in the chain should be tied low.

In the circuit diagram of figure 2.8 two SAMPAS are interconnected and their inputs are specified. The diagram illustrates an example of daisy chaining mode for clkSO of 80MHz, clkBX and clkADC internally generated and ADC sampling rate of 10 MSPS. The master SAMPA hardware address is configured as 0x1 and the neighbor SAMPA as 0x0. The polarity is configured as positive and the gain and peaking time as 4 mV/fC and 300ns. These inputs can be configured for different values if required.

| Pin | Name                | Dir | Type | Description                                |

|-----|---------------------|-----|------|--------------------------------------------|

| G19 | Nbflowstop_out_SO5+ | 0   | SLVS | Data flow-stop signal to upstream device p |

| G18 | Nbflowstop_out_SO5- | 0   | SLVS | Data flow-stop signal to upstream device n |

| E19 | Nbflowstop_in+      | I   | SLVS | Data flow-stop signal p                    |

| E18 | Nbflowstop_in-      | I   | SLVS | Data flow-stop signal n                    |

| F22 | DinN+               | I   | SLVS | Data from upstream device p                |

| F21 | DinN-               | I   | SLVS | Data from upstream device n                |

| L19 | serialOut0+         | 0   | SLVS | Data output p                              |

| L18 | serialOut0-         | О   | SLVS | Data output n                              |

Table 2.7: Pin list for daisy chaining.

**Figure 2.7:** *Connection setup for daisy chaining.*

**Figure 2.8:** Circuit diagram of a Daisy Chaining mode example.

### 2.5 Direct ADC serialization

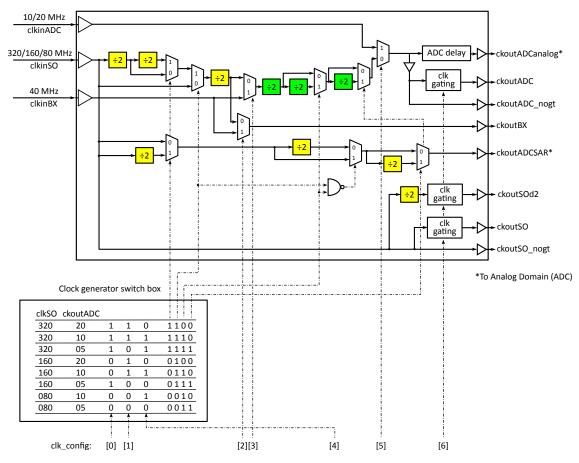

Direct ADC serialization mode enables serialization of raw ADC samples directly while the rest of the digital circuitry is shut down. The mode only functions properly with the serial clock being 32 times the ADC clock, so the valid settings of clk\_config are only those in table 2.8. Running with an external ADC clock is not recommended as the serial link clock and ADC clock need to be synchronous.

| clk_config | external clkSO (MHz) | clkADC (MHz) |

|------------|----------------------|--------------|

| 1000001    | 160                  | 5            |

| 1010011    | 320                  | 10           |

**Table 2.8:** clk\_config settings in DAS mode.

| Pin  | Name                | Dir | Type           | Description                        |

|------|---------------------|-----|----------------|------------------------------------|

| L19  | SerialOut+[0]       | 0   | SLVS           | Serial link 0 p                    |

| L18  | SerialOut-[0]       | 0   | SLVS           | Serial link 0 n                    |

| M22  | SerialOut+[1]       | О   | SLVS           | Serial link 1 p                    |

| M21  | SerialOut-[1]       | 0   | SLVS           | Serial link 1 n                    |

| K22  | SerialOut+[2]       | 0   | SLVS           | Serial link 2 p                    |

| K21  | SerialOut-[2]       | 0   | SLVS           | Serial link 2 n                    |

| H22  | SerialOut+[3]       | 0   | SLVS           | Serial link 3 p                    |

| H21  | SerialOut-[3]       | 0   | SLVS           | Serial link 3 n                    |

| J19  | SerialOut+[4]       | 0   | SLVS           | Serial link 4 p                    |

| J18  | SerialOut-[4]       | 0   | SLVS           | Serial link 4 n                    |

| G19  | NBflowstop_out_SO5+ | 0   | SLVS           | Serial link 5 p                    |

| G18  | NBflowstop_out_SO5- | 0   | SLVS           | Serial link 5 n                    |

| C22  | sdo+[0]             | 0   | SLVS           | Serial link 6 p                    |

| C21  | sdo-[0]             | 0   | SLVS           | Serial link 6 n                    |

| Y22  | sdo+[1]             | 0   | SLVS           | Serial link 7 p                    |

| Y21  | sdo-[1]             | 0   | SLVS           | Serial link 7 n                    |

| B22  | sdo+[2]             | 0   | SLVS           | Serial link 8 p                    |

| B21  | sdo-[2]             | 0   | SLVS           | Serial link 8 n                    |

| AB20 | sdo+[3]             | 0   | SLVS           | Serial link 9 p                    |

| AA20 | sdo-[3]             | О   | SLVS           | Serial link 9 n                    |

| B20  | sdo+[4]             | 0   | SLVS           | Serial link 10 p                   |

| A20  | sdo-[4]             | 0   | SLVS           | Serial link 10 n                   |

| T22  | trg+                | I   | SLVS           | Serialization enable p             |

| T21  | trg-                | I   | SLVS           | Serialization enable n             |

| W19  | bx_sync_trg+        | I   | SLVS           | Serialization mode p               |

| W18  | bx_sync_trg-        | I   | SLVS           | Serialization mode n               |

| B14  | clk_config[6]       | I   | Static (1.2 V) | Clock configuration bit for gating |

Table 2.9: Pin list for direct ADC serialization.

Setting bx\_sync\_trg to '1' enables the split output mode where ch 0-15 is on link 0-4 and ch 16-31 is on link 5-9 with low nibble first and high nibble second. Setting it to '0' will make it send the 10 bits of ch 0-31 consecutively.

Set trg to '0' disables output, set it to '1' to start the serialization up with the sync sequence first. To avoid the SAMPA chip entering in bypass test mode the hb\_trg pin must be set to '0'. The sync pattern is a

32 cycle long pattern that switches between the two complimentary values 0x2B5 and 0x14A. If we define 0x2B5 as 0 and 0x14A as 1 the pattern observed on the serial links [9:0] per serial link clock cycle in the non-split mode would be

0101010100110011010101010100110011

and for the split mode it would be slightly different

001100110011001100001111100001111

as we then only send 5 bits per channel per cycle. De-interleaving the sync pattern in the split mode will give the same data as the non-split mode.

The 11th link is the direct output of the ADC clock from the internal clock divider and should be used for monitoring that the SAMPAs are in sync and that no upsets occur in the clock division, which would present itself as a phase shift. Upset detection could be done by counting the number of high cycles and the number of low cycles and then if they differ then do a reset of the SAMPA. The relationship between the clock on the 11th link and the data is not guaranteed so it should not be used as a marker for a specific channel in the stream.

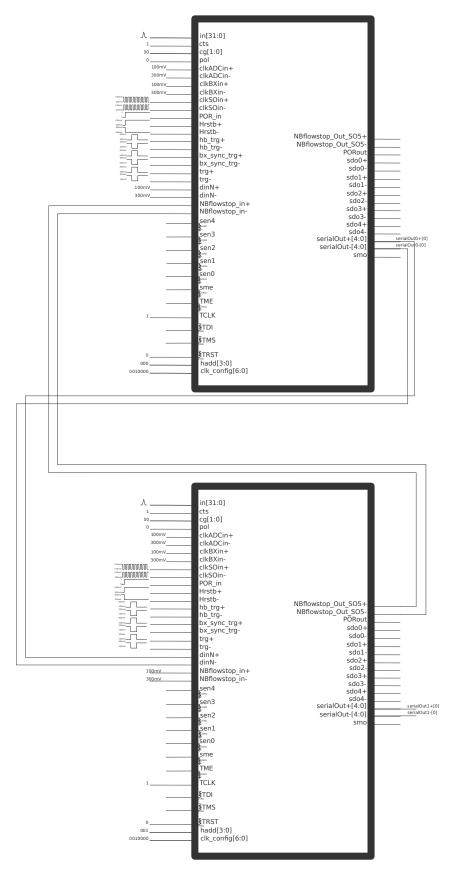

The circuit diagram of figure 2.9 illustrates SAMPA's inputs and outputs signals in DAS mode. In the example, the clkSO is configured for 160MHz, clkBX and clkADC internally generated and the ADC sampling rate is configured for 5 MSPS. The SAMPA hardware address is configured as 0x0. The polarity is configured as negative and the gain and peaking time as 20 mV/fC and 160ns. The output mode is set to normal trough bx\_sync\_trg in '0'. These inputs can be configured for different values if required.

### 2.6 Test interfaces

Various test interfaces are available to ease both functional and production testing of the SAMPA.

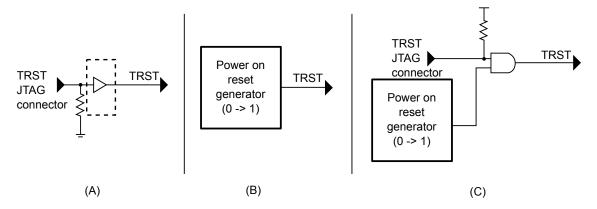

### 2.6.1 JTAG

SAMPA supports boundaryscan according to IEEE/ANSI Standard 1149.1-2001[3]. It is intended for testing the connectivity between digital inputs/outputs in the chip and on the board.

| Pin  | Name | Dir | Туре           | Function                |  |  |

|------|------|-----|----------------|-------------------------|--|--|

| AA17 | TDI  | I   | LVCMOS (1.2 V) | Test Data In            |  |  |

| AB16 | TMS  | I   | LVCMOS (1.2 V) | Test Mode Select        |  |  |

| AB17 | TCLK | I   | LVCMOS (1.2 V) | Test Clock              |  |  |

| AA16 | TRST | I   | LVCMOS (1.2 V) | Test Reset (active low) |  |  |

| AA18 | TDO  | О   | LVCMOS (1.2 V) | Test Data Out           |  |  |

Table 2.10: JTAG test interface pins.

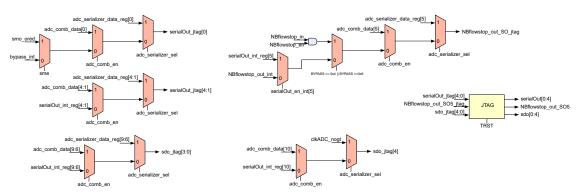

Figure 2.9: Circuit diagram of a DAS mode example.

#### JTAG instructions

The SAMPA has an 3 bit instruction register and supports the mandatory four instructions BYPASS, SAMPLE, PRELOAD and EXTEST.

| Instruction | Name           | DR Length | Function                                             |

|-------------|----------------|-----------|------------------------------------------------------|

| 0b000       | NA             | 1         | Unused (defaults to BYPASS)                          |

| 0b001       | NOP            | 1         | No operation (defaults to BYPASS, reset instruction) |

| 0b010       | NA             | 1         | Unused (defaults to BYPASS)                          |

| 0b011       | NA             | 1         | Unused (defaults to BYPASS)                          |

| 0b100       | INTEST         | 1         | Internal test (not implemented, defaults to BYPASS)  |

| 0b101       | SAMPLE/PRELOAD | 44        | Sample and Preload, inputs and outputs can be read   |

| 0b110       | EXTEST         | 44        | External test, outputs can be controlled             |

| 0b111       | BYPASS         | 1         | Data register bypassed                               |

**Table 2.11:** *JTAG instruction operation codes.*

**BYPASS** This instruction puts a 1bit register between TDI and TDO. It is used for shortening the shift path through a component to avoid having to clock the data to the next device through the full data register of the current device.

**SAMPLE** Reads pin values into the boundary scan register. Used for verifying board connection for input pins. Combined with PRELOAD instruction.

PRELOAD Loads pin values into the boundary scan register that will later be used for EXTEST.

**EXTEST** Set pins with value loaded with PRELOAD. Used for verifying board connection for output pins.

#### JTAG boundary register

The boundary register contains the registers that are connected to each input and output pin and it is placed between TDI and TDO in the SAMPLE/PRELOAD or EXTEST mode. In SAMPLE/PRELOAD the values that were present on input pins and output pins can be clocked out, additionally the value that should be loaded in EXTEST mode can be clocked in. Since the SAMPA has a shutdown feature for unused differential outputs it is required to set bit 0 to 1 to enable all output drivers before entering the EXTEST mode.

| Bit position | Pin                | Function                                     |

|--------------|--------------------|----------------------------------------------|

| 37           | clkADCin           | Observe only input                           |

| 36           | clkBXin            | Observe only input                           |

| 35           | clkSOin            | Observe only input                           |

| 34           | Hrstb              | Observe only input                           |

| 33           | bx_sync_trg        | Observe only input                           |

| 32           | trg                | Observe only input                           |

| 31           | hb_trg             | Observe only input                           |

| 30           | hadd[3]            | Observe only input                           |

| 29           | hadd[2]            | Observe only input                           |

| 28           | hadd[1]            | Observe only input                           |

| 27           | hadd[0]            | Observe only input                           |

| 26           | clk_config[6]      | Observe only input                           |

| 25           | clk_config[5]      | Observe only input                           |

| 24           | clk_config[4]      | Observe only input                           |

| 23           | clk_config[3]      | Observe only input                           |

| 22           | clk_config[2]      | Observe only input                           |

| 21           | clk_config[1]      | Observe only input                           |

| 20           | clk_config[0]      | Observe only input                           |

| 19           | sda_i              | Observe only input                           |

| 18           | scl                | Observe only input                           |

| 17           | dinN               | Observe only input                           |

| 16           | NBflowstop_in      | Observe only input                           |

| 15           | sme                | Observe only input                           |

| 14           | PORin              | Observe only input                           |

| 13           | sda_o              | Output (High-Z, 0)                           |

| 12           | NBflowstop_out_SO5 | Output with output enable at bit 0           |

| 11           | serialOut[4]       | Output with output enable at bit 0           |

| 10           | serialOut[3]       | Output with output enable at bit 0           |

| 9            | serialOut[2]       | Output with output enable at bit 0           |

| 8            | serialOut[1]       | Output with output enable at bit 0           |

| 7            | serialOut[0]       | Output with output enable at bit 0           |

| 6            | sdo4               | Output with output enable at bit 0           |

| 5            | sdo3               | Output with output enable at bit 0           |

| 4            | sdo2               | Output with output enable at bit 0           |

| 3            | sdo1               | Output with output enable at bit 0           |

| 2            | sdo0               | Output with output enable at bit 0           |

| 1            | smo                | Output with output enable at bit 0           |

| 0            | -                  | Control for outputs at bit 1-12 (active high |

Table 2.12: JTAG boundary register.

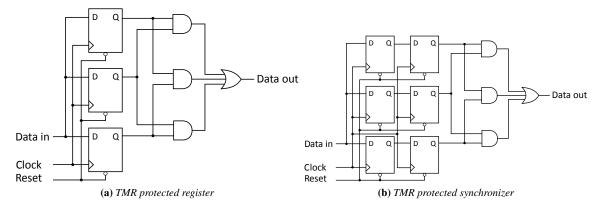

#### 2.6.2 Scanchain

The SAMPA has all flipflops (except memory IPs) wired up in 5 scan chains four of them of 24595 flip flops and one of 24596 flip flops. As some of the flip flops in the design is used with a negative output then

there will also be inversions of a signal that travels through the chain. The sen pins enable its corresponding scan chains, while TME enables various override modes internally that is needed for running the scan chain reliably. The sdo pins act as serial output pins in normal operation mode and are therefore differential.

| Pin  | Name    | Dir | Туре           | Function                                    |

|------|---------|-----|----------------|---------------------------------------------|