# Tsi148<sup>™</sup> PCI/X-to-VME Bus Bridge User Manual

Final March 2009 80A3020\_MA001\_12

#### Trademarks

TUNDRA is a registered trademark of Tundra Semiconductor Corporation (Canada, U.S., and U.K.). TUNDRA, the Tundra logo, Tsi148, and Silicon Behind the Network, are trademarks of Tundra Semiconductor Corporation. All other registered and unregistered marks (including trademarks, service marks and logos) are the property of their respective owners. The absence of a mark identifier is not a representation that a particular product name is not a mark.

#### Copyright

Copyright © March 2009 Tundra Semiconductor Corporation. All rights reserved. Published in Canada

This document contains information that is proprietary to Tundra and may be used for non-commercial purposes within your organization in support of Tundra products. No other use or transmission of all or any part of this document is permitted without written permission from Tundra, and must include all copyright and other proprietary notices. Use or transmission of all or any part of this document in violation of any applicable Canadian or other legislation is hereby expressly prohibited.

User obtains no rights in the information or in any product, process, technology or trademark which it includes or describes, and is expressly prohibited from modifying the information or creating derivative works without the express written consent of Tundra.

#### Disclaimer

Tundra assumes no responsibility for the accuracy or completeness of the information presented, which is subject to change without notice. Tundra products may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. In no event will Tundra be liable for any direct, indirect, special, incidental or consequential damages, including lost profits, lost business or lost data, resulting from the use of or reliance upon the information, whether or not Tundra has been advised of the possibility of such damages. The information contained in this document does not affect or change Tundra's product warranties.

Mention of non-Tundra products or services is for information purposes only and constitutes neither an endorsement nor a recommendation.

As this information will change over time, please ensure you have the most recent version by contacting a member of the Tundra technical support team, or by checking the Support section of www.tundra.com.

# **Corporate Profile**

#### **About Tundra**

Tundra Semiconductor Corporation (TSX:TUN) supplies the world's leading communications, computing and storage companies with smart System Interconnect products, intellectual property (IP) and design services backed by world-class customer service and technical support. Tundra's track record of product leadership includes over a decade of bridges and switches enabling key industry standards: RapidIO®, PCI, PCI-X, PCI Express®, PowerPC®, VME, HyperTransport<sup>™</sup>, Interlaken, and SPI4.2. Tundra's products deliver high functional quality and simplified board design and layout, with specific focus on system level signal integrity. Tundra's design services, semiconductor intellectual property and product development consulting. Tundra's smart technology connects critical components in high performance embedded systems around the world.

## **Tundra System Interconnect**

Tundra uses the term *System Interconnect* to refer to the technology used to connect all the components and sub-systems in almost any embedded system. This concept applies to the interfacing of functional elements (CPU, memory, I/O complexes) within a single-board system, and the interconnection of multiple boards in a larger system.

Advanced communications networks need advanced System Interconnect. It is a vital enabling technology for the networked world. Tundra System Interconnect provides the latest interface and throughput features, which enable communications infrastructure vendors to design and build more powerful, faster equipment in shorter timeframes.

Tundra System Interconnect — vital to building the communications systems of the future:

- Tundra System Interconnect products enable customers to get the performance, scalability, and reliability from their systems to meet today's and tomorrow's bandwidth demands.

- Tundra System Interconnect products are standards-based, off-the-shelf products that help customers speed their time to market.

- Tundra System Interconnect products meet the growing customer demand for outsourced standards-based interconnect products.

#### **Partnerships**

Fundamental to the success of Tundra is its partnerships with leading technology companies, including IBM, Intel, and Freescale. As a result of these alliances, Tundra devices complement our partners' products, and greatly influence the design of customers' architecture. Customers are changing their designs to incorporate Tundra products. This is evidence of our commitment to be a significant part of its customers' success.

#### Customers

Tundra Semiconductor products are used by the world's leading communications infrastructure and storage vendors, including Cisco Systems, Freescale, Siemens, Nortel Networks, Lucent Technologies, Nokia, Ericsson, Alcatel, and Hewlett-Packard.

The Tundra design philosophy is one in which a number of strategic customers are invited to participate in the definition, design, test, and early silicon phases of product development. Close working relationships with customers and clear product roadmaps ensure that Tundra can anticipate and meet the future directions and needs of communications systems designers and manufacturers.

## Support

Tundra is respected throughout the industry for its outstanding commitment to customer support. Tundra ensures that its customers can take immediate advantage of the company's products through its in-house Applications Engineering Group, unmatched design support tools, and full documentation accessible through the Web.

Design. Connect. Go.<sup>™</sup>

# **Contact Information**

Tundra is dedicated to providing superior technical documentation and design support to its customers. The following support options are available:

Web

| Product information         | The Tundra website at www.tundra.com contains the features, benefits, typical applications, and block diagram for the Tsi148. This website also allows you to register in oder to receive the full suite of product information. |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technical support resources | The Support section of the Tundra website contains an<br>extensive list of technical resources to assist with your<br>design needs. Some of the key support resources include:                                                   |

|                             | Technical support FAQ                                                                                                                                                                                                            |

|                             | • User documentation                                                                                                                                                                                                             |

|                             | • Schematic design checklists and debug guidelines                                                                                                                                                                               |

|                             | You can also opt to receive email notification when a support resource is added or changed.                                                                                                                                      |

| Technical support request   | To contact Tundra support personnel about a technical question, fill out the Technical Support Request Form in the Support section of the website.                                                                               |

| Sales support | The sales section of the Tundra website contains<br>information that will help you locate a Tundra sales<br>representative nearest you. |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Mail          | Tundra Semiconductor Corporation<br>603 March Road<br>Ottawa, ON, Canada<br>K2K 2M5                                                     |

| Fax           | 613-592-1320                                                                                                                            |

# Contents

| Со | rporat  | e Profi           | ile                                  |  |  |  |  |  |  |  |  |  |  |

|----|---------|-------------------|--------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Со | ntact I | Informa           | ation5                               |  |  |  |  |  |  |  |  |  |  |

| Ab | out th  | is Doc            | ument                                |  |  |  |  |  |  |  |  |  |  |

|    | Docu    | iment Conventions |                                      |  |  |  |  |  |  |  |  |  |  |

|    | Revis   | sion History      |                                      |  |  |  |  |  |  |  |  |  |  |

|    | Relate  | ed Inform         | nation                               |  |  |  |  |  |  |  |  |  |  |

| 1. | Fund    | ctional           | Overview                             |  |  |  |  |  |  |  |  |  |  |

|    | 1.1     | Overvie           | ew of Tsi148                         |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.1.1             | VME Renaissance                      |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.1.2             | Tsi148 Features                      |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.1.3             | Tsi148 Benefits.         32          |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.1.4             | Typical Applications                 |  |  |  |  |  |  |  |  |  |  |

|    | 1.2     | VMEbu             | us Interface                         |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.2.1             | 2eVME Protocol                       |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.2.2             | 2eSST Protocol                       |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.2.3             | VME Slave                            |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.2.4             | VME Master                           |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.2.5             | Tsi148 as a VMEbus System Controller |  |  |  |  |  |  |  |  |  |  |

|    | 1.3     | PCI/X             | Interface                            |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.3.1             | PCI/X Target                         |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.3.2             | PCI/X Master                         |  |  |  |  |  |  |  |  |  |  |

|    | 1.4     | Linkag            | e Module                             |  |  |  |  |  |  |  |  |  |  |

|    | 1.5     | Registe           | vr Overview                          |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.5.1             | Control and Status Registers         |  |  |  |  |  |  |  |  |  |  |

|    | 1.6     | DMA (             | Controllers                          |  |  |  |  |  |  |  |  |  |  |

|    |         | 1.6.1             | Data Movement                        |  |  |  |  |  |  |  |  |  |  |

|    | 1.7   | Interrupter and Interrupt Handler               |  |  |  |  |  |  |  |  |  |  |

|----|-------|-------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|    | 1.8   | JTAG                                            |  |  |  |  |  |  |  |  |  |  |

| 2. | VME   | Interface                                       |  |  |  |  |  |  |  |  |  |  |

|    | 2.1   | Overview of the VME Interface                   |  |  |  |  |  |  |  |  |  |  |

|    | 2.2   | VME Slave                                       |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.2.1 VME Slave Buffers                         |  |  |  |  |  |  |  |  |  |  |

|    | 2.3   | VME Master                                      |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.1 Addressing Capabilities                   |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.2 VME Master Buffers                        |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.3 VME Master Read-Modify Write (RMW) Cycles |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.4 VME Master Bandwidth Control              |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.5 VMEbus Exception Handling                 |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.6 Utility Functions                         |  |  |  |  |  |  |  |  |  |  |

|    |       | 2.3.7 Tsi148 as a VMEbus System Controller      |  |  |  |  |  |  |  |  |  |  |

| 3. | PCI/X | (Interface                                      |  |  |  |  |  |  |  |  |  |  |

|    | 3.1   | Overview of the PCI/X Interface                 |  |  |  |  |  |  |  |  |  |  |

|    | 3.2   | PCI Mode                                        |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.2.1 PCI Target                                |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.2.2 PCI Master                                |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.2.3 PCI Bus Exception Handling                |  |  |  |  |  |  |  |  |  |  |

|    | 3.3   | PCI-X Mode                                      |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.3.1 PCI-X Target                              |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.3.2 PCI-X Master                              |  |  |  |  |  |  |  |  |  |  |

|    |       | 3.3.3 PCI-X Bus Exception Handling              |  |  |  |  |  |  |  |  |  |  |

| 4. | DMA   | Interface                                       |  |  |  |  |  |  |  |  |  |  |

|    | 4.1   | Overview DMA Controller                         |  |  |  |  |  |  |  |  |  |  |

|    | 4.2   | Architecture                                    |  |  |  |  |  |  |  |  |  |  |

|    | 4.3   | DMA Buffers                                     |  |  |  |  |  |  |  |  |  |  |

|    | 4.4   | Operating Modes                                 |  |  |  |  |  |  |  |  |  |  |

|    |       | 4.4.1 Linked-List Descriptors                   |  |  |  |  |  |  |  |  |  |  |

|    | 4.5   | Directio | on of Data Movement                       |

|----|-------|----------|-------------------------------------------|

|    |       | 4.5.1    | PCI/X-to-VME                              |

|    |       | 4.5.2    | VME-to-PCI/X                              |

|    |       | 4.5.3    | PCI/X-to-PCI/X                            |

|    |       | 4.5.4    | VME-to-VME                                |

|    |       | 4.5.5    | Data Patterns                             |

|    |       | 4.5.6    | DMA Transaction Termination 118           |

|    |       | 4.5.7    | DMA Interrupts 119                        |

|    |       | 4.5.8    | Transfer Throttling                       |

| 5. | Rese  | ets, Clo | cks, and Power-up Options 121             |

|    | 5.1   | Overvie  | w of Resets, Clocks, and Power-up Options |

|    | 5.2   | Resets . |                                           |

|    |       | 5.2.1    | Reset Inputs and Outputs                  |

|    |       | 5.2.2    | Reset Timing                              |

|    | 5.3   | Clocks.  |                                           |

|    | 5.4   | Power-u  | 128 up Options                            |

|    |       | 5.4.1    | PCI/X Power-up Options                    |

|    |       | 5.4.2    | VMEbus Power-up Options                   |

|    |       | 5.4.3    | System Controller (SCON) 135              |

| 6. | Inter | rupt Co  | ontroller                                 |

|    | 6.1   | Overvie  | w of the Interrupt Controller             |

|    | 6.2   | VMEbu    | s Interrupter                             |

|    | 6.3   | Local Ir | nterrupter                                |

|    | 6.4   | VMEbu    | s Interrupt Handler                       |

| 7. | JTA   | G Modu   | ıle                                       |

|    | 7.1   | Overvie  | w of JTAG                                 |

|    | 7.2   | Instruct | ions                                      |

| 8. | Sign  | als and  | l Pins                                    |

|    | 8.1   | Overvie  | w of Signals                              |

|    | 8.2   | Signal C | Grouping                                  |

|    | 8.3   | Signal S | Summary                                   |

|    | 8.4   | Detailed | 1 Signal Descriptions                     |

|    |       | 8.4.1    | PCI/X Signal Descriptions                 |

|    |       | 8.4.2    | VMEbus Signal Descriptions                |

|    |       | 8.4.3    | Miscellaneous Signal Descriptions         |

|     | 8.5  | Pinout   |                                                        | . 171 |

|-----|------|----------|--------------------------------------------------------|-------|

|     |      | 8.5.1    | Sorted by Pin Assignment                               | . 172 |

| 9.  | Elec | trical C | Characteristics                                        | .185  |

|     | 9.1  | Overvie  | ew of Electrical Characteristics                       | . 186 |

|     |      | 9.1.1    | PCI/X Electrical Characteristics                       | . 186 |

|     |      | 9.1.2    | Non-PCI Electrical Characteristics                     | . 187 |

|     | 9.2  | Operati  | ng Conditions                                          | . 188 |

|     |      | 9.2.1    | Absolute Maximum Operating Conditions.                 | . 188 |

|     |      | 9.2.2    | Recommended Operating Conditions.                      | . 189 |

|     |      | 9.2.3    | Power Supply Sequencing                                | . 189 |

|     | 9.3  | Power C  | Consumption                                            | . 189 |

|     | 9.4  | Therma   | l Characteristics                                      | . 190 |

|     |      | 9.4.1    | Junction-to-Ambient Thermal Characteristics (Theta ja) | . 190 |

|     |      | 9.4.2    | Junction-to-Board and Junction-to-Case Characteristics | . 191 |

|     | 9.5  | Electros | static Discharge (ESD)                                 | . 192 |

|     |      | 9.5.1    | ESD Precautions                                        | . 192 |

| 10  | Dogi | otoro    |                                                        | 105   |

| 10. | -    |          | an of Devictory                                        |       |

|     | 10.1 |          | ew of Registers                                        |       |

|     | 10.2 | 0        | r Groupings                                            |       |

|     |      | 10.2.1   | Combined Register Group (CRG)                          |       |

|     |      | 10.2.2   | PCI/X Configuration Space Registers (PCFS)             |       |

|     |      | 10.2.3   | Local Control and Status Registers (LCSR)              |       |

|     |      | 10.2.4   | Global Control and Status Registers (GCSR).            |       |

|     |      | 10.2.5   | Control and Status Registers (CSR)                     |       |

|     | 10.0 | 10.2.6   | CR/CSR Register Access                                 |       |

|     | 10.3 |          | r Endian Mapping                                       |       |

|     | 10.4 | 0        | r Map                                                  |       |

|     |      | 10.4.1   | Conventions                                            |       |

|     |      | 10.4.2   | PCFS Register Group Overview                           |       |

|     |      | 10.4.3   | LCSR Register Group Overview                           |       |

|     |      | 10.4.4   | GCSR Register Group Overview                           |       |

|     |      | 10.4.5   | CR/CSR Register Group Overview                         |       |

|     |      | 10.4.6   | PCFS Register Group Description                        |       |

|     |      | 10.4.7   | Vendor ID/ Device ID Registers                         |       |

|     |      | 10.4.8   | Command/Status Registers                               |       |

|     |      | 10.4.9   | Revision ID / Class Code Registers                     | . 221 |

| Cache Line Size / Master Latency Timer / Header Type Registers       | 222                                |

|----------------------------------------------------------------------|------------------------------------|

| Memory Base Address Lower Register                                   | 224                                |

| Memory Base Address Upper Register                                   | 225                                |

| Subsystem Vendor ID/ Subsystem ID Registers                          | 226                                |

| Capabilities Pointer Register                                        | 227                                |

| Interrupt Line/interrupt PIn/Minimum Grant/Maximum Latency Registers | 228                                |

| PCI-X Capabilities Register                                          | 231                                |

| PCI-X Status Register                                                | 233                                |

| LCSR Register Group Description                                      | 236                                |

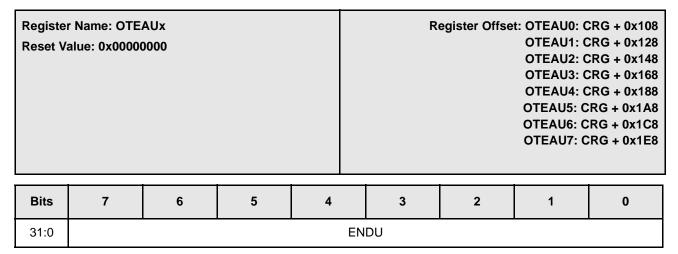

| Outbound Translation Starting Address Upper (0-7) Registers          | 236                                |

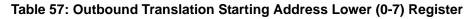

| Outbound Translation Starting Address Lower (0-7) Registers          | 237                                |

| Outbound Translation Ending Address Upper (0-7) Registers            | 238                                |

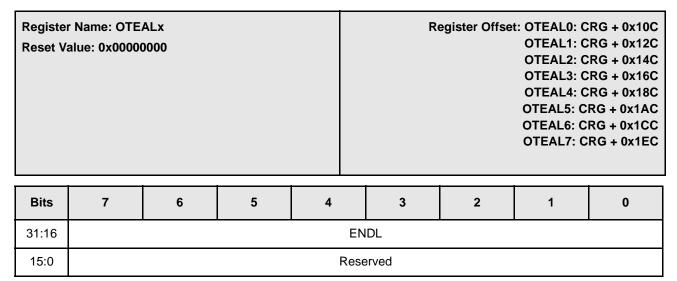

| Outbound Translation Ending Address Lower (0-7) Registers            | 239                                |

| Outbound Translation Offset Upper (0-7) Registers                    | 240                                |

| Outbound Translation Offset Lower (0-7) Registers                    | 241                                |

| Outbound Translation 2eSST Broadcast Select (0-7) Registers          | 242                                |

| Outbound Translation Attribute (0-7) Registers                       | 243                                |

| VMEbus IACK (1-7) Registers                                          | 247                                |

| VMEbus Read-Modify-Write (RMW) Address Upper Register                | 248                                |

| VMEbus RMW Address Lower Register                                    | 249                                |

| VMEbus RMW Enable Register                                           | 250                                |

| VMEbus RMW Compare Register                                          | 251                                |

| VMEbus RMW Swap Register                                             | 252                                |

| VME Master Control Register                                          | 253                                |

| VMEbus Control Register                                              | 257                                |

| VMEbus Status Register                                               | 261                                |

| PCI/X Control / Status Register                                      | 263                                |

| VMEbus Filter Register.                                              | 267                                |

| VMEbus Exception Address Upper Register.                             | 269                                |

| VMEbus Exception Address Lower Register                              | 270                                |

| VMEbus Exception Attributes Register                                 | 271                                |

| Error Diagnostic PCI/X Address Upper Register                        | 274                                |

| Error Diagnostic PCI/X Address Lower Register                        | 275                                |

| Error Diagnostic PCI-X Attribute Register                            | 276                                |

| Error Diagnostic PCI-X Split Completion Message Register             | 277                                |

| Error Diagnostic PCI/X Attributes Register                           | 278                                |

| Inbound Translation Starting Address Upper (0-7) Registers           | 281                                |

|                                                                      | Memory Base Address Lower Register |

| 10.4.47 | Inbound Translation Starting Address Lower (0-7) Registers |

|---------|------------------------------------------------------------|

| 10.4.48 | Inbound Translation Ending Address Upper (0-7) Registers   |

| 10.4.49 | Inbound Translation Ending Address Lower (0-7) Registers   |

| 10.4.50 | Inbound Translation Offset Upper (0-7) Registers           |

| 10.4.51 | Inbound Translation Offset Lower (0-7) Registers           |

| 10.4.52 | Inbound Translation Attribute (0-7) Registers              |

| 10.4.53 | GCSR Base Address Upper Register                           |

| 10.4.54 | GCSR Base Address Lower Register                           |

| 10.4.55 | GCSR Attribute Register                                    |

| 10.4.56 | CRG Base Address Upper Register                            |

| 10.4.57 | CRG Base Address Lower Register                            |

| 10.4.58 | CRG Attribute Register                                     |

| 10.4.59 | CR/CSR Offset Upper Register                               |

| 10.4.60 | CR/CSR Offset Lower Register                               |

| 10.4.61 | CR/CSR Attribute Register                                  |

| 10.4.62 | Location Monitor Base Address Upper Register               |

| 10.4.63 | Location Monitor Base Address Lower Register               |

| 10.4.64 | Location Monitor Attribute Register                        |

| 10.4.65 | 64-bit Counter Upper                                       |

| 10.4.66 | 64-bit Counter Lower                                       |

| 10.4.67 | Broadcast Pulse Generator Timer Register                   |

| 10.4.68 | Broadcast Programmable Clock Timer Register                |

| 10.4.69 | VMEbus Interrupt Control Register                          |

| 10.4.70 | Interrupt Enable Register                                  |

| 10.4.71 | Interrupt Enable Out Register                              |

| 10.4.72 | Interrupt Status Register                                  |

| 10.4.73 | Interrupt Clear Register                                   |

| 10.4.74 | Interrupt Map 1 Register                                   |

| 10.4.75 | Interrupt Map 2 Register                                   |

| 10.4.76 | DMA Control (0-1) Registers                                |

| 10.4.77 | DMA Status (0-1) Registers                                 |

| 10.4.78 | DMA Current Source Address Upper (0-1) Registers           |

| 10.4.79 | DMA Current Source Address Lower (0-1) Registers           |

| 10.4.80 | DMA Current Destination Address Upper (0-1) Registers      |

| 10.4.81 | DMA Current Destination Address Lower (0-1) Registers      |

| 10.4.82 | DMA Current Link Address Upper (0-1) Registers             |

| 10.4.83 | DMA Current Link Address Lower (0-1) Registers             |

|    |            | 10.4.84        | DMA Source Address Upper (0-1) Registers             | 345 |  |  |  |  |  |  |  |  |  |  |

|----|------------|----------------|------------------------------------------------------|-----|--|--|--|--|--|--|--|--|--|--|

|    |            | 10.4.85        | DMA Source Address Lower (0-1) Registers             | 346 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.86        | DMA Destination Address Upper (0-1) Registers        | 347 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.87        | 0.4.87 DMA Destination Address Lower (0-1) Registers |     |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.88        | 10.4.88 DMA Source Attribute (0-1) Registers         |     |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.89        | .4.89 DMA Destination Attribute (0-1) Registers      |     |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.90        | .90 DMA Next Link Address Upper (0-1) Registers      |     |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.91        | DMA Next Link Address Lower (0-1) Registers.         | 358 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.92        | DMA Count (0-1) Registers.                           | 359 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.93        | DMA Destination Broadcast Select (0-1) Registers     | 360 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.94        | GCSR Register Group                                  | 361 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.95        | Vendor ID / Device ID Registers                      | 361 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.96        | Control and Status Register                          | 362 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.97        | Semaphore Registers (0-3).                           | 365 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.98        | Semaphore Registers (4-7).                           | 366 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.99        | Mail Box Registers (0-3)                             | 367 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.100       | OCR/CSR Register Group Description                   | 368 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.10        | 1 CR/CSR Bit Clear Register                          | 368 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.102       | 2 CR/CSR Bit Set Register                            | 370 |  |  |  |  |  |  |  |  |  |  |

|    |            | 10.4.103       | 3 CR/CSR Base Address Register                       | 372 |  |  |  |  |  |  |  |  |  |  |

| Α. | Турі       | cal App        | olications                                           | 373 |  |  |  |  |  |  |  |  |  |  |

|    | A.1        | Overvie        | ·w                                                   | 373 |  |  |  |  |  |  |  |  |  |  |

|    | A.2        | Tsi148 (       | Connection Schematics                                | 374 |  |  |  |  |  |  |  |  |  |  |

| B. | Hard       | lwaro Ir       | nplementation                                        | 295 |  |  |  |  |  |  |  |  |  |  |

| D. |            |                | •                                                    |     |  |  |  |  |  |  |  |  |  |  |

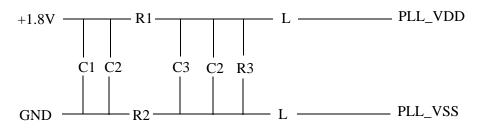

|    | B.1<br>B.2 |                | PLL Filtering.                                       |     |  |  |  |  |  |  |  |  |  |  |

|    | Б.2<br>В.3 |                | ance Decoupling Recommendations                      |     |  |  |  |  |  |  |  |  |  |  |

|    | D.3        | B.3.1          | -                                                    |     |  |  |  |  |  |  |  |  |  |  |

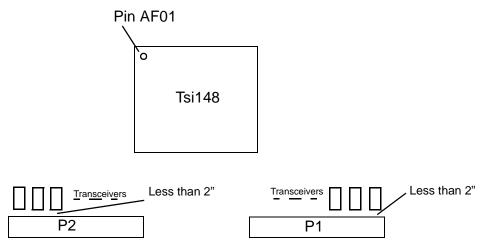

|    |            | в.з.1<br>В.3.2 | Trace Length Recommendations                         |     |  |  |  |  |  |  |  |  |  |  |

|    |            | D.3.2          | Recommended Stackup                                  | 200 |  |  |  |  |  |  |  |  |  |  |

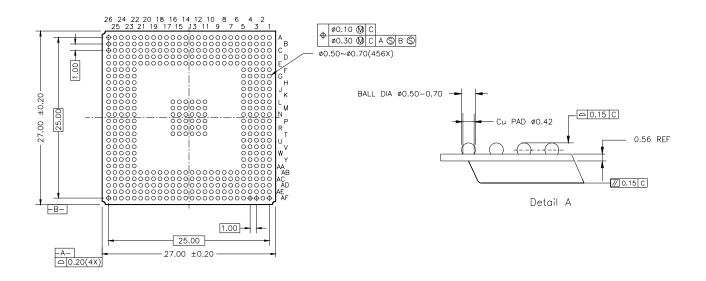

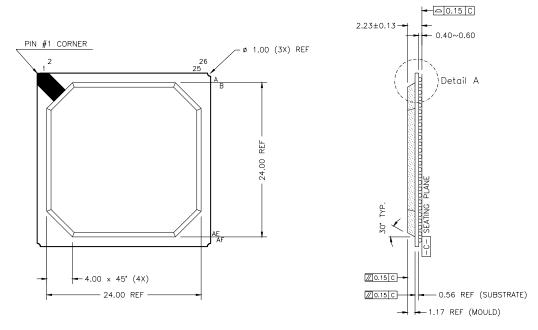

| С. | Pacl       | kage Inf       | formation                                            | 389 |  |  |  |  |  |  |  |  |  |  |

|    | C.1        | Package        | Characteristics                                      | 389 |  |  |  |  |  |  |  |  |  |  |

|    |            | C.1.1          | Package Notes                                        | 390 |  |  |  |  |  |  |  |  |  |  |

| D. | Orde       | erina In       | formation                                            | 391 |  |  |  |  |  |  |  |  |  |  |

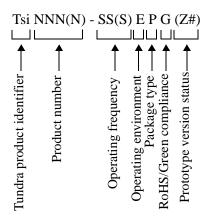

| -  | D.1        | -              | g Information                                        |     |  |  |  |  |  |  |  |  |  |  |

|    | D.2        |                | mbering.                                             |     |  |  |  |  |  |  |  |  |  |  |

|    |            |                |                                                      |     |  |  |  |  |  |  |  |  |  |  |

| Bit Index | <br>• • • | • • • | • • • | <br>••• | • • | ••• | • • • | • • | <br>••• | • • | • • | • • | • • • | • • | •• | • • | • • | • • | - | •• | • • | <br>••• | • • | <br>.3 | 95 |

|-----------|-----------|-------|-------|---------|-----|-----|-------|-----|---------|-----|-----|-----|-------|-----|----|-----|-----|-----|---|----|-----|---------|-----|--------|----|

| Index     | <br>      |       |       | <br>    |     |     |       |     | <br>    |     |     |     |       |     |    |     |     |     |   |    | • • | <br>    |     | <br>.4 | 01 |

# **List of Figures**

| Figure 1:  | Tsi148 Block Diagram                                              | 30 |

|------------|-------------------------------------------------------------------|----|

| Figure 2:  | Typical Application — Tsi148 In Single Board Computer Application | 33 |

| Figure 3:  | Divisions of the CRG Register Space                               | 42 |

| Figure 4:  | CR/CSR Register Space                                             | 43 |

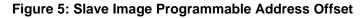

| Figure 5:  | Slave Image Programmable Address Offset                           | 51 |

| Figure 6:  | VMEbus to PCI/X Read Request                                      | 53 |

| Figure 7:  | VMEbus to PCI/X Read Completion                                   | 55 |

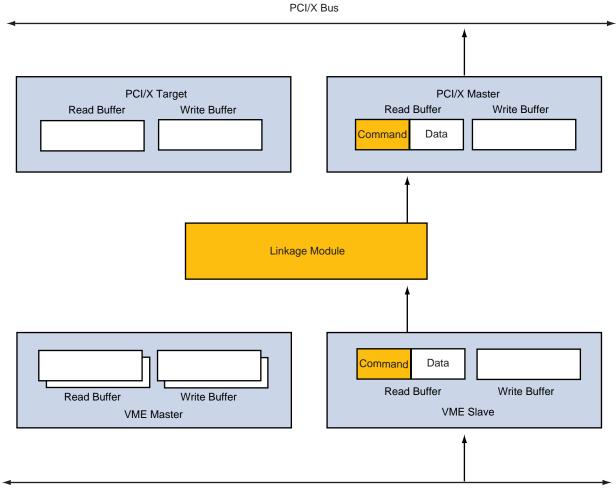

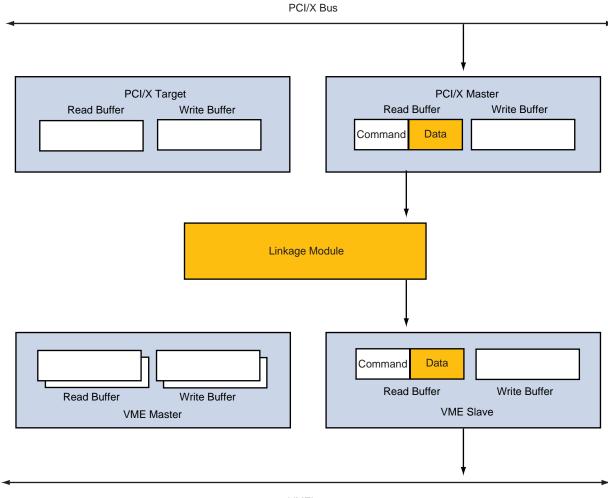

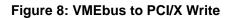

| Figure 8:  | VMEbus to PCI/X Write                                             | 57 |

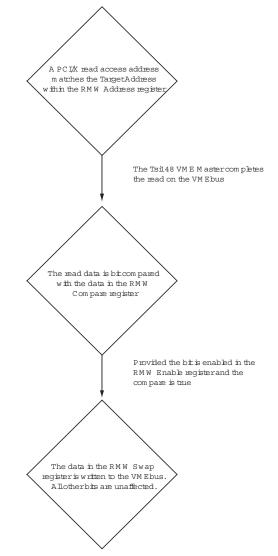

| Figure 9:  | Steps Used to Perform RMW Cycles on the VMEbus                    | 62 |

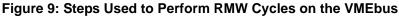

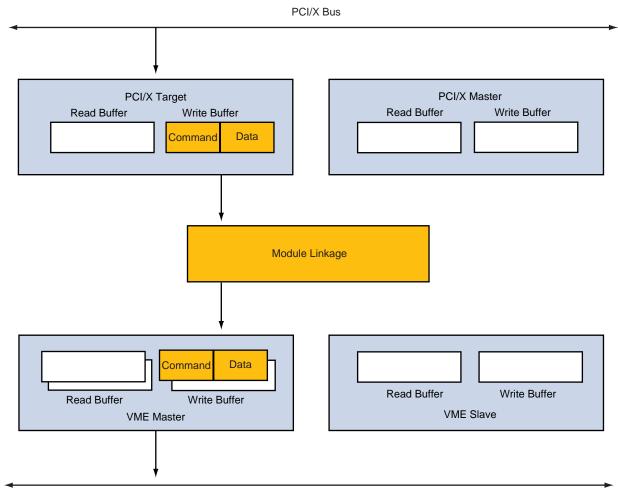

| Figure 10: | PCI Target Image Programmable Address Offset.                     | 74 |

| Figure 11: | PCI-VME Delayed Read Request                                      | 77 |

| Figure 12: | PCI-to-VME Delayed Read Completion.                               | 79 |

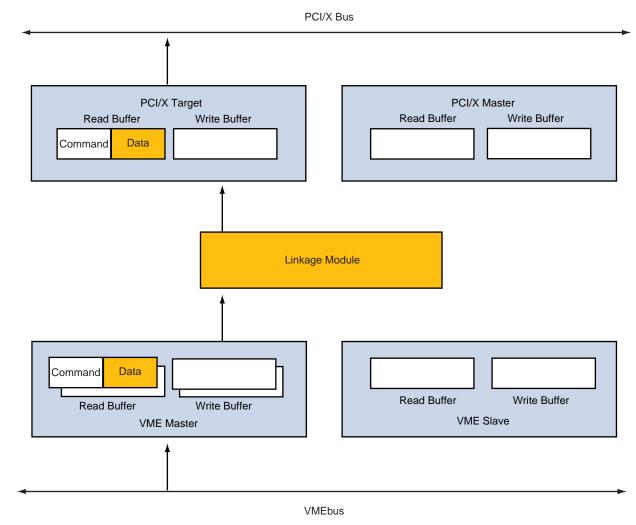

| Figure 13: | PCI-to-VME Posted Write                                           | 81 |

| Figure 14: | Target Image Programmable Address Offset                          | 88 |

| Figure 15: | PCI-X-to-VME Delayed Read Request.                                | 90 |

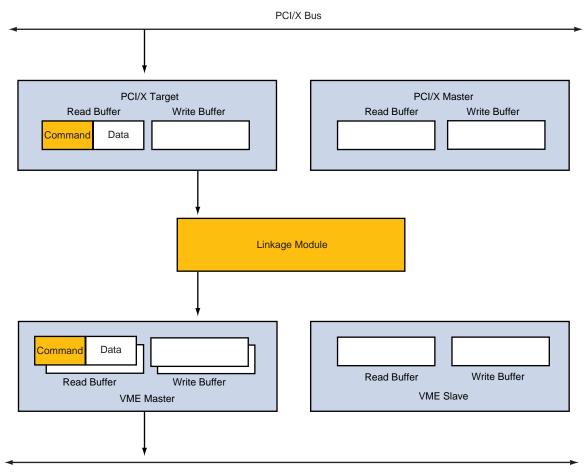

| Figure 16: | PCI-X-to-VME Delayed Read Completion.                             | 92 |

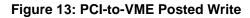

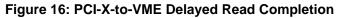

| Figure 17: | PCI-X-to-VME Posted Write                                         | 94 |

| Figure 18: | Direct Mode1                                                      | 01 |

| Figure 19: | Linked-list Mode                                                  | 02 |

| Figure 20: | DMA Transaction: PCI/X-to-VME Request1                            | 05 |

| Figure 21: | DMA Transaction: PCI/X-to-VME Completion1                         | 06 |

| Figure 22: | DMA Transaction: VME-to-PCI/X Request1                            | 08 |

| Figure 23: | DMA Transaction: VME-to-PCI/X Completion1                         | 09 |

| Figure 24: | DMA Transaction: PCI/X-to-PCI/X Request                           | 11 |

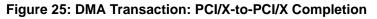

| Figure 25: | DMA Transaction: PCI/X-to-PCI/X Completion1                       | 12 |

| Figure 26: DMA Transaction: VME-to-VME Request                             |

|----------------------------------------------------------------------------|

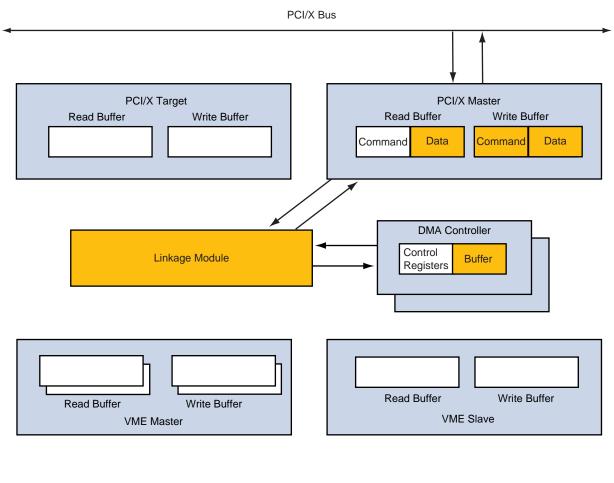

| Figure 27: DMA Transaction: VME-to-VME Completion115                       |

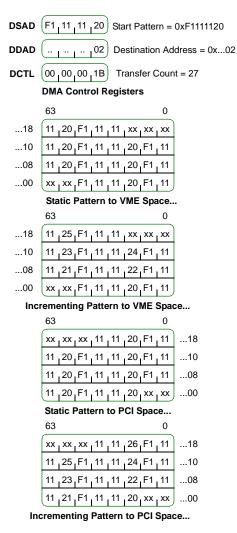

| Figure 28: 8-bit Pattern Writes                                            |

| Figure 29: 32-bit Pattern Writes                                           |

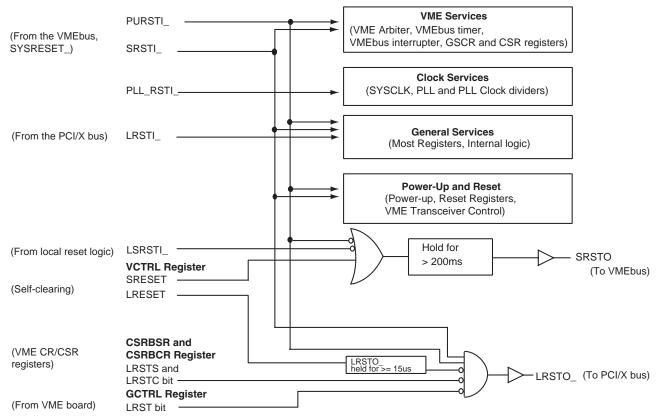

| Figure 30: Tsi148 Reset Structure                                          |

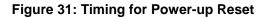

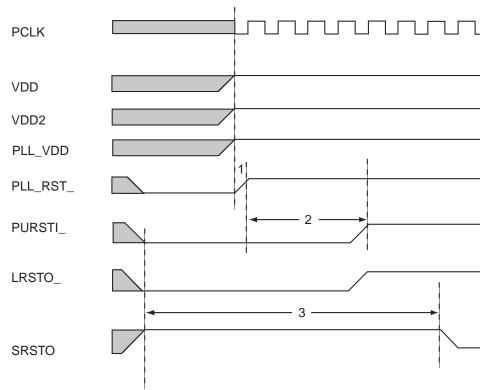

| Figure 31: Timing for Power-up Reset                                       |

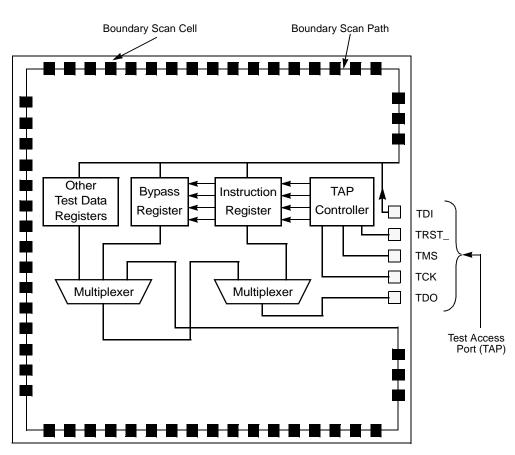

| Figure 32: JTAG Functional Diagram142                                      |

| Figure 33: Signal Grouping146                                              |

| Figure 34: Pinout — Bottom View                                            |

| Figure 35: Combined Register Group (CRG)196                                |

| Figure 36: CR/CSR Address Space                                            |

| Figure 37: Big to Little Endian Data Swap                                  |

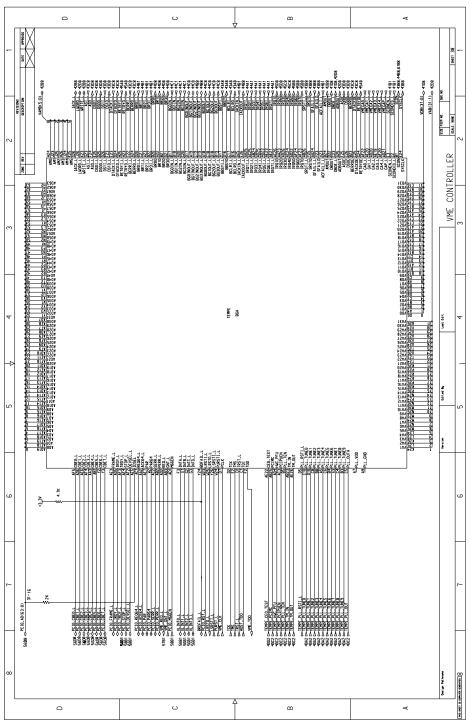

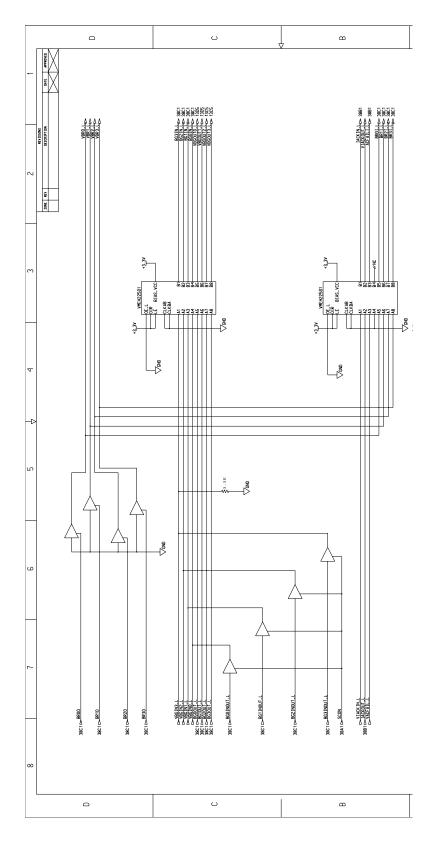

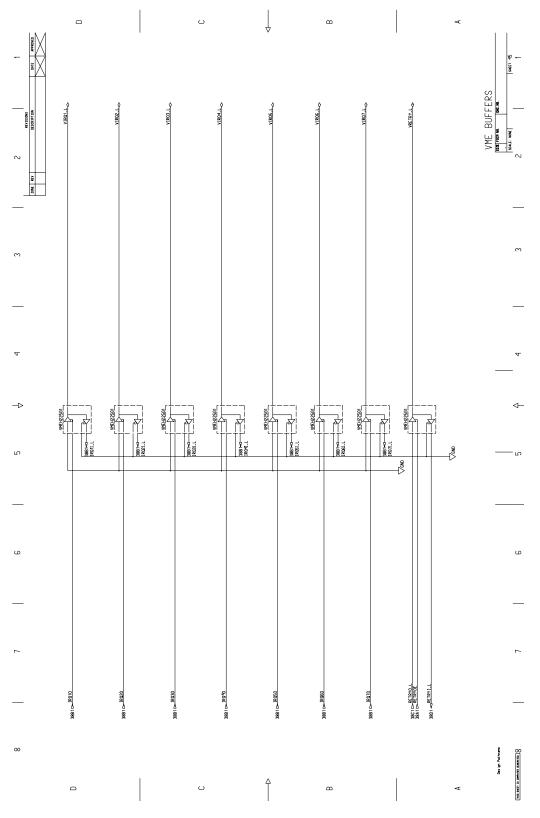

| Figure 38: Tsi148 Schematic (Page 38) - Tsi148 Device                      |

| Figure 39: Tsi148 Schematic (Page 39) - Power Pins                         |

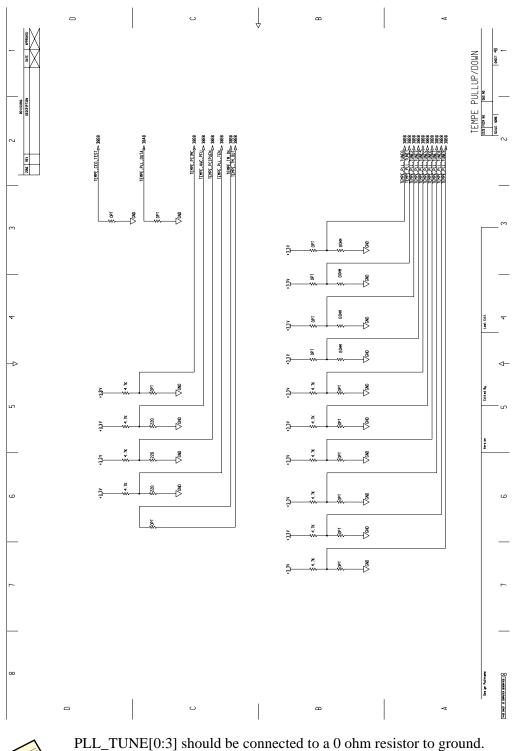

| Figure 40: Tsi148 Schematic (Page 40) - Pull-up and Pull-down Requirements |

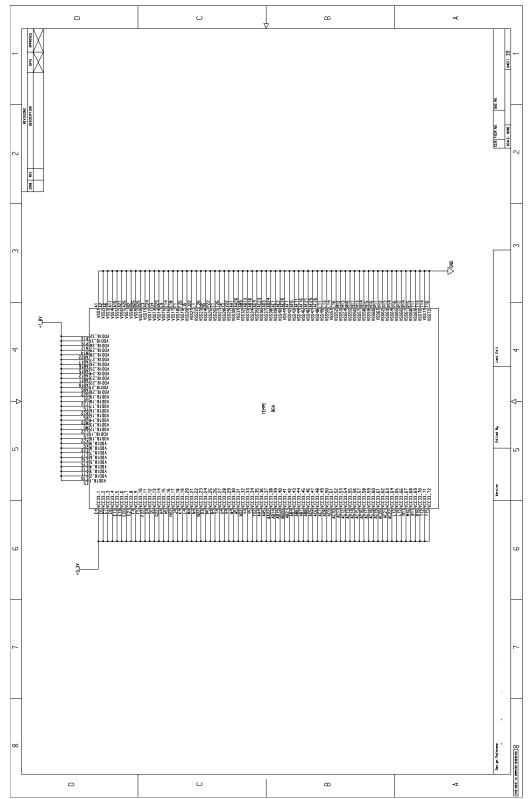

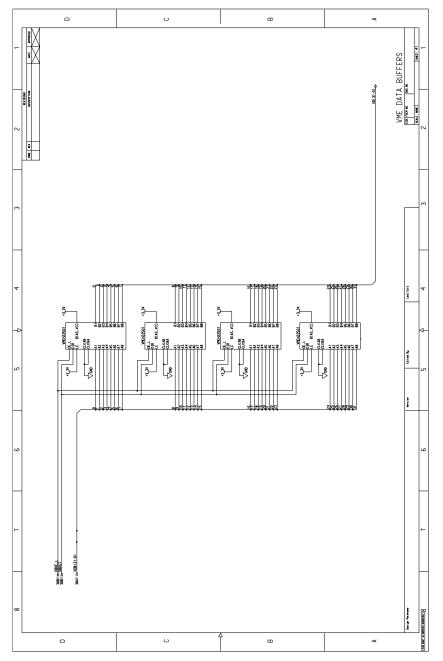

| Figure 41: Tsi148 Schematic (Page 41) - VME Data Buffers                   |

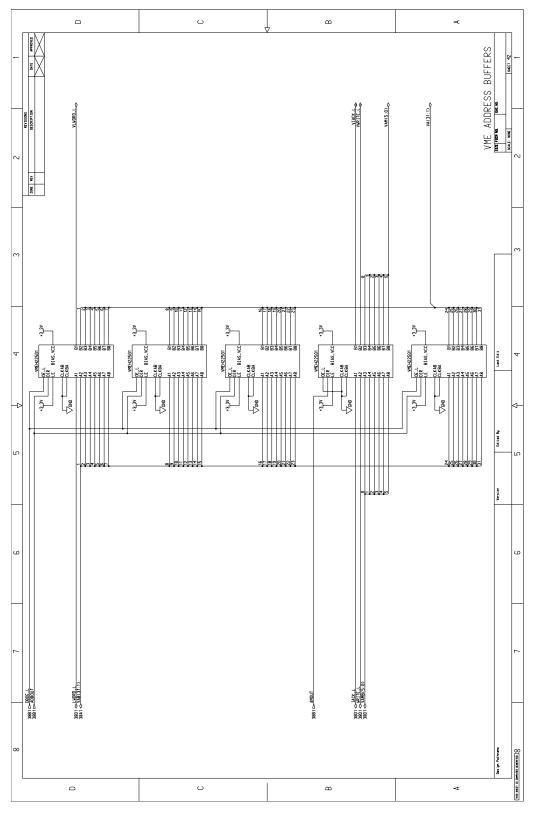

| Figure 42: Tsi148 Schematic (Page 42) - VME Address Buffers                |

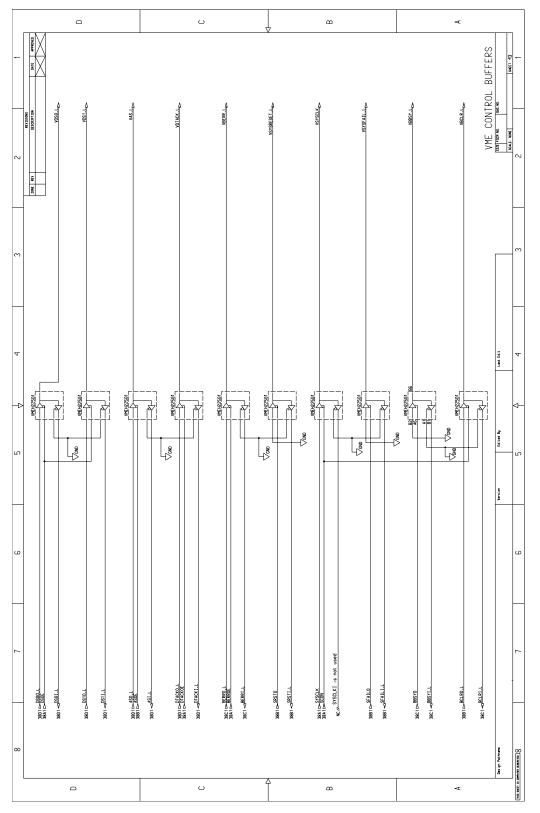

| Figure 43: Tsi148 Schematic (Page 43) - VME Control Buffers                |

| Figure 44: Tsi148 Schematic (Page 44) - VME Transceivers                   |

| Figure 45: Tsi148 Schematic (Page 45) - VME Transceivers                   |

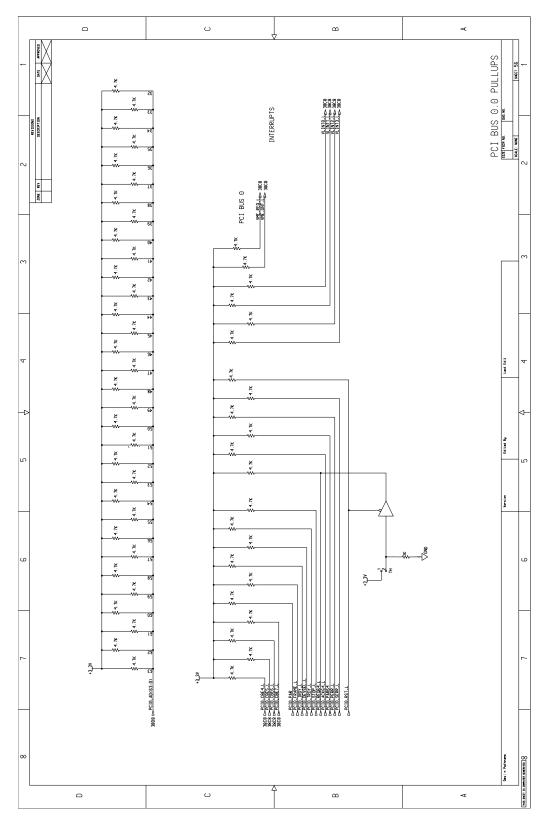

| Figure 46: Tsi148 Schematic (Page 56) - PCI Bus 0.0 and 1.0 Pull-ups       |

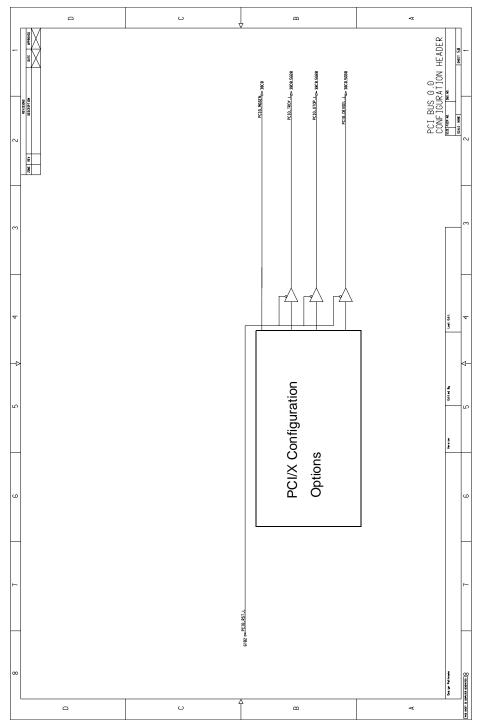

| Figure 47: Tsi148 Schematic (Page 58) - PCI Bus 0.0 Configuration Header   |

| Figure 48: Recommended PLL Filter                                          |

| Figure 49: Tsi148 PBGA Orientation                                         |

| Figure 50: 456-Pin PBGA Package Diagram — Bottom and Side Views            |

| Figure 51: 456-Pin PBGA Package Diagram — Top and Side View                |

# **List of Tables**

| Table 1:  | VMEbus Address Mode Codes                       | 59  |

|-----------|-------------------------------------------------|-----|

| Table 2:  | Location Monitor Interrupt Addresses            | 66  |

| Table 3:  | PCI Read Data Size                              | .76 |

| Table 4:  | DMA Controller Linked-List Descriptors          | 102 |

| Table 5:  | PCI Bus Configuration1                          | 127 |

| Table 6:  | PCI/X Bus Configuration                         | 129 |

| Table 7:  | VMEbus Power-up Options1                        | 130 |

| Table 8:  | ASIDEN and GSIDEN Definition 1                  | 131 |

| Table 9:  | CR/CSR Base Address Configuration               | 131 |

| Table 10: | VMEbus System Controller Configuration 1        | 135 |

| Table 11: | Signal Conventions - I/O Type 1                 | 147 |

| Table 12: | Signal Conventions - I/O Level                  | 147 |

| Table 13: | Signal Conventions - I/O Drive                  | 148 |

| Table 14: | Pin List                                        | 148 |

| Table 15: | VMEbus Signal Descriptions 1                    | 61  |

| Table 16: | Miscellaneous Signal Descriptions 1             | 168 |

| Table 17: | Pinout — Sorted by Pin Assignment 1             | 172 |

| Table 18: | VSS (Ground) — Sorted by Pin Assignment 1       | 179 |

| Table 19: | Core Power (1.8 V) — Sorted by Pin Assignment 1 | 82  |

| Table 20: | I/O Power (3.3 V) — Sorted by Pin Assignment 1  | 183 |

| Table 21: | PCI/X Electrical Characteristics                | 186 |

| Table 22: | 3.3 V LVTTL DC Electrical Characteristics       | 187 |

| Table 23: | 5.0 V LVTTL DC Electrical Characteristics       | 187 |

| Table 24: | Common Receiver DC Electrical Characteristics   | 87  |

| Table 25: | LVTTL Driver DC Electrical Characteristics 1    | 187 |

| Table 26: | 1.8 V CMOS Driver DC Electrical Characteristics                     |

|-----------|---------------------------------------------------------------------|

| Table 27: | Absolute Maximum Ratings                                            |

| Table 28: | Recommended Operating Conditions                                    |

| Table 29: | Tsi148 Total Power Dissipation (Core + IO)                          |

| Table 30: | Tsi148 Power Dissipation Division                                   |

| Table 31: | 456 EPBGA Package Thermal Performance for an 8 layer PCB191         |

| Table 32: | 456 EPBGA Package Thermal Performance for a 4 layer PCB191          |

| Table 33: | Thermal Characteristics of Tsi148191                                |

| Table 34: | Tsi148 ESD Classification192                                        |

| Table 35: | Endian Register Views                                               |

| Table 36: | PCFS Register Group                                                 |

| Table 37: | LCSR Register Group                                                 |

| Table 38: | GCSR Register Group                                                 |

| Table 39: | CR/CSR Register Group                                               |

| Table 40: | Vendor ID/ Device ID Registers                                      |

| Table 41: | Command/Status Register                                             |

| Table 42: | Revision ID / Class Code Register                                   |

| Table 43: | Cache Line Size / Master Latency Timer / Header Type Register       |

| Table 44: | Memory Base Address Lower Register                                  |

| Table 45: | Memory Base Address Upper Register                                  |

| Table 46: | Subsystem Vendor ID/ Subsystem ID Register                          |

| Table 47: | Capabilities Pointer Register                                       |

| Table 48: | Interrupt Line/Interrupt PIn/Minimum Grant/Maximum Latency Register |

| Table 49: | CRG Space Type                                                      |

| Table 50: | INTP INTx Encoding                                                  |

| Table 51: | PCI-X Capabilities Register                                         |

| Table 52: | MOST Encoding                                                       |

| Table 53: | MMRBC Encoding                                                      |

| Table 54: | PCI-X Status Register                                               |

| Table 55: | DMCRS Encoding                                                      |

| Table 56: | Outbound Translation Starting Address Upper (0-7) Register          |

| Table 57: | Outbound Translation Starting Address Lower (0-7) Register          |

| Table 58: | Outbound Translation Ending Address Upper (0-7) Register            |

| Table 59: | Outbound Translation Ending Address Lower (0-7) Register   |  |

|-----------|------------------------------------------------------------|--|

| Table 60: | Outbound Translation Offset Upper (0-7) Register           |  |

| Table 61: | : Outbound Translation Offset Lower (0-7) Register         |  |

| Table 62: | Outbound Translation 2eSST Broadcast Select (0-7) Register |  |

| Table 63: | Outbound Translation Attribute (0-7) Register              |  |

| Table 64: | Prefetch Size                                              |  |

| Table 65: | 2eSST Transfer Rate                                        |  |

| Table 66: | VMEbus Transfer Mode                                       |  |

| Table 67: | VMEbus Data Bus Width                                      |  |

| Table 68: | VMEbus Address Mode                                        |  |

| Table 69: | VMEbus IACK (1-7) Register                                 |  |

| Table 70: | VMEbus RMW Address Upper Register                          |  |

| Table 71: | VMEbus RMW Address Lower Register                          |  |

| Table 72: | VMEbus RMW Enable Register                                 |  |

| Table 73: | VMEbus RMW Compare Register                                |  |

| Table 74: | VMEbus RMW Swap Register                                   |  |

| Table 75: | VME Master Control Register                                |  |

| Table 76: | VME Master Time Off                                        |  |

| Table 77: | VME Master Time On                                         |  |

| Table 78: | VME Master Release Mode                                    |  |

| Table 79: | VMEbus Control Register                                    |  |

| Table 80: | Deadlock Timer                                             |  |

| Table 81: | VMEbus Global Time-out                                     |  |

| Table 82: | VMEbus Status Register                                     |  |

| Table 83: | PCI/X Control / Status Register                            |  |

| Table 84: | PCI-X Split Read Time-out                                  |  |

| Table 85: | PCI/X Control / Status Register                            |  |

| Table 86: | Acknowledge Delay Time                                     |  |

| Table 87: | VMEbus Exception Address Upper Register                    |  |

| Table 88: | VMEbus Exception Address Lower Register                    |  |

| Table 89: | VMEbus Exception Attributes Register                       |  |

| Table 90: | Error Diagnostic PCI/X Address Upper Register              |  |

| Table 91: | Error Diagnostic PCI/X Address Lower Register              |  |

| Table 92: | Error Diagnostic PCI-X Attribute Register                 |

|-----------|-----------------------------------------------------------|

| Table 93: | Error Diagnostic PCI-X Split Completion Message Register  |

| Table 94: | Error Diagnostic PCI/X Attributes Register                |

| Table 95: | Inbound Translation Starting Address Upper (0-7) Register |

| Table 96: | Inbound Translation Starting Address Upper (0-7) Register |

| Table 97: | Inbound Translation Ending Address Upper (0-7) Register   |

| Table 98: | Inbound Translation Ending Address Lower (0-7) Register   |

| Table 99: | Inbound Translation Offset Upper (0-7) Register           |

| Table 100 | Inbound Translation Offset Lower (0-7) Register           |

| Table 101 | Inbound Translation Attribute (0-7) Register              |

| Table 102 | Virtual FIFO Size                                         |

| Table 103 | 2eSST Mode                                                |

| Table 104 | VMEbus Address Space                                      |

| Table 105 | GCSR Base Address Upper Register                          |

| Table 106 | GCSR Base Address Lower (0-7) Register                    |

| Table 107 | GCSR Attribute Register                                   |

| Table 108 | VMEbus Address Space                                      |

| Table 109 | CRG Base Address Upper Register                           |

| Table 110 | CRG Base Address Lower Register                           |

| Table 111 | CRG Attribute Register                                    |

| Table 112 | VMEbus Address Space                                      |

| Table 113 | CR/CSR Offset Upper Register                              |

| Table 114 | CR/CSR Offset Lower Register                              |

| Table 115 | CRG Attribute Register                                    |

| Table 116 | Location Monitor Base Address Upper Register              |

| Table 117 | Location Monitor Base Address Lower Register              |

| Table 118 | Location Monitor Register                                 |

| Table 119 | VMEbus Address Space                                      |

| Table 120 | 64-bit Counter Upper Register                             |

| Table 121 | 64-bit Counter Lower Register                             |

| Table 122 | Broadcast Pulse Generator Timer Register                  |

| Table 123 | Broadcast Programmable Clock Timer Register               |

| Table 124 | VMEbus Interrupt Control Register                         |

| Table 125: Counter Source                                       | 311 |

|-----------------------------------------------------------------|-----|

| Table 126: Edge Interrupt Source                                | 311 |

| Table 127: VMEbus IRQ[1]O Function                              | 311 |

| Table 128: VMEbus IRQ[2]O Function                              | 312 |

| Table 129: Interrupt Enable Register                            | 313 |

| Table 130: Interrupt Enable Out Register                        | 318 |

| Table 131: Interrupt Status Register                            | 321 |

| Table 132: Interrupt Clear Register.                            | 324 |

| Table 133: Interrupt Map 1 Register                             | 327 |

| Table 134: Interrupt Map 2 Register                             | 329 |

| Table 135: DMA Control (0-1) Register.                          | 331 |

| Table 136: DCTL BKS Encoding                                    | 333 |

| Table 137: DCTL VBOT Encoding                                   | 334 |

| Table 138: DCTL PBKS Encoding.                                  | 334 |

| Table 139: DCTL PBOT Encoding.                                  | 335 |

| Table 140: DMA Status (0-1) Register                            | 336 |

| Table 141: DSTA ERT Encoding                                    | 338 |

| Table 142: DMA Current Source Address Upper (0-1) Register      | 339 |

| Table 143: DMA Current Source Address Lower (0-1) Register      | 340 |

| Table 144: DMA Current Destination Address Upper (0-1) Register | 341 |

| Table 145: DMA Current Destination Address Lower (0-1) Register | 342 |

| Table 146: DMA Current Link Address Upper (0-1) Register        | 343 |

| Table 147: DMA Current Link Address Lower (0-1) Register.       | 344 |

| Table 148: DMA Source Address Upper (0-1) Register.             | 345 |

| Table 149: DMA Source Address Lower (0-1) Register              | 346 |

| Table 150: DMA Destination Address Upper (0-1) Register         | 347 |

| Table 151: DMA Destination Address Lower (0-1) Register         | 348 |

| Table 152: DMA Source Attribute (0-1) Register                  | 349 |

| Table 153: DSAT TYP Encoding                                    | 350 |

| Table 154: 2eSST Transfer Rate                                  | 351 |

| Table 155: VMEbus Transfer Mode                                 | 351 |

| Table 156: VMEbus Data Bus Width                                | 351 |

| Table 157: VMEbus Address Mode                                  | 352 |

| , |

|---|

| , |

|   |

|   |

| ) |

|   |

|   |

|   |

| , |

| , |

|   |

| ) |

|   |

|   |

|   |

|   |

# **About this Document**

This chapter discusses general document information about the Tsi148 PCI/X-to-VME Bus Bridge User Manual. The following topics are described:

- "Document Conventions" on page 23

- "Revision History" on page 26

- "Related Information" on page 28

## **Document Conventions**

This section explains the document conventions used in this manual.

#### **Non-differential Signal Notation**

Non-differential signals, such as those used by the PCI/X standard, are either active high or active low. Active low signals are defined as true (asserted) when they are at a logic low. Similarly, active high signals are defined as true at a logic high. Non-differential signals are considered asserted when active and negated when inactive, irrespective of voltage levels. For voltage levels, the use of 0 indicates a low voltage while a 1 indicates a high voltage.

Non-differential signals that assume a logic low state when asserted are followed by an underscore sign as the last non-numerical character, "\_". For example, SIGNAL\_[0] is asserted low to indicate an active low signal. Non-differential signals not followed by an underscore are asserted when they assume the logic high state. For example, SIGNAL[0] is asserted high to indicate an active high signal.

#### **Bit Ordering Notation**

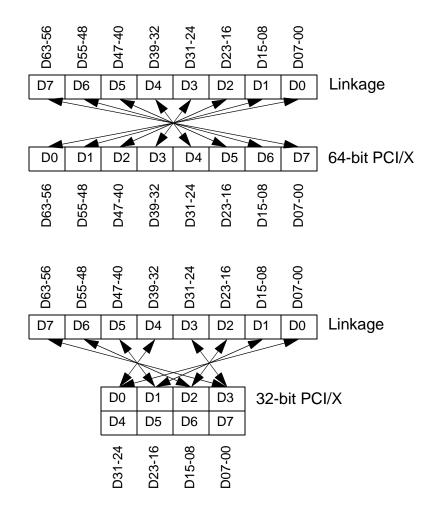

When referring to PCI/X transactions, this document assumes the most significant bit is the largest number (also known as *little-endian* bit ordering). For example, the PCI address/data bus consists of AD[31:0], where AD[31] is the most significant bit and AD[0] is the least-significant bit of the field.

Both bits and bytes have an ordering convention. The bit ordering convention for the PCI bus interface is little-endian bit ordering in which bit 0 is the least significant bit. The byte ordering convention of the PCI bus is little-endian. Byte 0 represents the least significant data bits of the word. This corresponds to the bit and byte ordering convention of the PCI bus. PCI is consistent in the bit and byte ordering.

The bit ordering convention for the VMEbus interface is little-endian bit ordering in which bit 0 is the least significant bit. The byte ordering convention is big-endian. Byte 0 represents the most significant bits of the word. This corresponds to the bit and byte ordering convention of the VMEbus. The VMEbus is not consistent in the bit and byte ordering.

## **Object Size Notation**

The following object size conventions are used for PCI/X transactions:

- A *byte* is an 8-bit object.

- A word is a 16-bit (2-byte) object.

- A *doubleword* (dword) is a 32-bit (4-byte) object.

- A *quadword* is a 64-bit (8-byte) object.

#### **Numeric Notation**

The following numeric conventions are used:

- Hexadecimal numbers are denoted by the prefix 0x. For example, 0x04.

- Binary numbers are denoted by the suffix *b*. For example, 10b.

## **Typographic Notation**

The following italic typographic conventions are used in this manual:

- Book titles: For example, PCI Local Bus Specification (Revision 2.2).

- Important terms: For example, when a device is granted access to the PCI bus it is called the *bus master*.

- Undefined values: For example, the device supports four channels depending on the setting of the PCI\_D*x* register.

## Terminology

The following terms are used in this manual:

• PCI/X: Refers to both the PCI and PCI-X bus. The PCI/X interface can be configured for either PCI or PCI-X operation.

## Symbols Used

The following symbols are used in this manual:

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

This symbol indicates a basic design concept or information considered helpful.

# **Revision History**

## 80A3020\_MA001\_12, Final, January

This revision of the Tsi148 PCI/X-to-VME Bus Bridge User Manual has the following change:

- The functionality of the SRESET bit was clarified in "Reset Inputs and Outputs" on page 123 and "VMEbus Control Register" on page 257

- "Power Supply Sequencing" on page 189 was updated

## 80A3020\_MA001\_11, Final, August 2008

This revision of the Tsi148 PCI/X-to-VME Bus Bridge User Manual has the following change:

• The "Junction-to-Board and Junction-to-Case Characteristics" on page 191 information was added

## 80A3020\_MA001\_10, Final, April 2008

This revision of the Tsi148 PCI/X-to-VME Bus Bridge User Manual has the following change:

- Clarifications have been made to "Resets, Clocks, and Power-up Options" on page 121

- The TRST\_ signal information was updated in "Resets, Clocks, and Power-up Options" on page 121 and "Detailed Signal Descriptions" on page 160

#### 80A3020\_MA001\_09, Final, January 2008

This revision of the Tsi148 PCI/X-to-VME Bus Bridge User Manual has the following changes:

- Clarifications have been made to "Resets, Clocks, and Power-up Options" on page 121.

- "Ordering Information" on page 391 was updated to include industrial variants.

#### 80A3020\_MA001\_08, Final, September 2006

This revision of the Tsi148 PCI/X-to-VME Bus Bridge User Manual had the following changes:

- The reset value for the SELTIMO bit in the "Command/Status Registers" on page 218 was changed from 0 to 1.

- The mechanical outline drawing in the "Package Information" on page 389 chapter was updated.

#### 80A3020\_MA001\_07, Final, March 2006

This revision of the Tsi148 PCI/X-to-VME Bus Bridge User Manual had the following changes:

- The PERRM field in the Interrupt Map 2 Register had the function description corrected from DMA0 Interrupt Map to the PCI/X Bus Error Interrupt Map (see Section 10.4.75 on page 329).

- The naming NIP bit in the DMA Source Attribute (0-1) Registers was corrected. It was previously was called the NIN bit (see Section 10.4.88 on page 349). Table 153 on page 350 was also corrected to reflect the correct NIP data pattern.

- The lead free commercial part number was added to the Ordering Information chapter (see Section D. on page 391).

# **Related Information**

The following information is useful for reference purposes when using this manual:

| American National Standard for<br>VME64                                            | This specification defines the VME64 hardware system<br>including the protocol, electrical, mechanical and<br>configuration specification for the VMEbus components<br>and expansion boards.                                                                           |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| American National Standard for<br>VME64 Extensions<br>(ANSI/VITA 6.1 1996 (R2003)) | This specification defines extensions to the VME64<br>standard including the protocol, electrical, mechanical<br>and configuration specification for the VMEbus<br>components and expansion boards.                                                                    |

| Source Synchronous Transfer<br>(2eSST) Standard<br>(VITA 1.5 2003)                 | This specification defines the 2eSSTincluding the protocol, electrical, and configuration specifications.                                                                                                                                                              |

| PCI Local Bus Specification<br>(Revision 2.2)                                      | This specification defines the PCI hardware system<br>including the protocol, electrical, mechanical and<br>configuration specification for the PCI local bus<br>components and expansion boards. For more<br>information, see www.pcisig.com.                         |

| PCI-X Addendum to PCI Local<br>Bus Specification (Revision 1.0b)                   | This specification addresses the need for increased<br>bandwidth of PCI Devices. PCI-X enables the design of<br>systems and devices that can operate at speeds<br>significantly higher than today's specification allows.<br>For more information, see www.pcisig.com. |

# **1. Functional Overview**

This chapter describes the main features and functions of the Tsi148<sup>™</sup>. The following topics are discussed:

- "Overview of Tsi148" on page 30

- "Tsi148 Features" on page 31

- "Tsi148 Benefits" on page 32

- "Typical Applications" on page 32

- "VMEbus Interface" on page 34

- "PCI/X Interface" on page 39

- "Linkage Module" on page 41

- "Register Overview" on page 42

- "DMA Controllers" on page 44

- "Interrupter and Interrupt Handler" on page 45

- "JTAG" on page 46

## 1.1 Overview of Tsi148

The Tundra Tsi148 device is the next generation component in our industry leading, high performance VMEbus system interconnect product family. Tsi148 is fully compliant with the 2eSST and VME64 Extension standards. This enables you to take advantage of the higher performance VME protocols, while preserving your existing investment in VME boards that implement legacy protocols.

Tsi148 increases a system's usable bus bandwidth because its local bus interface is designed for the next generation PCI/X processors and peripherals that support either a 66 MHz PCI bus or a 133 MHz PCI-X bus interface.

Tsi148 eases design constraints of VME Single Board Computers (SBCs) by requiring less board real estate and power than the previous generation of VME-to-PCI/X bridge components.

These capabilities make Tsi148 a key building block of the VME Renaissance and the development of next generation VME single board computers.

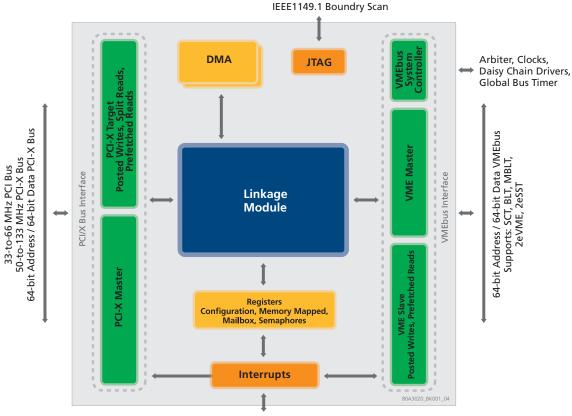

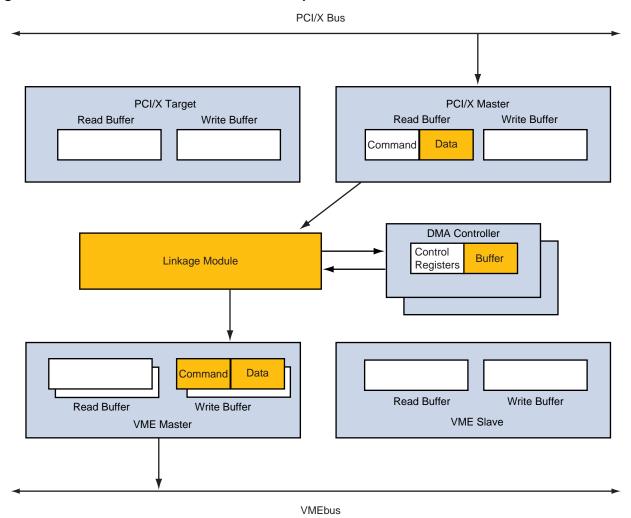

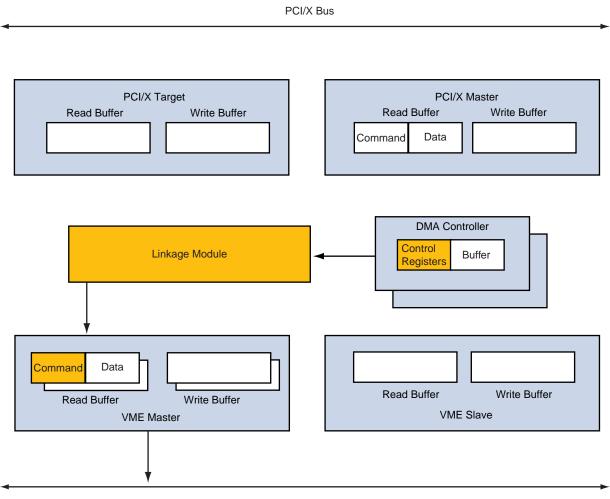

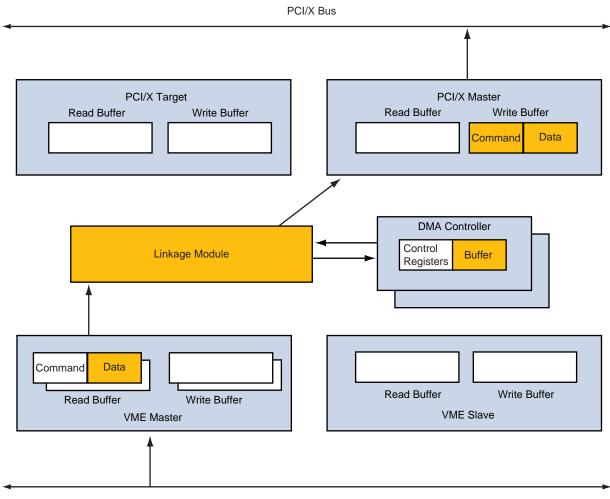

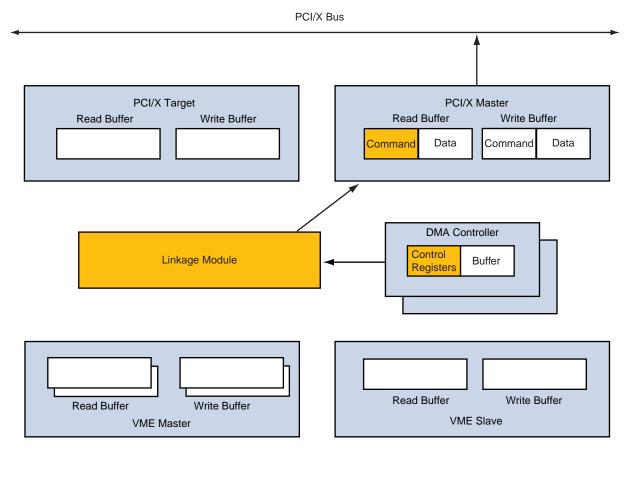

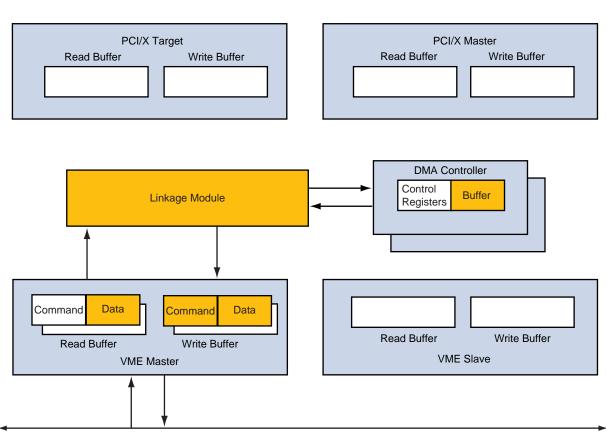

#### Figure 1: Tsi148 Block Diagram

Interrupter, Interrupt Handler

#### 1.1.1 VME Renaissance

*VME Renaissance* is a term defined by Motorola<sup>TM</sup> that describes an intense period of intellectual activity and technology infusion focused on the VMEbus. The renaissance is a period of innovation and performance improvement which maintains backwards compatibility to legacy VMEbus standards. This compatibility requirement protects existing customer investments.

The VME Renaissance gives VME a faster parallel backplane interconnect, a switched serial interconnect on the backplane coincident with the traditional parallel interconnect, point-to-point mezzanines on the cards and many other significant innovations.

#### 1.1.2 Tsi148 Features

Tsi148 has the following key features:

#### VMEbus Interface

- Standards supported:

- Legacy protocols to protect existing VME investment

- VME64 Extensions

- 2eVME and 2eSST protocols to bring support for higher bandwidth

- Full VMEbus system controller functionality

#### PCI/X Interface

- Fully compliant, programmable PCI or PCI-X bus interface

- Multiple modes of bus operation

- Interface can be configured as PCI-X or PCI

- PCI-X interface operates from 50-to-133 MHz

- PCI interface operates from 33-to-66 MHz

- 32-bit or 64-bit addressing and data in PCI and PCI-X modes

#### **Other Features**

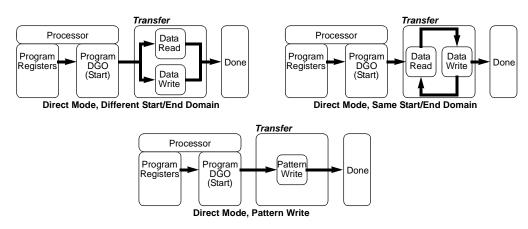

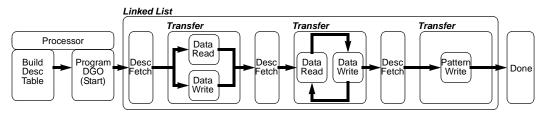

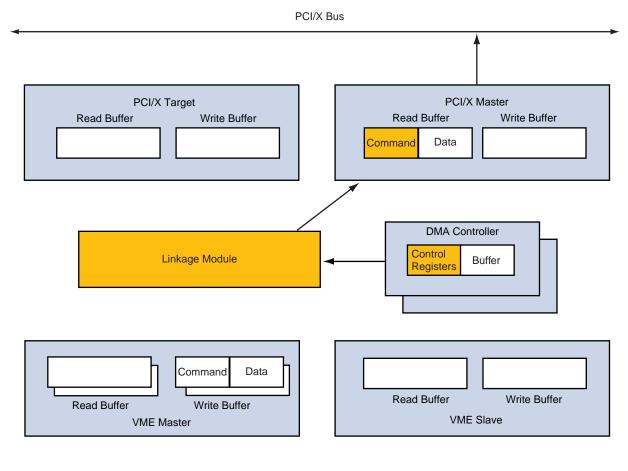

- Two, programmable DMA controllers with Direct mode and Linked-List mode support

- Interrupt and interrupt handling capability

- Flexible register set; programmable from both PCI/X and VMEbus

- IEEE 1149.1 Interface

- 456 PBGA package, 1.0 mm ball pitch

#### 1.1.3 Tsi148 Benefits

Tsi148 offers the following benefits to designers:

- Increased bandwidth

- 8*x* increase in usable system bus bandwidth over current solutions

- Less power required than existing devices due to reduced voltages

- 3.3V I/O supply

- 1.8V Core supply

- Small device footprint

- 40% less space required than existing products

- Reliable customer support with experience supporting the VME community for the past decade.

#### 1.1.4 Typical Applications

Tsi148 is intended for VME Single Board Computers and VME I/O peripheral cards that serve the following markets:

- Telecommunications

- Industrial automation

- Medical

- Military

- Aerospace

#### 1.1.4.1 Typical Application — Single Board Computers

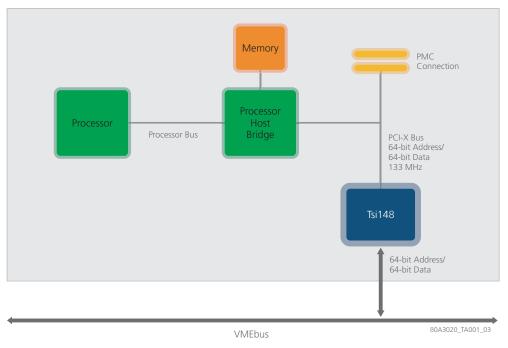

The Tsi148 can be used on VME-based Single Board Computers (SBC) that employ PCI/X as their local bus and VME as the backplane bus, as shown in the accompanying diagram. These SBC cards support a variety of applications including telecommunications, datacommunications, medical, industrial automation, and military equipment.

The Tsi148 high performance architecture seamlessly bridges the PCI/X and VME busses, and is the VME industry's standard for single board computer interconnect device.

Figure 2: Typical Application — Tsi148 In Single Board Computer Application

## 1.2 VMEbus Interface

The Tsi148 VMEbus Interface is compliant with the following standards:

- American National Standard for VME64 (ANSI/VITA 1.0 1994 (R2002))

- American National Standard for VME64 Extensions (ANSI/VITA 1.1 1997)

- Source Synchronous Transfer (2eSST) Standard

For more information on the VME Interface refer to Section 2. on page 47.

#### 1.2.1 2eVME Protocol

The 2eVME protocol doubles the VME64 peak block data rate to 160 Mbytes/s by utilizing both edges of the DS\* signal and the DTACK signal to validate data. The addressing phase of the transaction also differs from VME64 transactions because the address broadcast is split into three phases. The three phase address broadcast transmits extended AM codes (programmable limit of 256 codes), VME master information, and the transaction beat count.

The 2eVME protocol doubles peak block data rate and has flexibility in transaction terminations. The following terminations of transactions are allowed in 2eVME:

- Master termination: Before the beat count expires

- Slave terminated transactions: Using the RETRY\* and BERR\* signals

- Slave suspended terminations: Using the RETRY\* and DTACK\* signals

Refer to the *American National Standard for VME64 Extensions* for more information on the 2eVME protocol.

## 1.2.2 2eSST Protocol

The 2eSST protocol further increases VME transaction bandwidth with programmable transfer rates of 160, 267, and 320 Mbytes/s.

Although the 2eSST protocol is similar to the 2eVME protocol there are a number of differences and specific requirements for 2eSST protocol. Transactions are source synchronous in 2eSST; there is no acknowledgement from receiver of the data. This lack of acknowledgement enables transactions to happen at a faster rate; there are no delays caused by multiple acknowledgements as in the original VME standard.

Performance enhancements delivered by 2eSST require careful management of system-wide skew. 2eSST protocol implementation is possible on standard VME64x five row backplanes with Texas Instrument's high performance bus transceivers

Refer to the *Source Synchronous Transfer (2eSST) Standard* for more information on the 2eSST protocol.

#### 1.2.3 VME Slave

The Tsi148 VME Slave accepts most of the addressing and data transfer modes documented in the VME64 Specification, the VME64x Specification, and Source Synchronous Transfer (2eSST) Standard specification. The supported transactions include:

- Address: A16, A24, A32, and A64

- Data: D8, D16, and D32 Single Cycle Transaction (SCT)

- Data: D8, D16, D32 Block Transaction (BLT)

- Data: D64 Multiple Block Transaction (MBLT)

- Data: D64 2eVME

- Data: D64 2eSST

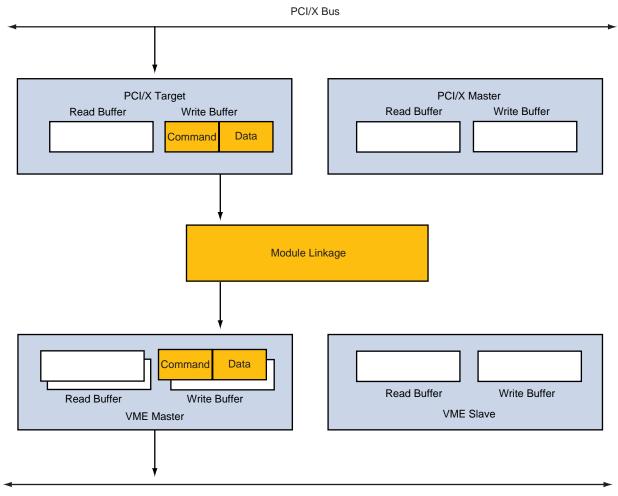

Incoming write transactions from the VMEbus are posted. With posted write transactions, data is written to a VME Slave write buffer. The VME Slave write buffer is a 4 Kbyte buffer. When the Tsi148 VME Slave accepts a write request, the initiating VMEbus master receives a data acknowledgment from Tsi148. Write data is transferred from the VME Slave write buffer, through the internal Linkage Module, to the PCI/X Master write buffer without involving the initiating VMEbus master. Refer to Section 2.2.1 on page 48 for a detailed description of transaction flow and buffer usage in Tsi148.

The VME Slave read operations depend on whether the transfer is a SCT or BLT transfer. If the transfer is a SCT transfer, the VME Slave requests a single beat transfer from the Linkage Module (see Section 1.4 on page 41). A PCI/X prefetched read is initiated when a VMEbus master initiates a block read (BLT, MBLT, 2eVME, or 2eSST) transaction on the VMEbus. When the Tsi148 PCI/X Master receives a read request (after theVME Slave sends the read request requirements through the Linkage Module), the PCI/X Master fills its read buffer by issuing burst requests to the PCI/X bus target.

The VME Slave read buffer is a 2 Kbyte read buffer with a programmable size and refill threshold. The design enables the initiating VMEbus master to acquire its block read data from the VME Slave (after the PCI/X Master has transferred the data through the Linkage Module to the VME Slave) instead of directly from the PCI/X resources. Refer to Section 2.5 on page 79 for a detailed description of transaction flow and buffer usage in Tsi148.

#### 1.2.3.1 Features Not Supported

The following features are not supported by the Tsi148 VME Slave:

- A40 address modes

- D32 MBLT transfers

- VMEbus Lock commands

- RMW cycles are not guaranteed indivisible on the PCI bus

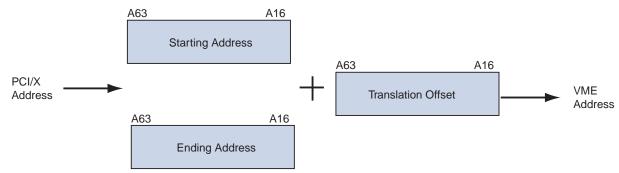

#### 1.2.4 VME Master

The Tsi148 is VME Master when the VME Master is internally requested by the Linkage Module to service the PCI/X Target, DMA, or Interrupts. The internal Linkage Module arbitrates requests for each interface. Refer to Section 1.4 on page 41 for more information on the Linkage Module.

The Tsi148's VME Master can generate the following addressing and data transfer modes:

- Address: A16, A24, A32, and A64

- Data: D8, D16, and D32 Single Cycle Transaction (SCT)

- Data: D16, D32 Block Transaction (BLT)

- Data: D64 Multiple Block Transaction (MBLT)

- Data: D64 2eVME

- Data: D64 2eSST

As VME Master, Tsi148 supports Read-Modify-Write (RMW) generation, and RETRY\* as a termination from the external VMEbus slave.

Refer to the *American National Standard for VME64 Extensions* for more information on the RETRY\* signal.

The VME Master has two 4 Kbyte posted write buffers and two 4 Kbyte prefetch read buffers. These buffers enable the VME Master to buffer two read or write transactions simultaneously.

Tsi148 provides several mechanisms to control VMEbus usage, including: time-on timer, time-off timer, and additional release mode control (see Section 2. on page 47).

#### 1.2.4.1 Features Not Supported

The following features are not supported by the Tsi148 VME Master:

- A40 address modes

- D32 MBLT transfers

• VMEbus lock commands

### 1.2.5 Tsi148 as a VMEbus System Controller

The Tsi148 supports the following VMEbus system controller functions:

- VMEbus Arbiter with three modes of programmable arbitration:

- Priority (PRI)

- Round-Robin-Select (RRS)

- Single Level (SGL)

- IACK Daisy-Chain Driver

- SYSRESET Driver: Provides a global system reset

- Global VMEbus Timer: Monitors the VMEbus and generates a BERR\_ when there is no VMEbus activity for the programmed value

- System Clock Driver: Generates a 16 MHz system clock

#### 1.2.5.1 Arbiter

The Tsi148 VMEbus arbiter is programmable. All three of the following arbitration modes defined by the VMEbus standard are supported:

- Priority (PRI)

- Round-Robin-Select (RRS)

- Single Level (SGL)

A 16 us arbitration timer is included in the Tsi148 to prevent a bus lock-up from occurring when no requester assumes mastership of the bus after the arbiter has issued a grant. This timer can be enabled or disabled in the VMEbus Control and Status Register (see Section 10.4.34 on page 257).

#### 1.2.5.2 IACK Daisy-Chain Driver

An IACK Daisy-Chain driver is included in the Tsi148 as part of the system controller functionality. This feature ensures that the timing requirements for starting the IACK Daisy-Chain are satisfied.

#### 1.2.5.3 SYSRESET Driver

A SYSRESET driver is included in the Tsi148 to provide a global system reset. The SRSTO signal is asserted in the following cases: the LSRSTI\_ pin is asserted, the SRESET bit is asserted in the VMEbus Control Status Register, or the PURSTI\_ pin is asserted. The SRSTO signal is always asserted for at least 200 ms. SRSTO is normally connected to the VMEbus SYSRESET\_ signal through an inverting open collector buffer.

#### 1.2.5.4 Global VMEbus Timer

The Tsi148 has a VMEbus global timer that monitors VMEbus cycles and generates a BERR signal when there is no VMEbus slave response for the programmed time period. The global timer only monitors VMEbus cycles when the system controller function is enabled. The global timer is compatible with SCT, BLT, MBLT, 2eVME, and 2eSST transfers. The global time-out period can be programmed for 8, 16, 32, 64, 128, 256, 512  $\mu$ s. This timer can be enabled or disabled in the VMEbus Control and Status Register (see Section 10.4.34 on page 257).

#### 1.2.5.5 System Clock Driver

Tsi148 generates the system clock (SYSCLK) signal when it is configured as the system controller. The SYSCLK signal is in spec for the following PCI/X clock frequencies: 33.3, 66.6, 100, or 133 MHz. The SYSCLK pin is connected through an external driver to the VMEbus. SYSCLK operates at 16 MHz. The external driver is enabled through the SCON pin (see Section 8.4.2 on page 161).

#### 1.2.5.6 Configuration

The system controller functions can be configured at power-up. The system controller functionality can be enabled or disabled, or the auto system controller (SCON) function can be used. The auto SCON function automatically enables the system controller functions when the board is installed in slot 1. Table 10 on page 135 shows the different signal combinations that enable or disable the SCON functionality.

## 1.3 PCI/X Interface

The Tsi148 PCI/X Interface can operate either in PCI mode or PCI-X mode. The PCI interface is compliant with the *PCI Local Bus Specification (Revision 2.2)*, while the PCI-X interface is compliant with the *PCI-X Addendum to PCI Local Bus Specification (Revision 1.0b)*

The term *PCI/X* refers to functionality that applies to both PCI and PCI-X operating modes.

The PCI mode can operate at 33 to 66 MHz and has 32-bit/64-bit addressing and data capability. The PCI-X mode can operate at 50 to 133 MHz and has 32-bit/64-bit addressing and data capability.

For more information on the PCI/X Interface refer to Section 3. on page 71.

### 1.3.1 PCI/X Target

The PCI and PCI-X targets are described separately in the following sections because they respond differently to read requests and use different buffering techniques for read transactions.

#### 1.3.1.1 PCI Target

Read transactions from the PCI bus are always processed as delayed transactions. The PCI Target has a 4 Kbyte read buffer, however, in conventional PCI mode a maximum of 512 bytes are used for storing prefetched data. When processing a read request the requesting PCI bus master is issued a retry from the Tsi148 PCI Target. The read request is then forwarded to the Linkage Module and then to the Tsi148 VME Master to be serviced. One delayed read is supported by the PCI Target.

During write transactions, the PCI Target posts write data in its write buffer. The write buffer consists of a 40 entry command queue and a 4 Kbyte data queue. Tsi148 issues the initiating PCI bus master immediate acknowledgement upon the write completing. Once the posted write completes on PCI, Tsi148 obtains the VMEbus and writes the data to the VMEbus resource independent of the initiating PCI master.

For more information on buffer structure and data flow in Tsi148 refer to Section 3. on page 71.

#### 1.3.1.2 Features Not Supported

The following features are not supported by the Tsi148 PCI Target:

- No response to PCI I/O transfers

- PCI/X LOCK\_ signal

— Message signalled interrupts

#### 1.3.1.3 PCI-X Target

Read transactions from the PCI-X bus are always processed as split transactions. The PCI-X Target has a 4 Kbyte read buffer used for storing prefetched data. The requesting external PCI-X master is issued a split response from the Tsi148 PCI-X Target. The PCI-X Target supports up to six split read transactions.

Prefetching is based on the byte count received by the Tsi148 PCI-X Target.

When the read data has been retrieved from the VMEbus and sent to the PCI-X Target's read buffer, Tsi148 issues a split completion on the PCI-X bus and transfers the data from the PCI-X Target's read data buffer to the original master.

During write transactions, the PCI-X Target posts write data in its write buffer. The write buffer consists of a 40 entry command queue and a 4 Kbyte data queue. Tsi148 issues the initiating PCI bus master immediate acknowledgement upon the write completing. Once the posted write completes on PCI-X, Tsi148 obtains the VMEbus and writes the data to the VMEbus resource independent of the initiating PCI-X master.

#### 1.3.1.4 Features Not Supported

The following features are not supported by the Tsi148 PCI-X Target:

- No response to PCI-X I/O transfers

- PCI/X LOCK\_ signal

- Message signalled interrupts

#### 1.3.2 PCI/X Master

Tsi148 requests PCI/X ownership when the PCI/X Master is internally requested by Linkage Module to service the VME Slave or the DMA controllers.

The PCI/X Master has a 4 Kbyte read buffer and 4 Kbyte write buffer.

The size of the read buffer is dependent on what PCI/X mode (PCI or PCI-X) is used in the system (see Section 1.3.1.1 on page 39).