# **PPMC-280** Installation Guide

P/N 221086 Revision AA October 2003

## Copyright

The information in this publication is subject to change without notice. Force Computers reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers shall not be liable for technical or editorial errors or omissions contained herein, nor for indirect, special, incidental, or consequential damages resulting from the furnishing, performance, or use of this material. This information is provided "as is" and Force Computers expressly disclaims any and all warranties, express, implied, statutory, or otherwise, including without limitation, any express, statutory, or implied warranty of merchantability, fitness for a particular purpose, or non-infringement.

This publication contains information protected by copyright. This publication shall not be reproduced, transmitted, or stored in a retrieval system, nor its contents used for any purpose, without the prior written consent of Force Computers.

Force Computers assumes no responsibility for the use of any circuitry other than circuitry that is part of a product of Force Computers. Force Computers does not convey to the purchaser of the product described herein any license under the patent rights of Force Computers nor the rights of others.

Copyright" 2003 by Force Computers. All rights reserved.

The Force logo is a trademark of Force Computers.

IEEE is a registered trademark of the Institute for Electrical and Electronics Engineers, Inc. PICMG, CompactPCI, and the CompactPCI logo are registered trademarks and the PICMG logo is a trademark of the PCI Industrial Computer Manufacturer's Group.

Intel and Strata Flash are registered trademarks and the Intel logo is a trademark of the Intel Corporation. PowerPC is a registered trademark and the PowerPC logo is a trademark of International Business Machines Corporation.

Other product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

#### World Wide Web: www.forcecomputers.com

24-hour access to on-line manuals, driver updates, and application notes is provided via SMART, our SolutionsPLUS customer support program that provides current technical and services information.

## Headquarters

#### The Americas

#### **Corporate Headquarters/CA**

Force Computers 4211 Starboard Drive Fremont, CA 94538

Tel.: +1 510 624-8274 Fax: +1 510 445-6007 Email: support@fci.com

#### Europe

**Force Computers GmbH** Lilienthalstr. 15 D-85579 Neubiberg/München Germany

Tel.: +49 (89) 608 14-0 Fax: +49 (89) 609 77 93 Email: support-de@fci.com

#### Asia

**Force Computers Japan KK** Shibadaimon MF Building 4F 2-1-16 Shiba Daimon Minato-ku, Tokyo 105-0012 Japan

Tel.: +81 (03) 3437 6221 Fax: +81 (03) 3437 6223 Email: support-de@fci.com

# Contents

## **Using This Guide**

## **Other Sources of Information**

## **Safety Notes**

## 1 Introduction

| Product Overview         |      |

|--------------------------|------|

| PPMC-280 Variants        |      |

| Functional Block Diagram | 1-6  |

| Board Layout             | 1-7  |

| Standard Compliance      | 1-11 |

| Physical Specifications  |      |

1-2

| MTBF                 | 1-14   |

|----------------------|--------|

| Ordering Information | 1-15   |

| Order Numbers        | . 1-15 |

## 2 Installation

| Action Plan                            | 2-3  |

|----------------------------------------|------|

| Preparing for Installation             | 2-4  |

| Taking Antistatic Precautions          | 2-4  |

| Unpacking Kit Contents                 |      |

| Checking Kit Contents                  | 2-5  |

| Physical Requirements                  | 2-5  |

| Carrier Card Requirements              | 2-6  |

| Power Requirements                     | 2-8  |

| Environmental Requirements             | 2-9  |

| Thermal Requirements                   | 2-10 |

| PPMC-280 Installation on K2 Test Card2 | 16   |

| Installing PPMC-280                    | 2-16 |

| Removal Procedure                      | -19  |

| Board Power Up and Initialization      | :-20 |

## **3** Devices and Other Functions

| On-Board Devices                                                                                    | 3-3               |

|-----------------------------------------------------------------------------------------------------|-------------------|

| Central Processing Unit                                                                             |                   |

| Boot Modes<br>BOOT-FLASH-BOOT MODE<br>PCI_BOOT Mode                                                 | 3-4               |

| System Controller<br>CPU Interface<br>DDR SDRAM Controller<br>PCI2.2 Interface<br>Device Controller | 3-6<br>3-6<br>3-6 |

## 4 Controls, Indicators and Connectors

| LEDs                    |

|-------------------------|

| On-Board Connectors 4-8 |

| PMC Connectors          |

## A Hardware Resources Mapping

| PPMC-280 MEMORY MAP            | A-3 |

|--------------------------------|-----|

| I <sup>2</sup> C Bus Addresses | A-4 |

| PCI Resources                  | A-4 |

| Device Bus Chip Select Mapping                   | A-4 |

|--------------------------------------------------|-----|

| External interrupt mapping to GPPs of MV64360/62 | A-5 |

| PROCESSOR PMC SIGNAL ACCESS                      | A-5 |

| ETHERNET PHY ADDRESSES                           | A-7 |

## **B** Troubleshooting

## **C** Assembly Instructions

Assembly Instructions for Transposer Card ......C-3

## D PCI Boot

| PCI BootD-3                                                           |

|-----------------------------------------------------------------------|

| Example - Steps                                                       |

| PPMC-280 in non-monarch mode (the "boot host" is assumed the monarch) |

| PPMC-280 in monarch modeD-5                                           |

## Index

## **Product Error Report**

# Tables

#### Introduction

| Table | 1 | Variants of PPMC-280                                                             | . 1-4 |

|-------|---|----------------------------------------------------------------------------------|-------|

| Table | 2 | Standard Compliance (PPMC-280 is yet to be qualified in the following standards) | 1-11  |

| Table | 3 | Physical Specifications.                                                         | 1-12  |

| Table | 4 | Ordering Information Excerpt                                                     | 1-15  |

#### Installation

| Table | 5 | Package Contents               | 2-5 |

|-------|---|--------------------------------|-----|

| Table | 6 | Power Requirement for PPMC-280 | 2-8 |

| Table | 7 | Environmental Requirements.    | 2-9 |

#### **Devices and Other Functions**

| Table 8  | List of Major Devices                              | 3-3 |

|----------|----------------------------------------------------|-----|

| Table 9  | Memory organization on PMC-280 variants            | 3-9 |

| Table 10 | Special Function Processor PMC Signals Implemented | 11  |

| Table 11 | I <sup>2</sup> C Bus Devices                       | 14  |

#### **Controls, Indicators and Connectors**

| Table 12 | LED Indications                       | . 4-5 |

|----------|---------------------------------------|-------|

| Table 13 | CR3 Function Table                    | . 4-6 |

| Table 14 | CR6 and CR7 Function Table            | . 4-7 |

| Table 15 | Link/Speed LEDs for Ethernet0         | . 4-7 |

| Table 16 | Link/Speed LEDs for Ethernet1         | . 4-7 |

| Table 17 | P4 PMC Signal Classification.         | 4-12  |

| Table 18 | Ethernet Link/Speed and Signal Status | 4-14  |

#### Hardware Resources Mapping

| Table 1<br>Table 2 | MEMORY MAP                                                   |    |

|--------------------|--------------------------------------------------------------|----|

| Table 3            | External interrupts on GPPs of MV64360/62 A                  | -5 |

| Table 4            | PPMC special signal mapping to GPPs A                        | -6 |

| Table 5            | Miscellaneous signals mapped to GPPs of MV64360/62           | -6 |

| PCI Boot           |                                                              |    |

| Table 6            | Important I <sup>2</sup> C Configuration steps for PCI boot: | -4 |

# **Figures**

#### Introduction

| Figure   | 1     | Functional Block Diagram                                                                                                                                           | 1-6 |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure   | 2     | Top Layout of PPMC-280 Showing Major Components                                                                                                                    | 1-7 |

| Figure   | 3     | Bottom Layout of PPMC-280 Showing Major Components                                                                                                                 | 1-8 |

| Figure   | 4     | Top Assembly exploded view for 120092 (variants 120093, 120791 and 120673 use t same heat sink)                                                                    |     |

| Figure   | 5     | Top assembly exploded view for 120049 (variants 120047, 120048 and 120094 use t same heat sink)                                                                    |     |

| Figure   | 6     | Extent of deviation (44 mm) from CMC component envelope specification due to the non-standard heatsink(P/N 221421) used on variants 120048, 120049, 120047, 120094 |     |

| Installa | ation |                                                                                                                                                                    |     |

| Figure   | 7     | Power-up sequencing                                                                                                                                                | 2-7 |

| Figure   | 8     | Power-down sequencing                                                                                                                                              |     |

| Figure   | 9     | Airflow and thermal characteristics for 1200482-                                                                                                                   | -11 |

|          |       |                                                                                                                                                                    |     |

| Figure 10 | Airflow and thermal characteristics for 120092, 120673.       | 2-12 |

|-----------|---------------------------------------------------------------|------|

| Figure 11 | Airflow and thermal characteristics for 120049.               | 2-13 |

| Figure 12 | Airflow and thermal characteristics for 120093, 120791.       | 2-14 |

| Figure 13 | Airflow and thermal characteristics for 120047, 120094.       | 2-15 |

| Figure 16 | Installation of PPMC-280 with Transposer Card on Carrier Card | 2-18 |

#### **Devices and Other Functions**

#### **Controls, Indicators and Connectors**

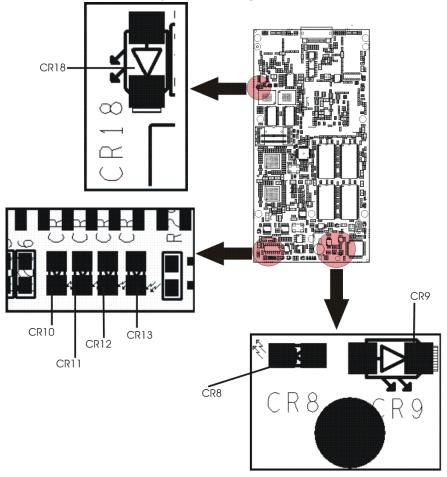

| Figure 17 | Zoomed Areas for LED Indicators CR8, CR9, CR10, CR11, CR12, |    |

|-----------|-------------------------------------------------------------|----|

|           | CR13,and CR18                                               | -3 |

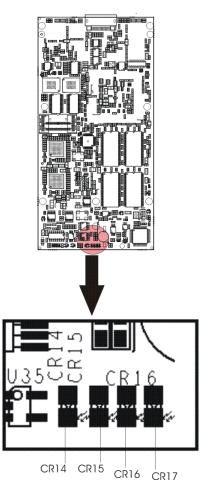

| Figure 18 | Zoomed Areas for LED Indicators CR14, CR15, CR16, CR174     | -4 |

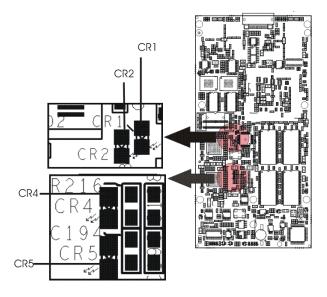

| Figure 19 | Zoomed Areas for LED Indicators CR1, CR2, CR4, and CR5 |

|-----------|--------------------------------------------------------|

| Figure 20 | Pinout of P1 PMC Connector 4-9                         |

| Figure 21 | Pinout of P2 PMC Connector 4-10                        |

| Figure 22 | Pinout of P3 PMC Connector 4-11                        |

| Figure 23 | Pinout of P4 PMC Connector 4-12                        |

#### Hardware Resources Mapping

#### Troubleshooting

#### Assembly Instructions

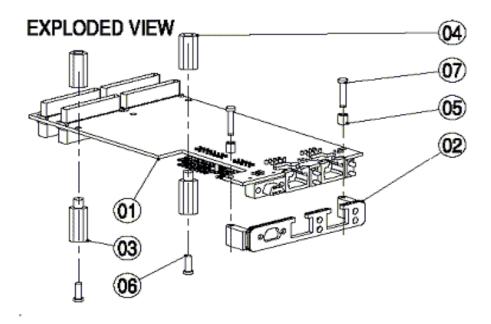

| Figure | 1 | Top Assembly of PMC 270 transposer card, exploded view | . C-3 |

|--------|---|--------------------------------------------------------|-------|

|--------|---|--------------------------------------------------------|-------|

#### PCI Boot

## **Using This Guide**

This Installation Guide explains how to install, use, and troubleshoot problems associated with PPMC-280.

This Installation Guide is intended for users qualified in electronics or electrical engineering. It is presumed that you have the pre-requisite knowledge and working experience with:

- Peripheral Component Interconnect (PCI) bus

- PCI Mezzanine Cards (PMCs)

- Processor PCI Mezzanine Cards (PPMCs)

- PowerPC

#### Conventions

| Notation      | Description                                                                                            |

|---------------|--------------------------------------------------------------------------------------------------------|

| 57            | All numbers are decimal numbers except when used with the notations described below                    |

| 0000000016    | Typical notation for hexadecimal numbers (digits are 0 through F), e.g. used for addresses and offsets |

| 00002         | Same for binary numbers (digits are 0 and 1)                                                           |

| x             | Generic use of a letter                                                                                |

| n             | Generic use of numbers                                                                                 |

| n.nn          | Decimal point indicator is signaled                                                                    |

| Bold          | Character format used to emphasize a word                                                              |

| Courier       | Character format used for on-screen output                                                             |

| Courier+Bold  | Character format used to characterize user input                                                       |

| Italics       | Character format for references, table, and figure descriptions                                        |

| <text></text> | Typical notation used for variables and keys                                                           |

| [text]        | Typical notation for buttons                                                                           |

|               | Repeated item                                                                                          |

|               | Omission of information from example/command that is not necessary at the time being                   |

|               | Ranges                                                                                                 |

| Notation       | Description                                                                             |

|----------------|-----------------------------------------------------------------------------------------|

| :              | Extents                                                                                 |

|                | Logical OR                                                                              |

| Note:          | No danger encountered. Pay attention to important information marked using this layout. |

| Caution        | Possibly dangerous situation: slight injuries to people or damage to objects possible   |

| Danger<br>STOP | Dangerous situation: injuries to people or severe damage to objects possible            |

#### Abbreviations

| BIB    | Board Information Block                             |

|--------|-----------------------------------------------------|

| BSP    | Board Support Package                               |

| CL     | CAS Latency for SDRAM                               |

| СМС    | Common Mezzanine Card                               |

| CPCI   | Compact Peripheral Component Interconnect           |

| CPLD   | Complex Programmable Logic Device                   |

| CPU    | Central Processing Unit                             |

| DDR    | Dual Data Rate                                      |

| ECC    | Error Correcting Code                               |

| EEPROM | Electrically Erasable Programmable Read-Only Memory |

| EIA    | Electronic Industries Association                   |

| EMC    | Electromagnetic compatibility                       |

| EMI    | Electromagnetic interference                        |

| ESD    | Electrostatic discharge                             |

| FAE    | Field Applications Engineer                         |

| FCC    | Federal Communications Commission                   |

|        |                                                     |

| GPP              | General Purpose Port                               |

|------------------|----------------------------------------------------|

| IC               | Integrated Circuit                                 |

| I <sup>2</sup> C | Inter-Integrated Circuit                           |

| IDMA             | Internal Direct Memory Access                      |

| IEEE             | International Electrical and Electronics Engineers |

| I <sup>2</sup> C | Inter Integrated Circuit                           |

| I/O              | Input/Output                                       |

| ISP              | In System Programmability                          |

| JTAG             | Joint Test Action Group                            |

| LED              | Light Emitting Diode                               |

| LFM              | Linear Feet per Minute                             |

| LSP              | Linux Support Package                              |

| MAC              | Message Authentication Code/Media Access Control   |

| MTBF             | Mean Time Between Failures                         |

| NMI              | Non-Maskable Interrupt                             |

| NVRAM            | Non-Volatile Random Access Memory                  |

| PCB              | Printed Circuit Board                              |

| PBGA             | Plastic Ball Grid Array                            |

| PCI              | Peripheral Component Interconnect                  |

| РМС              | PCI Mezzanine Card                                 |

| PPMC             | Processor PCI Mezzanine Card                       |

| RefDes           | Reference Designator                               |

| RTC              | Real Time Clock                                    |

| R/W              | Read/Write                                         |

| SDMA             | Serial DMA                                         |

| SDRAM            | Synchronous Dynamic Random Access Memory           |

| SMI              | Serial Management Interface                        |

| SMP              | Symmetric Multi-Processing                         |

| SRAM             | Static Random Access Memory                        |

| TFTP             | Trivial File Transfer Protocol                     |

| TSOP | Thin Small Outline Package                  |

|------|---------------------------------------------|

| UART | Universal Asynchronous Receiver Transmitter |

| UL   | Underwriters Laboratories Inc.®             |

| VITA | VMEBus International Trade Association      |

| Y2K  | Year 2000                                   |

|      |                                             |

## **Revision History**

| Order Number   | Revision | Date         | Description     |

|----------------|----------|--------------|-----------------|

| 221086 420 000 | AA       | October 2003 | Initial Release |

### **Other Sources of Information**

| Company                                       | Web Address      | Document                                                                                           |

|-----------------------------------------------|------------------|----------------------------------------------------------------------------------------------------|

| Motorola                                      | www.motorola.com | PowerPC MPC7450 RISC<br>Microprocessor Familiy user manual<br>, 10/2002, Revision 2.2              |

|                                               |                  | RISCWatch Debugger for PowerPC Processors                                                          |

|                                               |                  | PowerPC MPC7457 RISC<br>Microprocessor Hardware<br>specification, 7/2003, Revision 2               |

| Philips Semiconductors                        | www.philips.com  | I <sup>2</sup> C bus specification, Version 2.1, January 2000                                      |

| Marvell Technology                            |                  | MV64360/1/2 system controller for<br>PowerPC Processors-datasheet,<br>Revision B, January 13, 2003 |

| Broadcom <sup>©</sup> Corporation             | www.broadcom.com | BCM5421 Datasheet                                                                                  |

| JEDEC Solid State Tech-<br>nology Association |                  | Double Data Rate (DDR) SDRAM specification, JESD79, June 2000                                      |

For further information refer to the following documents:

In addition, refer the following documents:

- Processor PMC Standard, VITA32-2003, Revision 1.0a, April 2003: VITA Standards Organization

- Draft Standard Physical and Environmental Layers for PCI Mezzanine Cards: PMC, P1386.1/Draft2.4, January 12, 2001: IEEE

- Draft Standard Physical and Environmental Layers for a Common Mezzanine Card: CMC, P1386/Draft2.4a, March 21, 2001: IEEE

- PCI Local Bus Specification, Revision 2.2, June 8, 1998: PCI Special Interest Group

## **Safety Notes**

This section provides safety precautions to follow when installing, operating, and maintaining PPMC-280.

We intend to provide all necessary information to install and handle PPMC-280 in this Installation Guide. However, as the product is complex and its usage manifold, we do not guarantee that the given information is complete. If you need additional information, ask your Force Computers representative.

PPMC-280 has been designed to meet the standard industrial safety requirements. It must only be used in its specific area of office telecommunication industry and industrial control.

**PPMC-280** is intended for use with a UL listed chassis that has adequate instructions on installation of PMC accessories.

Only personnel trained by Force Computers or persons qualified in electronics or electrical engineering are authorized to install, maintain, and operate PPMC-280. The information given in this manual is meant to complete the knowledge of a specialist and must not be taken as replacement for qualified personnel.

#### EMI

The EMI limits are designed to provide reasonable protection against harmful interference when the board is operated in a commercial, business, or industrial environment.

The board generates and uses radio frequency energy. If not installed properly and used in accordance with this Installation Guide, the board may cause harmful interference to radio communications. Operating the board in a residential area is likely to cause harmful interference, in which case, users will be required to correct the interference at their own expense.

#### ESD

**PPMC-280** contains very delicate Integrated Circuit (IC) chips. To protect them against damage from Electrostatic Discharge (ESD), follow the described precautions:

Ground yourself properly before removing the board from the antistatic bag

- Use a grounded wrist strap before handling system components. If you do not have one, touch both hands to a safely grounded object or to a metal object such as the system case

- Hold the board by its edges and do not touch the components, IC chips, connectors and leads

Whenever components are separated from the system, place components on a grounded antistatic pad or the original packaging bag

#### Installation

Electrostatic discharge and incorrect board installation and removal can damage circuits or shorten their life. Therefore:

- Before installing or removing the board, read "Action Plan" page 2-3

- Before touching boards or electronic components, make sure that you are working in an ESD-safe environment.

- Before installing or removing an additional device or module, read the respective documents.

#### Operation

While operating the board, ensure that the environmental and power requirements are met.

Do not operate the product outside the specified environmental limits. High humidity and condensation may cause short circuits. Make sure the product is completely dry and there is no moisture on any surface before applying power. Do not operate the product below 0°C.

When operating the board in areas of electromagnetic radiation, ensure that the board is bolted on the carrier card and the system is shielded by enclosure.

Make sure that contacts and cables of the board cannot be touched while the board is operating.

#### **Replacement/Expansion**

Only replace or expand components or system parts with those recommended by Force Computers. Otherwise, you are fully responsible for the impact on EMC and the possibly changed functionality of the product.

Check the total power consumption of all components installed (see the technical specification of the respective components). Ensure that any individual

output current of any source stays within its acceptable limits (see the technical specification of the respective source).

#### Environment

Always dispose off old boards according to your country's legislation, if possible, in an environmentally acceptable way.

#

# Introduction

## **Product Overview**

PPMC-280 is a Processor PMC (PPMC) dual-processing card based on the MPC7447 PowerPC and MV64360 system controller.

The standard variant of PPMC-280 (120092) supports the following features. For features supported by other variants, refer to Table 1 "Variants of PPMC-280" page 1-4.

- Dual Motorola PowerPC<sup>®</sup> MPC7447 processors

- 1GHz core CPU frequency

- 133 MHz front-side bus

- Marvell Atlantis MV64360 System Controller

- 512 MB Dual Data Rate (DDR) Synchronous Dynamic Random Access Memory (SDRAM)

- 133 MHz bus frequency (266 MHz data rate)

- Flash

- 64 MB user-programmable flash

- PCI2.2 interface

- Universal signaling

- 64-bit, 66 MHz

- Two Gigabit Ethernet ports accessible through the PMC I/O P4 Connector

- Two RS-232 Serial Ports accessible through the PMC I/O P4 Connector

In addition, PPMC-280 also provides a Y2K-compliant Real Time Clock (RTC) and serial EEPROMs for board configuration and identification.

#### **PPMC-280** Variants

The PPMC-280 variant information is detailed in the table given in the following page.

| Features               | Description                                                                                               | Variant<br>120092   | Variant<br>120048 | Variant<br>120047   | Variant<br>120049   | Variant<br>120093   | Variant<br>120094 | Variant<br>120791   | Variant<br>120673   |

|------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|-------------------|---------------------|---------------------|---------------------|-------------------|---------------------|---------------------|

| CPU(s)                 | MPC7447<br>PowerPC                                                                                        | Dual                | Dual              | Single              | Single              | Single              | Single            | Single              | Dual                |

| Core speed             | CPU core fre-<br>quency                                                                                   | 1 GHz               | 1 GHz             | 733<br>MHz          | 1 GHz               | 1 GHz               | 733<br>MHz        | 1 GHz               | 1GHz                |

| System Con-<br>troller | Marvell Dis-<br>covery -II<br>MV6436X                                                                     | MV643<br>60         | MV643<br>62       | MV6436<br>0         | MV6436<br>0         | MV643<br>60         | MV643<br>62       | MV643<br>60         | MV643<br>60         |

| FSB Speed              | Frequency of<br>the front-<br>side/host bus                                                               | 133<br>MHz          | 133<br>MHz        | 133<br>MHz          | 133<br>MHz          | 133<br>MHz          | 133<br>MHz        | 133<br>MHz          | 133<br>MHz          |

| Memory                 | On-board<br>DDR266<br>SDRAM with<br>ECC                                                                   | 512 MB              | 512 MB            | 512 MB              | 1 GB                | 512 MB              | 128 MB            | 256 MB              | 1 GB                |

| Flash Mem-<br>ory      | On-board user<br>flash (Intel<br>Strata Flash)                                                            | 64 MB               | None              | 64 MB               | 64 MB               | 64 MB               | None              | None                | 64 MB               |

|                        | 1 MB boot flash                                                                                           | Yes                 | No                | Yes                 | Yes                 | Yes                 | Yes               | Yes                 | Yes                 |

| PCI2.2 Inter-<br>face  | 3.3V/5V, 64-<br>bit, 66 MHz<br>interface                                                                  | Yes                 | Yes               | Yes                 | Yes                 | Yes                 | Yes               | Yes                 | Yes                 |

| Ethernets              | Gigabit ports<br>accessible<br>through PMC<br>P4                                                          | Two<br>(GbE0,<br>1) | One<br>(GbE0)     | Two<br>(GbE0,<br>1) | Two<br>(GbE0,<br>1) | Two<br>(GbE0,<br>1) | One<br>(GbE0)     | Two<br>(GbE0,<br>1) | Two<br>(GbE0,<br>1) |

| Boot Mode              | PPMC-280 can<br>boot from boot<br>flash or over<br>PCI; defualt<br>boot mode is<br>variant depen-<br>dent | Boot<br>Flash       | PCI               | Boot<br>Flash       | Boot<br>Flash       | Boot<br>Flash       | PCI               | Boot<br>Flash       | Boot<br>Flash       |

| PCI Sub-<br>system ID  | Assigned to the<br>variant by<br>Force Comput-<br>ers                                                     | 0xB283              | 0xB281            | 0xB280              | 0xB282              | 0xB284              | 0xB285            | 0xB286              | 0xB287              |

| Table 1: | Variants | of PPMC-280 |

|----------|----------|-------------|

|----------|----------|-------------|

| Features                    | Description                                                            | Variant<br>120092           | Variant<br>120048                   | Variant<br>120047                   | Variant<br>120049                   | Variant<br>120093           | Variant<br>120094                   | Variant<br>120791           | Variant<br>120673           |

|-----------------------------|------------------------------------------------------------------------|-----------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-----------------------------|

| Heat Sink                   | Standard is<br>compliant to<br>CMC mechani-<br>cal specifica-<br>tions | Standard<br>(P/N<br>221719) | Non-<br>Standard<br>(P/N<br>221421) | Non-<br>Standard<br>(P/N<br>221421) | Non-<br>Standard<br>(P/N<br>221421) | Standard<br>(P/N<br>221719) | Non-<br>Standard<br>(P/N<br>221421) | Standard<br>(P/N<br>221719) | Standard<br>(P/N<br>221719) |

| Front panel bezel           | -                                                                      | Yes                         | No                                  | No                                  | No                                  | Yes                         | No                                  | No                          | Yes                         |

| * CMC Com-<br>pliance       | Full Conform-<br>ance to CMC<br>mechanical<br>specifications           | Yes                         | No                                  | No                                  | No                                  | Yes                         | No                                  | Yes                         | No                          |

| VxWorks<br>T1.0.1           | Dual CPU =<br>Loosely Cou-<br>pled-SMP                                 | No                          | Yes                                 | No                                  | No                                  | No                          | Yes                                 | No                          | No                          |

| VxWorks<br>T2.2             | Dual CPU =<br>Loosely Cou-<br>pled-SMP                                 | Yes                         | No                                  | No                                  | No                                  | Yes                         | No                                  | Yes                         | Yes                         |

| Linux –<br>Monta<br>Vista   | Dual CPU =<br>SMP<br>Single CPU =<br>LSP                               | Yes                         | No                                  | No                                  | No                                  | Yes                         | No                                  | No                          | Yes                         |

| Linux - Ker-<br>nel.<br>Org | Dual CPU =<br>SMP<br>Single CPU =<br>LSP                               | No                          | No                                  | Yes                                 | Yes                                 | No                          | No                                  | No                          | No                          |

| Power-Boot                  | On CPU0 only                                                           | Yes                         | No                                  | Yes                                 | Yes                                 | Yes                         | No                                  | Yes                         | Yes                         |

| Table 1: | Variants of PPMC-280 |

|----------|----------------------|

|----------|----------------------|

NB: \* see "Physical Specifications" page 1-12 for details.

#### **Software Support**

PPMC-280 supports VxWorks and Linux operating systems (see "Variants of PPMC-280" page 1-4). Refer to the latest VxWorks /Tornado<sup>™</sup> BSP for PPMC-280 Installation Guide (Order Number 221087 410 000), VxWorks /Tornado<sup>™</sup> BSP for PPMC-280 Programmer's Guide (Order Number 221088 410 000) and Linux Board Support Package for PPMC-280 installation guide(Order Number 221522 410 000).

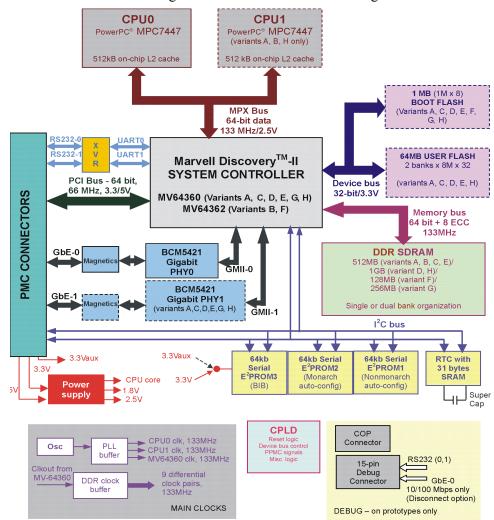

## **Functional Block Diagram**

The functional block diagram of PPMC-280 is shown in Figure 1.

**Figure 1:** Functional Block Diagram

Note: Variant A=120092; B=120048; C=120047; D=120049; E=120093; F=120094; G=120791; H=120673

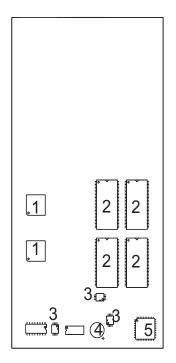

## **Board Layout**

This Installation Guide refers to two sides (top and bottom) of PPMC-280:

- You can identify bottom side by the CPU, heat-sink, Ethernet Magnetics, and PMC connectors.

- You can identify top side by Super-capacitor.

The top and bottom layout of the PPMC-280 are shown in Figure 2 and Figure 3 respectively. See figure "Controls, Indicators and Connectors" (Chapter 4) and figure "Devices and Other Functions" (Chapter 3) for detailed information.

Figure 2: Top Layout of PPMC-280 Showing Major Components

The major components numbered in Figure 2 are listed here:

- 1. Ethernet PHY

- 2. DDR SDRAMs

- 3. EEPROMs

- 4. Super-capacitor

#### 5. CPLD

The bottom layout of PPMC-280 is shown in Figure 3.

Figure 3: Bottom Layout of PPMC-280 Showing Major Components

The major components numbered in Figure 3 are listed here:

- 1. CPU 0 (On single-CPU variants 120047, 120049, and 120093, only CPU 0 is present.)

- 2. CPU 1 (On single-CPU variants 120094 and 120791, only CPU 1 is present)

- 3. User Flash

- 4. System Controller

- 5. DDR SDRAMs

- 6. Ethernet Magnetics

- 7. P1

- 8. P3

- 9. P2

- 10. P4

- 11. RTC

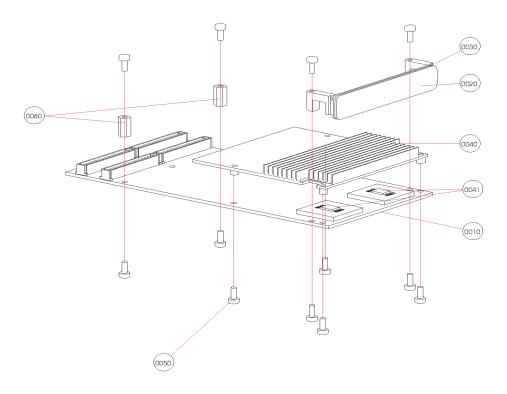

**Figure 4:** Top Assembly exploded view for 120092 (variants 120093, 120791 and 120673 use the same heat sink)

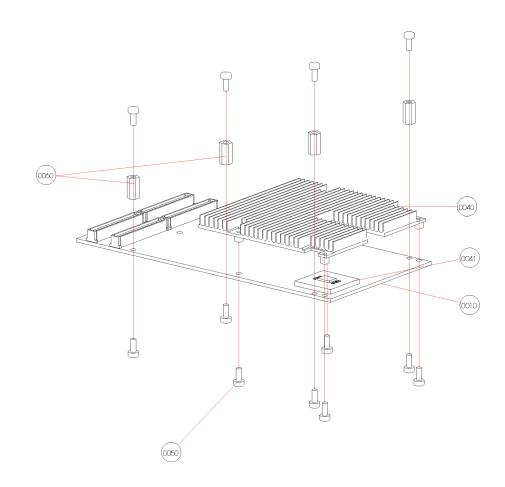

**Figure 5:** Top assembly exploded view for 120049 (variants 120047, 120048 and 120094 use the same heat sink)

## **Standard Compliance**

PPMC-280 will meet the following standards:

| Standard                                                                                                            | Description                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPC                                                                                                                 | Quality level requirements                                                                                                                                                  |

| IEC 68-2-1/2/3/13/14                                                                                                | Climatic environmental requirements.The<br>PPMC-280 can be used in a restricted<br>temperature range only.<br>See "Environmental Requirements" on page 2-<br>9 for details. |

| IEC 68-2-6/27/32                                                                                                    | Mechanical environmental requirements                                                                                                                                       |

| UL 1950 (standard CompactPCI chassis)                                                                               | Legal safety requirements                                                                                                                                                   |

| FCC Part 15, Class A                                                                                                | EMI Requirements on System Level                                                                                                                                            |

| EN 55022:1998, Class A                                                                                              | EMI Requirements on System Level                                                                                                                                            |

| EN 55024:1998<br>IEC 61000-4-2<br>IEC 61000-4-3<br>IEC 61000-4-4<br>IEC 61000-4-5<br>IEC 61000-4-6<br>IEC 61000-4-8 | EMS Requirements on System Level                                                                                                                                            |

**Table 2:** Standard Compliance (PPMC-280 is yet to be qualified in the following standards)

The features relevant to PMC/Processor PMC standards that are supported by PPMC-280 are:

- 64-bit, 66 MHz, PCI 2.2-compliant interface to an IEEE P1386.1 PMC or VITA 32-199x Draft 0.5 Processor PMC compliant carrier board

- Universal signaling PCI interface (supporting both 3.3V and 5V)

- Four 64-pin EIA E700 AAAB connectors as per the EIA standard. These PMC connectors labelled P11, P12, P13, P14 (as entailed by the CMC specification P1386) are referred to as P1, P2, P3, and P4 in this Installation Guide.

- Monarch and Non-Monarch Operating Modes

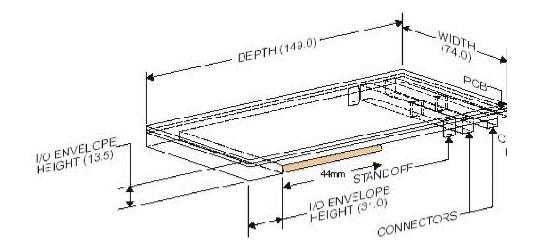

## **Physical Specifications**

| Variant# | Standoff<br>height | Total<br>height | Width | Depth | Weight | Comments                    |

|----------|--------------------|-----------------|-------|-------|--------|-----------------------------|

| 120092   | 10mm               | 13.5mm          | 74mm  | 149mm | 190g   | Includes bezel              |

| 120048   | 10mm               | 13.5mm          | 74mm  | 149mm | 220g   | Note (b)                    |

| 120047   | 15mm               | 18.5mm          | 74mm  | 149mm | 200g   | Note (b)                    |

| 120049   | 15mm               | 19.25mm         | 74mm  | 149mm | 212g   | Note (b)                    |

| 120093   | 10mm               | 13.5mm          | 74mm  | 149mm | 180g   | Includes bezel              |

| 120094   | 10mm               | 13.5mm          | 74mm  | 149mm | 210g   | Note (b)                    |

| 120791   | 10mm               | 13.5mm          | 74mm  | 149mm | 160g   | -                           |

| 120673   | 10mm               | 14.25mm         | 74mm  | 149mm | 200g   | Includes bezel;<br>Note (c) |

Table 3:

Physical Specifications

(a) "Height" is measured as the vertical distance of the top of the tallest component on the top side (CMC side-2) of the PMC card from the carrier card. Hence, it includes the standoff height, the PCB thickness and the tallest component height on the top side.

(b) Variants 120048, 120047, 120049 and 120094 do not conform to the bottom-side (CMC side-1) component height specification, because the heat sink encroaches 44 mm into the 4.7mm maximum height envelope in the component area. See Figure 6:.

(c) Variant 120673 does not conform to the top-side (CMC side-2) component height specification for a 10mm stacking height card, since it uses stacked 1Gb DDR modules.

**Figure 6:** Extent of deviation (44 mm) from CMC component envelope specification due to the nonstandard heatsink(P/N 221421) used on variants 120048, 120049, 120047, 120094.

#### **Connector Types**

PMC connectors: Four 64-pin EIA E700 AAAB connectors, current rating 1A/pin.

## MTBF

Standard conditions for MTBF calculation

- Nonmobile operation

- Ground benign Gb

- 40°C mean ambient temperature

- No fans

- Continuous operation 8760 hours per year

| Variant                         | General description             | Minimum MTBF  |

|---------------------------------|---------------------------------|---------------|

| 120092/120048/1206<br>73        | Dual-CPU variants               | 347,826 hours |

| 120093/120047/1207<br>91/120094 | Single-CPU, single-stack memory | 422,476 hours |

| 120049                          | Single-CPU, dual-stack memory   | 398,248 hours |

## **Ordering Information**

#### **Order Numbers**

When ordering PPMC-280, use the order numbers given below.

The order numbers are provided in Table 4.

Table 4:

Ordering Information Excerpt <sup>1</sup>

| Order No. | Name                    | Description                                                                                      |

|-----------|-------------------------|--------------------------------------------------------------------------------------------------|

| 120092    | PPMC-280 Variant-120092 | Dual 7447, 1GHz, 512MB,<br>64MB flash, Discovery II<br>MV64360 – 2 GigE, Boot<br>ROM boot        |

| 120048    | PPMC-280 Variant-120048 | Dual 7447, 1GHz, 512MB,<br>0MB Flash, Discovery II<br>MV64362 – 1 GigE, PCI boot                 |

| 120047    | PPMC-280 Variant-120047 | Single 7447, 733 MHz,<br>512MB, 64MB flash, Discov-<br>ery II MV64360 – 2 GigE,<br>Boot ROM boot |

| 120049    | PPMC-280 Variant-120049 | Single 7447, 1GHz, 1GB,<br>64MB Flash, Discovery II<br>MV64360 – 2 GigE, Boot<br>ROM boot        |

| 120093    | PPMC-280 Variant-120093 | Single 7447, 1GHz, 512MB,<br>64MB flash, Discovery II<br>MV64360 – 2 GigE, Boot<br>ROM boot      |

| 120094    | PPMC-280 Variant-120094 | Single 7447, 733 MHz,<br>128MB, 0MB flash, Discovery<br>II MV64362 – 1GigE, PCI<br>boot          |

| 120791    | PPMC-280 Variant-120791 | Single 7447, 1 GHz, 256 MB,<br>0 MB flash, Discovery II<br>MV64360 – 2 GigE, Boot<br>ROM boot    |

| 120673    | PPMC-280 Variant-120791 | Dual 7447, 1GHz, 1GB,<br>64MB Flash, Discovery II<br>MV64360 – 2 GigE, Boot<br>ROM boot          |

1) Status: October 2003

# 2

## Installation

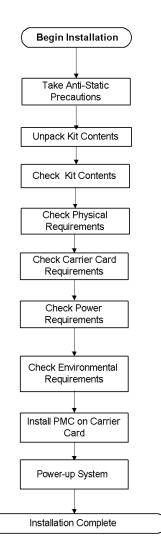

## **Action Plan**

This chapter details the installation procedure of PPMC-280 on the carrier card. To install PPMC-280 on the carrier card, follow the steps shown in the diagram below.

## **Preparing for Installation**

The following sections explain how to prepare for an installation. Topics include:

- "Taking Antistatic Precautions" on page 2-4

- "Unpacking Kit Contents" on page 2-4

- "Checking Kit Contents" on page 2-5

- "Physical Requirements" on page 2-5

- "Carrier Card Requirements" on page 2-6

- "Environmental Requirements" on page 2-9

Note: Ensure that there is adequate airflow as per the recommendations, see "Thermal Requirements" page 2-10.

#### **Taking Antistatic Precautions**

When handling circuit boards and associated internal computer components, use an antistatic wrist strap or wear isolation gloves.

In addition to using an antistatic wriststrap or wearing isolation gloves, consider the following precautions:

- Do not allow a circuit board or other components to make contact with nonconductors, including your clothing.

- Keep loose circuit boards inside or on top of conductive plastic bags.

- Before touching a loose circuit board or component, discharge static electricity.

#### **Unpacking Kit Contents**

Start preparing for your installation by unpacking the card kit.

- 1. Verify that the order numbers on labels of your kit carton match the numbers for the product you ordered. If the order numbers do not match, contact your Force Computers sales representative.

- 2. Locate and put on an antistatic wriststrap.

- 3. Clip the wire attached to the wriststrap to the frame of your system chassis.

- 4. Remove all items from the carton.

- 5. Remove hardware components from conductive plastic bags in which they were packaged, and place components on the bags.

Note: Store the original packaging material in case a factory return is necessary.

The details of the kit contents are listed in Table 5 "Package Contents" on page 2-5.

#### **Checking Kit Contents**

Table 5 lists the contents of the card kit. Verify that the material you unpacked matches contents listed in Table 5.

Table 5: Package Contents

| Part | Part Name          | Part Number/Order<br>Number                                         |

|------|--------------------|---------------------------------------------------------------------|

|      | Installation Guide | Order Number<br>221086 420 000 AA                                   |

|      | PPMC-280           | 120092/120047/<br>120048/120049/1200<br>93/120094/120791/<br>120673 |

#### **Physical Requirements**

PPMC-280 features the industry-standard PMC form-factor. The card must be placed on a carrier card.

#### **Carrier Card Requirements**

PPMC-280 is to be plugged into a carrier card that meets the following requirements:

- Carrier cards to support PPMC-280 should be compliant with the CMC/PMC standard specifications for carrier cards.

- If PPMC special signals are required, the carrier card should implement changes required by the Processor PMC specification. In order to take advantage of the special Processor PMC signals (MONARCH#, EREADY, RESETOUT#), the carrier card must support these, with a weak pull-up (5kohm) for EREADY.

- PCI clock and reset signals must be provided by the carrier card. All necessary PCI signal pull-ups should be provided by the carrier card. Since PCI arbitration is not provided by PPMC-280, another participant in the system should provide the PCI arbitration.

- If the carrier card uses the PMC I/O connector (P4), ensure that P4 is pin-compliant and voltage-compliant with the corresponding signals on PPMC-280.

- If the carrier card interfaces to the I<sup>2</sup>C bus on PPMC-280, ensure that I<sup>2</sup>C address clash is prevented.

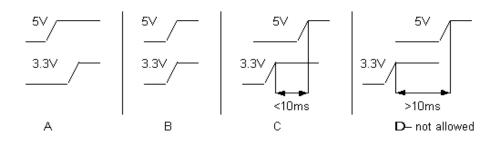

- The carrier card needs to supply 3.3V and 5V power to PPMC-280:

- Mandatory:  $3.3V \pm 5\%$

- Mandatory. $5V \pm 5\%$

- PCI reset should be asserted by the carrier card for a minimum of 200 ms after 3.3V becomes stable on power-on.

- The following power up-sequencing requirement should be met (see "Power-up sequencing" page 2-7):

- The 5V rail may power-up prior to the 3.3V rail (case A) or at the same time (case B) as the 3.3V rail. Either case A or case B is recommended.

- If the 5V rail powers up after the 3.3V rail, the time delay between the two rails powering up should not exceed 10ms (case C).

Figure 7: Power-up sequencing

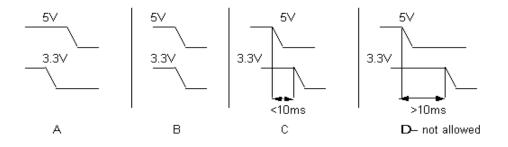

- The following power down-sequencing requirement should be met (see "Power-down sequencing" page 2-7):

- •The 5V rail may power-down after the 3.3V rail (case A) or at the same time as the 3.3V rail (case B). Either case A or case B is recommended.

- •If the 5V rail powers down before the 3.3V rail, the time delay between the two rails powering down should not exceed 10ms (case D).

Figure 8: Power-down sequencing

- The PMC connectors (receptacles) on the carrier card should have a minimum current rating of 1A/pin.

- Carrier card for 120047/120049 must use 15mm tall PMC receptacles, capable of mating properly with 10mm plugs.

Note:

- The carrier card has to supply 3.3Vaux if the BIB EEPROM has to be accessed when the main 3.3V rail is powered off.

- If you use K2 Test Card (P/N110869) as a carrier card, then the PPMC-270 Transposer card (P/N 120101) has to be used along with it. (Refer to "PPMC-280 Installation on K2 Test Card" on page 2-16).

#### **Power Requirements**

The power requirement of PPMC-280 to be supplied by the carrier card is detailed in Table 6.

| TLA#   | 3.3V<br>power | 3.3V<br>current/<br>pin | 5V<br>power | 5V<br>current/<br>pin | Measured<br>instantaneous<br>total power | Worst case<br>total power<br>(Sum of 3.3V<br>and 5V<br>power) |

|--------|---------------|-------------------------|-------------|-----------------------|------------------------------------------|---------------------------------------------------------------|

| 120092 | 23.76W        | 0.8A                    | 13.2W       | 0.44A                 | 33.79W                                   | 36.96W                                                        |

| 120093 | 16.86W        | 0.57A                   | 13.2W       | 0.44A                 | 26.86W                                   | 30.06W                                                        |

| 120048 | 23.76W        | 0.8A                    | 11.95W      | 0.4A                  | 32.54W                                   | 35.71W                                                        |

| 120047 | 15.12W        | 0.51A                   | 13.2W       | 0.44A                 | 25.12W                                   | 28.32W                                                        |

| 120049 | 16.86W        | 0.57A                   | 14.15W      | 0.47A                 | 28.51W                                   | 31.01W                                                        |

| 120094 | 15.12W        | 0.51A                   | 10.33W      | 0.34A                 | 25.45W                                   | 25.45W                                                        |

| 120791 | 16.86W        | 0.57A                   | 13.2W       | 0.44A                 | 26.86W                                   | 30.06W                                                        |

| 120673 | 23.76W        | 0.8A                    | 14.85W      | 0.5A                  | 35.44W                                   | 38.61W                                                        |

Table 6: Power Requirement for PPMC-280

(a) Measured Instantaneous Total Power indicates real power numbers where the application usually does not exercise the 3.3V and 5V power rails simultaneously to the maximum.

"Worst case total power" indicates the sum of maximum of measured 3.3V and 5V powers.

(b) Current/pin indicates the current flowing per 3.3V/5V power pin of the PMC connector. The

PMC connector is rated for 1A/pin.

(c) Carrier card designers must consider worst-case power.

(d) The 5V power numbers in the table are applicable when both ethernet ports are operating in Gigabit mode. If operating in 10/100 mode, the power reduces by 1.25W per port.

#### **Environmental Requirements**

The conditions listed below refer to the surroundings of the board within the user environment.

Note: Operating temperatures refer to the temperature of the air circulating around the board and not to the component temperature.

Do not operate the product outside the specified environmental limits. High humidity, temperature and condensation may cause short circuits. Make sure the product is completely dry and there is no moisture on any surface before applying power.

| Feature            | Operating                              | Non-Operating                      |

|--------------------|----------------------------------------|------------------------------------|

| Temperature range  | 0 to 55 <sup>0</sup> C                 | –40 ° C to 85 ° C                  |

| Temperature change | $\pm 0.5$ ° C per minute               | $\pm 1$ ° C per minut              |

| Relative humidity  | 5% to 95% at 40 ° C<br>(noncondensing) | 5% to 95% at 40<br>(noncondensing) |

|                    |                                        |                                    |

Table 7:

Environmental Requirements

|                     | · · · · · · · · · · · · · · · · · · ·                  |                                                       |

|---------------------|--------------------------------------------------------|-------------------------------------------------------|

| Temperature range   | 0 to 55 <sup>0</sup> C                                 | -40°C to 85°C                                         |

| Temperature change  | $\pm 0.5$ ° C per minute                               | ±1 ° C per minute                                     |

| Relative humidity   | 5% to 95% at 40° C<br>(noncondensing)                  | 5% to 95% at 40° C<br>(noncondensing)                 |

| Altitude            | -300m to 3000m                                         | -300m to 12000m                                       |

| Shock               | 5g/11 ms half sine                                     | 15g/11 ms half sine                                   |

| Vibration           | 10 Hz to 15 Hz: 2 mm amplitude<br>15 Hz to 150 Hz: 2 g | 10 Hz to 15 Hz: 5 mm amplitude<br>15 Hz to 150 Hz: 5g |

| Packaging free fall | 100 mm/3 axis                                          | 1200 mm/all edges and corners                         |

#### **Thermal Requirements**

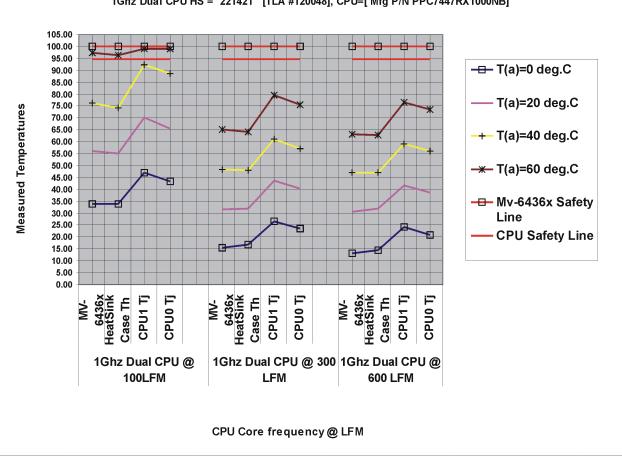

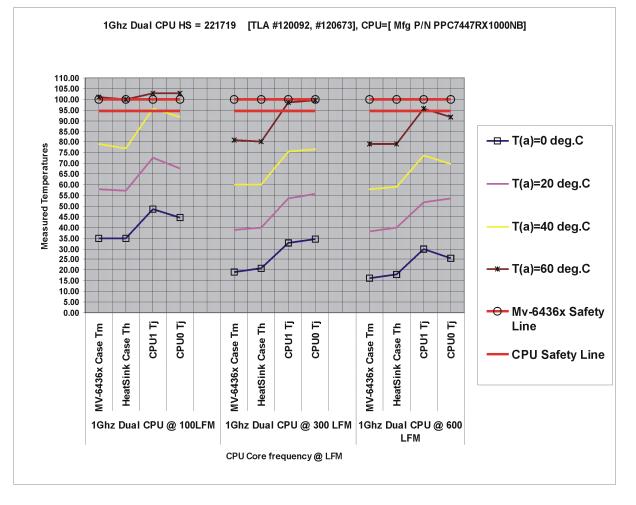

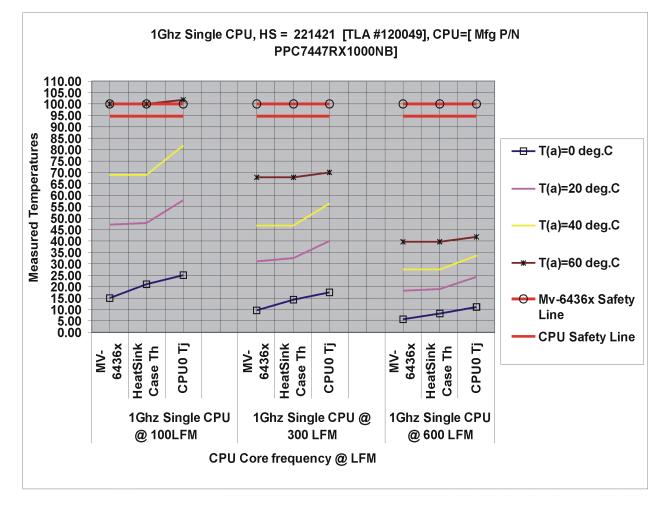

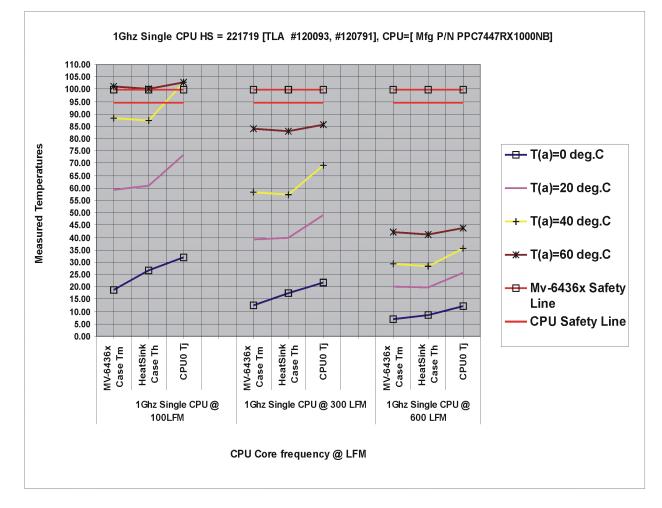

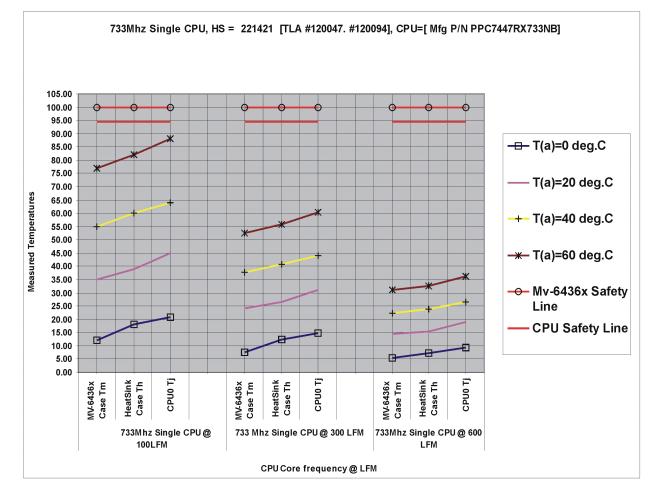

Graphs shown in figures 8 to 12 below are recommended thermal and airflow operating conditions for different variants of PPMC-280. Airflow information can be extracted if the ambient temperature and the core frequency of the CPU are known. Continuous operation of the CPU and MV6436x junctions beyond the specified safety limits shown in the graphs is not recommended.

The airflow (LFM) indicated in the graphs is assumed to be at the lateral entry point of the heat sink.

Note: Measurement conditions applicable to Figures 9-13:

- PPMC-280 is mounted on a standard CompactPCI<sup>®</sup> 6U carrier card, and the whole setup is plugged into a CompactPCI<sup>®</sup> backplane.

- The junction temperatures are extrapolated from the measured respective case temperatures and the thermal characteristics of the device.

- The "safety limit" of operation for each device is assumed 90% of the maximum specified junction temperature in the device datasheet.

- "CPU0" in the graphs for dual-CPU variants refers to the CPU that is closer to the fan.

1Ghz Dual CPU HS = 221421 [TLA #120048], CPU=[ Mfg P/N PPC7447RX1000NB]

Figure 9: Airflow and thermal characteristics for 120048.

Figure 10: Airflow and thermal characteristics for 120092, 120673.

Figure 11: Airflow and thermal characteristics for 120049.

Figure 12: Airflow and thermal characteristics for 120093, 120791.

Figure 13: Airflow and thermal characteristics for 120047, 120094.

## **PPMC-280 Installation on K2 Test Card**

Follow the steps mentioned in the section below to install PPMC-280 on K2 Test Card.

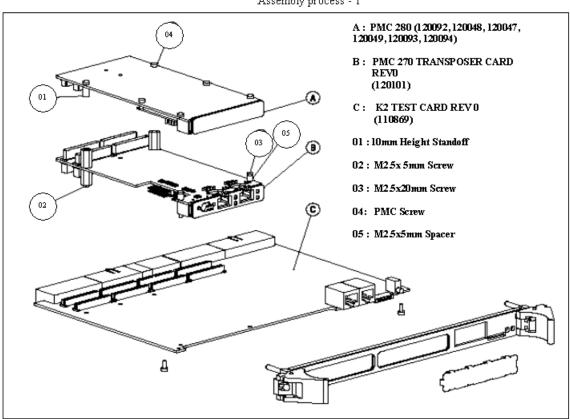

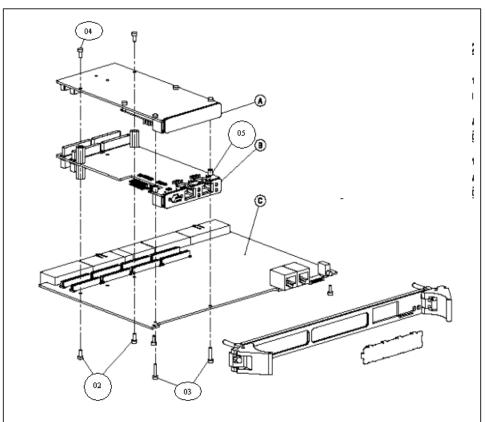

Note: The instructions detailed here do not describe how to install the carrier card and power up the board. Follow instructions detailed in the carrier card documentation (P/N K2TSTCARDIG) for installing the carrier card and powering up the board. In addition, refer "Assembly Instructions" page C-1 for information on assembling PMC-270 Transposer Card.

Always install PPMC-280 when power is turned off.

#### **Installing PPMC-280**

Follow these steps to install PPMC-280 on the carrier card:

- 1. Switch off power.

- 2. Remove the carrier card from the system according to the user's documentation.

- 3. Identify and locate the PMC slot on the carrier card into which you are installing PPMC-280.

- 4. Remove corresponding PMC slot filler from the front panel of the carrier card.

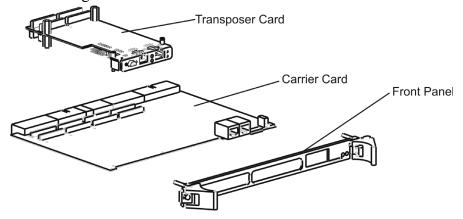

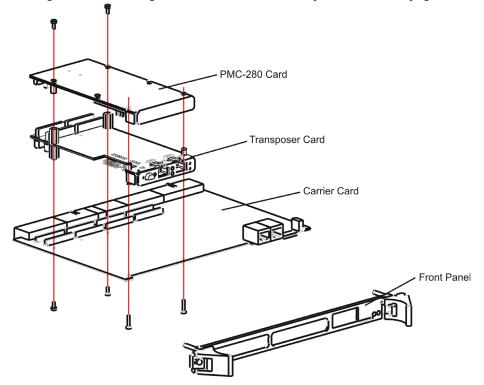

5. Mount the PPMC-270 Transposer card on the K2 carrier card as shown in the figure below.

Figure 14: Installing Transposer Card on Carrier Card

6. Engage the connectors. Make sure the connectors are seated completely.

7. Mount the PPMC-280 card on the PMC-270 Transposer card as shown in Figure 15 "Installing PPMC-280 Card on Transposer Card" on page 2-18.

Figure 15: Installing PPMC-280 Card on Transposer Card

8. Secure PPMC-280 using four screws provided. Ensure that you screw PPMC-280 from the rear side of the carrier card through clearance holes.

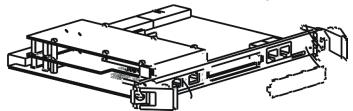

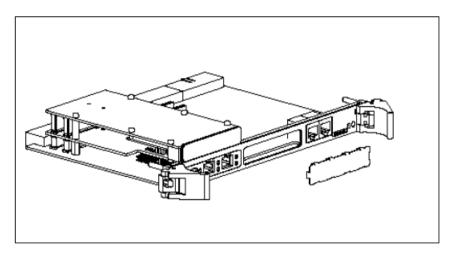

Installation of PPMC-280 along with the PMC-270 Transposer card on the carrier card is now complete. A view of the PMC along with a PMC-270 Transposer installed on a K2 carrier card is shown in Figure 16.

Figure 16: Installation of PPMC-280 with Transposer Card on Carrier Card

## **Removal Procedure**

To remove PPMC-280 from the carrier card, follow the steps listed below:

- 1. Turn off system power (Ensure that you follow the steps to turn off power for the carrier card as per carrier card documentation.)

- 2. If the carrier card is installed into a backplane, remove the carrier card according to the documented procedure for the carrier card.

- 3. Remove screws that secure PPMC-280 and PMC-270 Transposer card to the carrier card.

- 4. Carefully disengage PPMC-280 from the PMC-270 Transposer card. PPMC-280 is now removed from the carrier card.

## **Board Power Up and Initialization**

The steps listed below detail the board power up and initialization procedure:

- 1. Install PPMC-280 on the carrier card. (Refer to "PPMC-280 Installation on K2 Test Card" on page 2-16).

- 2. The MONARCH# signal of PPMC-280 has to be asserted by the carrier card when PPMC-280 is used as a Monarch. If PPMC-280 is to be used as a Non-Monarch, the carrier card must float the signal.

- 3. Connect the Serial Port 0 of PPMC-280 to the PC terminal using a cross wired cable. Ensure that the PC serial port is set for a baud rate of 115200.

- 4. Switch on system power. The power on LEDs (RefDes: CR8 for 3.3 V and CR9 for 5V) on PPMC-280 should glow to indicate that the board has powered up. If the Power Bad LED (Refdes CR18) is in the OFF state, it indicates that all voltage rails are within tolerance. (Refer to "LEDs" on page 4-3 for a detailed description of the LEDs on PPMC-280).

- 5. The Operating System/Boot Loader command prompt comes up on the terminal. The board is now fully configured and ready to accept valid commands given at the command prompt.

## 3

## **Devices and Other Functions**

### **On-Board Devices**

Note: This chapter describes features supported by the standard PPMC-280 variant, 120092. For features supported by other variants, please refer Table 1 "Variants of PPMC-280" page 1-4.

Details of the on-board devices are provided in this section. See Figure 2 and Figure 3 on Page 1-7 and Page 1-8 for the location of the on-board devices.

Table 8: List of Major Devices

| Description                                           |  |

|-------------------------------------------------------|--|

| Two PowerPC MPC7447 RISC Microprocessors<br>Motorola  |  |

| MV64360 System Controller<br>Marvell Technologies     |  |

| 4 x8Mx16 Intel <sup>®</sup> Strata Flash <sup>®</sup> |  |

| Two BCM5421 PHY                                       |  |

| Three Serial EEPROMs<br>AT24C64                       |  |

#### **Central Processing Unit**

There are two PowerPC<sup>™</sup> MPC7447 microprocessors from Motorola as the central processing unit. These operate with a core frequency of 1GHz. The combined heat sink for the CPUs is on the bottom side of PPMC-280.

The CPUs interface to each other and the System Controller through a 2.5V MPX bus (32-bit address, 64-bit data) that runs at 133 MHz.

Additional key features of the CPU are:

- On-die 512 K L2 cache

- Running at core frequency

- ECC logic

- Estimated typical power consumption of 8W

- At 1 GHz and 1.1V core voltage.

#### CPU 0 and CPU 1

As there are two CPUs, one of the CPUs is designated as CPU 0, and the other CPU is designated as CPU 1. CPU 0 acts as the boot master as it boots up first. CPU 1 is the boot slave. CPU 1 starts booting only after CPU 0 triggers the system controller's inbuilt bus arbiter to allow CPU 1 bus access. Each CPU can identify whether it is CPU0 or CPU1 by reading the Who Am I register in the System Controller.

Note: The terms CPU 0 and CPU 1 in this section refer to the boot master and slave respectively and not the physical CPU 0 and CPU 1 shown in Figure 3 "Bottom Layout of PPMC-280 Showing Major Components" page 1-8.

PPMC-280 is designed to swap the CPUs on-board which helps to assign CPU 1 as the boot master. This feature provides flexibility of where to locate CPU on a single-CPU variant of PPMC-280 depending on thermal factors. On variants 120047, 120049, and 120093, the (sole) CPU is located so as to have better airflow in a standard CompactPCI chassis; on variants 120094 and 120791, the (sole) CPU is located to take advantage of the direction of airflow in a custom chassis.

In the dual-CPU environment, CPU0 boots up first, initializes the system controller, memory, and serial port0, before triggering CPU1 to boot. Refer to the software installation guide for details.

#### **Boot Modes**

On variants 120092, 120047, 120049, 120791, 120673 and 120093, the boot flash+integrated SRAM combination is the default boot device. This boot mode is referred to as "boot-flash-boot" mode. However, variants 120048 and 120094 are configured to boot from PCI memory space. This boot mode is referred to as "PCI boot" mode. Auto-configuration of MV64360 from the I<sup>2</sup>C EEPROM is critical to both boot modes.

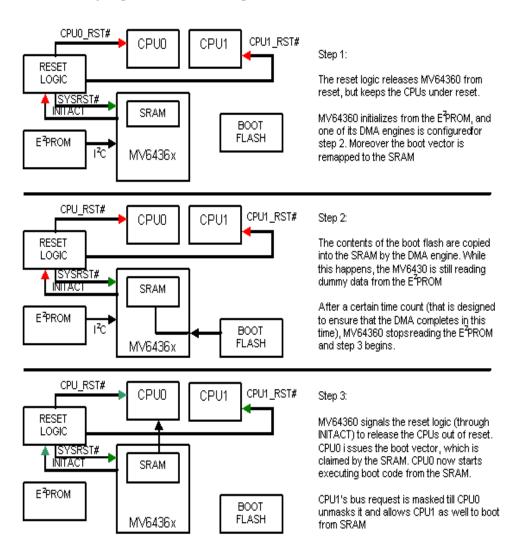

#### **BOOT-FLASH-BOOT MODE**

The boot flash is an 8-bit wide device that resides on the device bus of MV64360. Though the boot flash stores the boot image, the CPU does not fetch boot code directly from the boot flash. This is because the MPC7447 issues 32-byte burst reads right out of reset, and the MV64360's device controller does not support 32byte bursts to an 8-bit device. Hence, the MV64360's integrated SRAM (which is a 32-bit wide device) is used as the actual boot device. The MV64360 is configured (during auto-configuration from  $I^2C$ ) to remap the PowerPC boot vector to SRAM instead of boot flash.

The following steps describe the boot process in this mode:

#### PCI\_BOOT Mode

In this boot mode, the MV64360 is auto-configured through I<sup>2</sup>C such that the PowerPC boot vector is remapped to PCI space (instead of the default mapping to boot flash).

#### Note: Refer to "PCI Boot" page D-1 for additional information on PCI-Boot.

#### **System Controller**

PPMC-280 uses the Marvell Technologies MV64360 System Controller. The features utilized by PPMC-280 are detailed here.

#### **CPU Interface**

The following features are utilized:

- MPX bus at 133 MHz

- Internal bus arbiter

- Dual CPU support

#### DDR SDRAM Controller

The features utilized are:

- 64-bit DDR SDRAM interface

- 8-bit ECC

- Internally generated DDR differential clock output

#### PCI2.2 Interface

- 64-bit, 66 MHz, universal signaling (3.3V or 5V)

- Support for VPD as defined in PCI 2.2 specification

#### **Device Controller**

- 32-bit multiplexed device bus

- Support for Vital Product Data storage device on one chip select (DevCS3#)

#### Integrated 2Mb SRAM

#### Note: This feature is not supported by MV64362.

- 64-bit wide + 8-bit even parity

- Support for coherency with CPU caches (if required)

#### **Two Gigabit Ethernet MACs**

- IEEE802.3-compliant 10/100/1000Mbps Gigabit Media Independent Interfaces (GMII)

- port0 and port1 of MV64360 are used

- Dedicated Serial DMA (SDMA) to transfer data/descriptors to/from memory

#### Note: MV64362 supports only one Ethernet interface.

#### **Two Multi-Protocol Serial Port Controllers**

- Used as two independent UART ports

- A dedicated serial DMA (SDMA) to transfer data and descriptors to and from memory

| Interrupt Controlle | er |

|---------------------|----|

|---------------------|----|

Routes internally generated interrupts and external interrupts (on general-purpose pins) flexibly to two CPU interrupt outputs (separately for CPU0 and CPU1). Interrupts may also be routed to the PCI interrupt output in the Non-Monarch mode

#### **IDMA Controller**

Four channels for efficient data transfer between interfaces without significant CPU intervention

#### Watchdog Timer

- 32-bit down counter generating an NMI to the CPU periodically

- Expiry signal used to reset the system

#### I<sup>2</sup>C Timer

• Both master and slave capability.

- Support for multi-master environment

- Support for auto-configuration on power-on through I<sup>2</sup>C

#### Support for Dual Processing

- On power-on, MV64360 allows CPU0 to boot and keeps CPU1 bus request on hold. After CPU0 boots and initializes the system, it triggers the system controller's inbuilt bus arbiter to allow CPU 1 bus access and start booting.

- Separate interrupt outputs and interrupt mask registers for each CPU.

- Separate Doorbell interrupt register for each CPU, which can be used for CPUto-CPU interrupt generation, external PCI device-to-CPU interrupt generation, or for a CPU to interrupt itself.

- Who Am I register which each CPU can read to determine its identity (CPU0 or CPU1)

- Eight semaphore registers as a locking mechanism for shared resources

- Independent synchronization barrier mechanisms for each CPU to enable synchronization of data transfer between interfaces.

#### **General Purpose Ports**

There are 32 general-purpose ports which may also be configured as interrupts.

MV64360 operates on a 1.8V core voltage. The CPU interface operates on 2.5V, DDR interface at 2.5V, and other I/Os at 3.3V.

Note: Refer to the silicon ID of the system controller chip on the board to identify the chip version. The datasheet of the corresponding version is available from Marvell Technologies.

#### **On-board SDRAM**

PMC-280 supports on-board DDR266 (133MHz clock, 266MHz data rate) SDRAM with ECC. Memory size and organization are variant-dependent, as shown in Table 9 "Memory organization on PMC-280 variants" page 3-9.

| Variant                                 | Memory size | Logical organization                                           | Physical organization                                    |

|-----------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------|

| 120092,<br>120048,<br>120047,<br>120093 | 512MB       | Single-bank, mapped to<br>chip-select CS0# of<br>MV64360/62    | Nine 512Mb devices<br>(8 for data, 1 for ECC)            |

| 120049,<br>120673                       | 1GB         | Dual-bank, one bank<br>mapped to CS0# and the<br>other to CS1# | Nine dual-stacks (eighteen 512Mb devices, nine per bank) |

| 120094                                  | 128MB       | Single-bank, mapped to CS0#                                    | Nine 128Mb devices<br>(8 for data, 1 for ECC)            |

| 120791                                  | 256MB       | Single-bank, mapped to CS0#                                    | Nine 256Mb devices<br>(8 for data, 1 for ECC)            |

Table 9:

Memory organization on PMC-280 variants

Note: The usage of stacked memory devices results in a non-conformance from the CMC side-2 component height specification by 0.75mm on variants 120049 and 120673.

#### **Flash Memory**

PPMC-280 supports 64 MB (4 devices x 8M x 16) of NOR-based Intel<sup>®</sup> Strata Flash<sup>®</sup> on the MV64360's device bus (demultiplexed). This is organized as two banks (Bank0 and Bank1) of 32MB each. Features include:

- Flexible block locking

- Block erase/program lockout during power transitions

- Compliant to Intel's Common Flash Interface (CFI), Scalable CommandSet (SCS) and Command User Interface (CUI) implementations

PPMC-280 also supports 1 MB of Boot Flash (AM29LV008BBE). This is a non-volatile device that stores the boot image (PowerBoot). A portion of the Boot Flash is used as VPD storage device. This is done by redirecting the DevCS3# chip select of MV64360/62 to BootCS#. On variant 120094, Boot Flash is not used as the boot device, but as the VPD device.

Note: Boot Flash is not used as the boot device on variants 120048 and 120094. These variants boot from PCI memory space. Refer to "Boot Modes" on page 3-4 for additional information.

#### **PCI Interface**

PCI interface between PPMC-280 and the carrier card is made through PMC connectors P1, P2 and P3. It is a 3.3V/5V, 64-bit (64-bit addressing also supported), 66 MHz PCI2.2 compliant interface implemented in MV64360. The connectors P1 and P2 carry the 32-bit PCI signals, whereas the P3 connector carries the 64-bit extension signals. Refer to Chapter 4 for Connector pin assignments.

#### **PCI Signaling Voltage**

PCI signaling voltage to be used can be 3.3V or 5V as decided by the carrier card. The PMC connectors P1 and P3 have V(I/O) pins which are in turn connected to the VREF (PCI reference voltage) pin of the MV64360. The carrier card should supply the V(I/O) pins with 3.3V or 5V to decide the PCI signaling voltage.

#### **PCI Clock**

The PCI clock is supplied by the carrier card. The clock frequency can be any value up to 66 MHz.

Note: PCI clock is independent of and asynchronous with respect to the processor bus and SDRAM frequencies.

#### **PCI Vital Product Data**

MV64360 provides support for Vital Product Data access through PCI as defined by the PCI2.2 specification. The VPD data structure is stored in the boot flash. Refer to the VxWorks/Tornado BSP Rel. 2.0 for PPMC-280 Programmers Guide (Order Number 221088 410 000) for more information.

#### **Special Function Processor PMC Signals**

PPMC-280 implements the Processor PMC signals/pins as defined in the VITA 32-199x standard.

| Signal Name | Function                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRESENT#    | Is grounded on PPMC-280 to indicate to the carrier card that the Processor PMC is installed                                                                                                                                                                                                                                                                     |

| MONARCH#    | Enables Monarch-mode operation of PPMC-280. Is pulled up on PPMC-280. LED CR6 indicates the status of this signal.                                                                                                                                                                                                                                              |

| EREADY      | Open-drain output signal in Non-Monarch mode, and input signal<br>in Monarch mode. Weak pull up (10k) on the Processor PMC.<br>Used to inform the Monarch that all PPMCs are ready for PCI con-<br>figuration. LED CR7 indicates the status of this signal.                                                                                                     |

| RESETOUT#   | Open-drain output under software control. May be used as an input<br>to the carrier card reset logic. Time duration of RESETOUT#<br>assertion is controlled by the software. If RESETOUT# assertion<br>finally results in resetting PPMC-280 itself, the RESETOUT# out-<br>put of PPMC-280 is tristated as soon as PCI_RST# is asserted by<br>the carrier card. |

**Table 10:** Special Function Processor PMC Signals Implemented

#### Monarch and Non Monarch Operation

PCI enumeration in a system consisting of (one or more) Processor PMCs is performed by Monarch (The Processor PMC operating in Monarch mode). When the carrier card grounds the MONARCH# pin on the PMC connector, the software configures PPMC-280 as a Monarch and proceeds to perform PCI bus enumeration (Provided the EREADY signal is asserted). It acts as the PCI interrupt handler and enables PCI interrupt inputs. The PCI interrupt output of the MV64360 is disabled in the Monarch mode.

When the carrier card floats the MONARCH# pin, PPMC-280 operates as a Non-Monarch. In this mode, it deasserts EREADY till it has completed the on-board configuration, and then asserts it to indicate to the Monarch that it is ready for PCI enumeration.

Conventionally, PPMC-280 in the Non-Monarch mode does not handle PCI interrupts, and masks the PCI interrupt inputs from being routed through the interrupt controller, and the PCI interrupt output of the MV64360 is enabled.

#### Note:

- CPU0 is responsible for Monarch and Non-Monarch status detection and related action.

- PPMC-280 can work on a carrier card that does not support the EREADY signal. In this case, PCI enumeration is begun as soon as Monarch status is detected.

- When the carrier card does not support the MONARCH# signal PPMC-280 will enter the Non-Monarch mode by default.

## PCI Interrupts When PPMC-280 operates in the Monarch mode, it acts as a PCI interrupt handler by default. The PCI interrupts INTA#, INTB#, INTC#, and INTD# are routed from the PMC connector to the internal interrupt controller of the MV64360 through the general-purpose ports (GPPs) of the MV64360 configured as interrupt inputs. The interrupt output of MV64360 is disabled in this mode.

When in the Non-Monarch mode, PPMC-280 has one interrupt output that is wired to the PCI interrupt INTA#. In this mode, PPMC-280 does not handle the PCI interrupts by default. This is however possible through a BSP option.