# Nuclear Physics Division Data Acquisition Group

# **Description and Technical Information for the VME Trigger Interface (TI) Module**

J. William Gu (jgu@jlab.org)

Updated on: Dec. 3<sup>rd</sup>, 2013

# **Table of Contents**

| <u>Section</u> | Title                            | Page |

|----------------|----------------------------------|------|

| 1              | Introduction                     | 3    |

| 2              | Purpose of TI Module             | 4    |

| 3              | Function Description             | 7    |

| 4              | Specifications                   | 16   |

| 5              | TI operation                     | 18   |

| 6              | Programming Requirements         | 20   |

| 7              | VXS P0 and VME P2 Row-C Pin outs | 29   |

| 8              | Examples of individual test      | 30   |

| 9              | Software setup for TI            | 31   |

| 10             | Citation                         | 32   |

| Appendix A     | Schematics                       | 33   |

| Appendix B     | Fabrication Drawing              | 51   |

| Appendix C     | Bill of Materials                | 54   |

| Appendix D     | Glossary                         | 60   |

| Appendix E     | TI data format                   | 61   |

| Appendix F     | Revision history                 | 62   |

# 1 Introduction

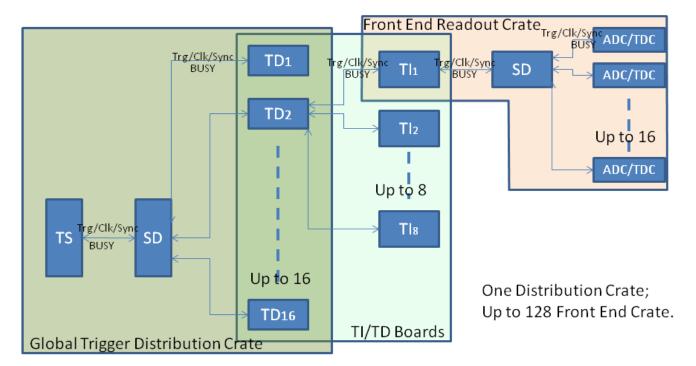

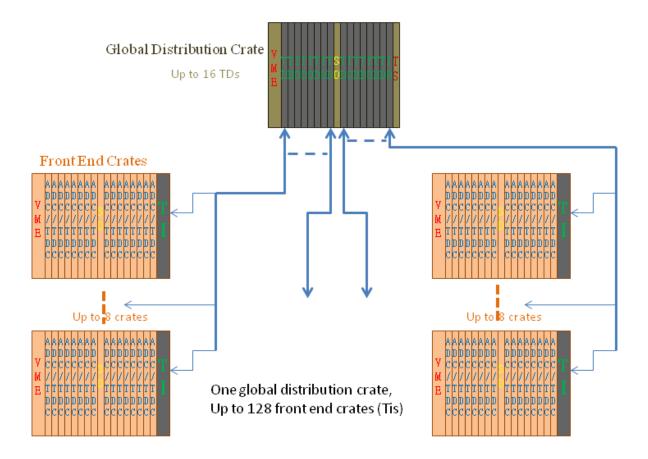

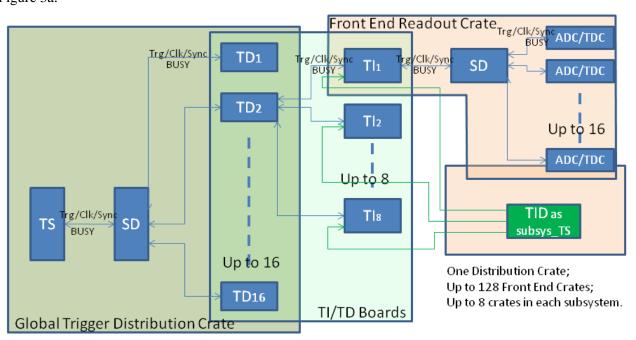

The Trigger Interface (TI) module is being designed for the Jefferson Lab 12GeV upgrade, mainly for HallD [ (Collaboration G. , 2009)] and Hall-B [ (Collaboration C. , 2009)], with other experimental Halls [ (experiments, 1990)] compatibility. The TI boards are located in data acquisition frontend crates, and are responsible for providing a low-jitter system clock, sync signals and fixed latency trigger signals for the Front-end readout boards in the crates. The modules also merge the front-end crate status and generate a BUSY signal to request the Trigger Supervisor (TS) to pause the trigger. For the detailed description, refer to the Trigger Distribution system design document [Trigger Distribution]. Figure 1a shows the placement of the TI modules in the global trigger distribution scheme in experiment setup. Figure 1b shows the crate level diagram

Figure 1a:

Figure 1b:

The TI shares the same PCB design as the Trigger Distribution (TD) board. The TI board has simple Trigger Supervisor (TS) functions built in. The TI can act as a subsystem trigger supervisor when used independently. The TI board can have optionally eight optic fibers populated, and distribute Trigger/Clock/Sync to another 8 (eight) TI boards. A subsystem with up to nine crates can be setup without a real TS module. The TI also has the flexibility to select the trigger and clock inputs from central trigger system or local (sub-system) trigger system.

# 2 Purpose of the module

TI board is positioned in the last slot of the front-end data acquisition crate, and connects to a TD module in the global trigger distribution crate. This is done using a four channels full-duplex fiber link, which provides a gigabit trigger link, global 250MHz clock and synchronization link to phase lock the trigger and initialize the system. The trigger link uses a reference clock derived from the 250MHz global pipeline clock allowing a trigger word to be distributed every 4 global pipeline clock cycles. Depending on the trigger word type the TI can issue a crate level trigger condition through the VXS switch port B. The trigger bits are sent to a Signal Distribution (SD) module that distributes these signals to all front-end modules in the crate. The TI also accepts status signals from the SD module, which is the logical OR of the status signals from all the other front-end modules. These status signals can be transmitted back to the TS through the fiber link to slow down or inhibit further distribution of triggers until the status has been resolved. For now, the status includes a BUSY only. When the BUSY is set, the front end boards are requesting for trigger inhibit. The assertion of a status signal will create a dead-time in the data acquisition system which should be a rare occurrence since the data acquisition is being designed to handle the full trigger rate that can occur from the physics events. The dead time will be monitored and recorded by the Trigger Supervisor board.

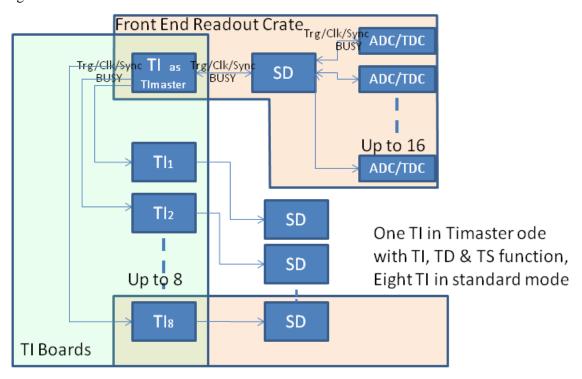

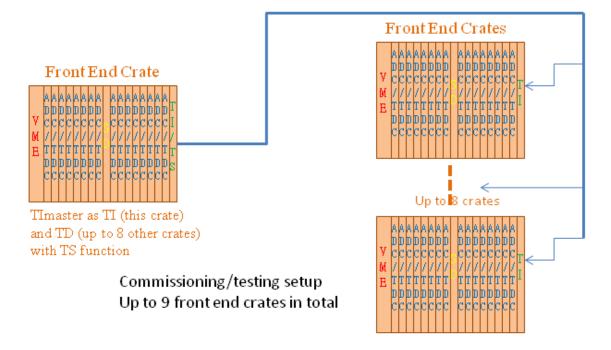

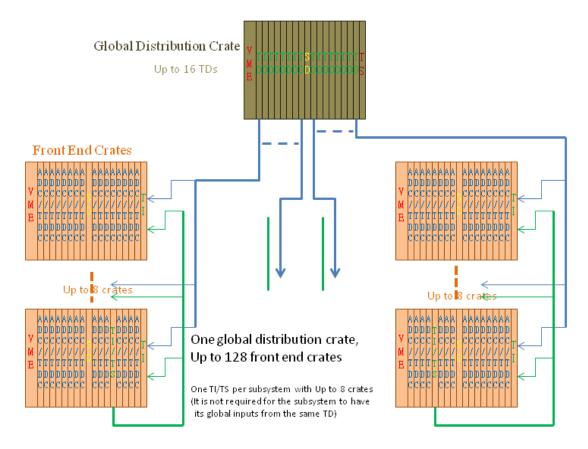

The TI can also perform simple Trigger Supervisor functions. In test setup or commissioning setup, the TI can perform as a TI Master (TM). In this case, it can take inputs from its front panel and generate trigger/clock like a TS, it can sends the trigger, clock, and SYNC to the backplane (P0 and P2) like a TI, and it can send the trigger, clock and SYNC to the front panel fibers like a TD. With the TM, a test setup can include up to nine (9) crates. Figure 2a shows the setup. Figure 2b shows the crate level diagram.

Figure 2a

Figure 2b

The TI FPGA firmware is compatible with the TImaster mode and the standard TI mode. The firmware senses the TI clock setting. If the TI clock source is set to onboard oscillator or front panel ECL input, the TI is in TM mode, or else, the TI is in standard mode. For the TM mode, the TRG/SYNC used in the TM is similar to the TRG/SYNC sent in the optical transceiver. The TRG/SYN is looped back within the FPGA and decoded the same way as a standard TI board. Some registers are valid on the TM only, as these registers are specific to the TS function. The TM can be used by itself in the setup. It can also drive another up to eight TIs if the setup needs be expanded.

When the TI is in standard TI mode, it can have two HFBR-7924 modules stuffed. In this case, one can receive trigger from system TS, while the other can receive trigger from a sub-system TS. One TID can be located in any payload slots in a front-end crate, and configured as a subsystem TS. This configuration requires an extra optical transceiver on the TI module, and an extra TID board be configured as a subsystem TS with fiber outputs. Each optical transceiver module costs about \$400. For a subsystem with eight crates, the extra cost is about \$10K (extra optic fiber included). The benefit is that the subsystem can have independent control without affecting the other subsystem. That is a lot of flexibility: independent subsystem control, independent subsystem calibration etc. This is called a luxury option. Refer to figure 3a for the setup. Figure 3b shows the crate level diagram

Figure 3a:

Figure 3b:

There is another direct connection between the TI and switch slot A board (CTP or GTP) and switch slot B board (SD). This link can be used to transfer data between the TI board and the switch slot boards. It is natural to implement the link at 250 Mbps using the system clock, or 500 Mbps with DDR technique. If the Data acquisition function is built in the SD, the SD can collect and assemble events at the trigger by trigger basis, which provides a redundant data readout path. The SD/CTP can send their data to the TI, and the TI combines the data with its own data event by event. The data can be readout through VME (there is no direct VME access to the switch slot A and switch slot B)

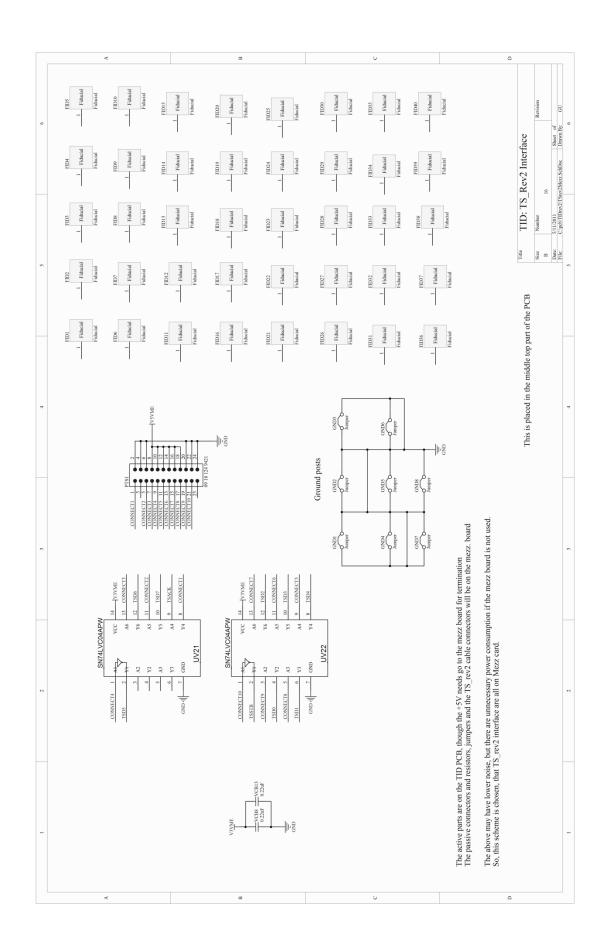

With a mezzanine board, the TI is backward compatible with Trigger Supervisor Rev2 module. The TI with the mezzanine card will behave the same way as TI\_Rev2 (produced in the year of 2001) board with added functionality.

For non-VXS crate (or non-VXS data acquisition modules), the TI will send trigger/clock/Sync to Row-C on VME P2 connector. With a fan out board, the trigger/clock/SYNC are distributed to the frontend data acquisition modules (CAEN VX1290 TDC for example), and the BUSY from these modules are summed in the fan out module, and sent back to the TI.

# **3 Functional Descriptions**

# 3.1 General description

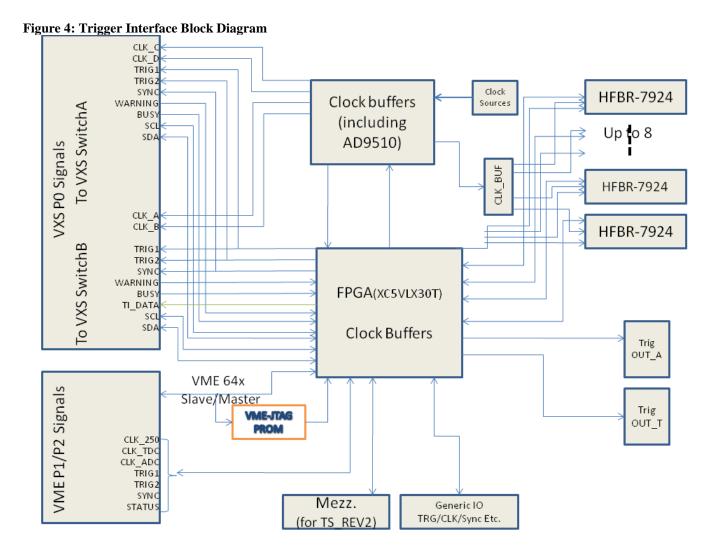

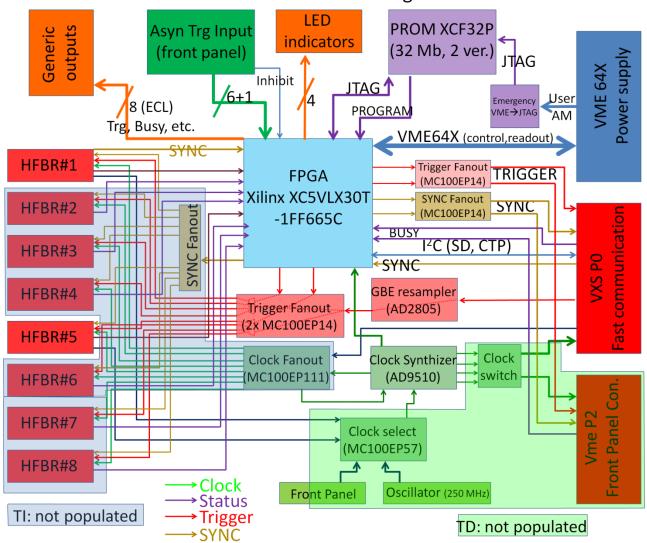

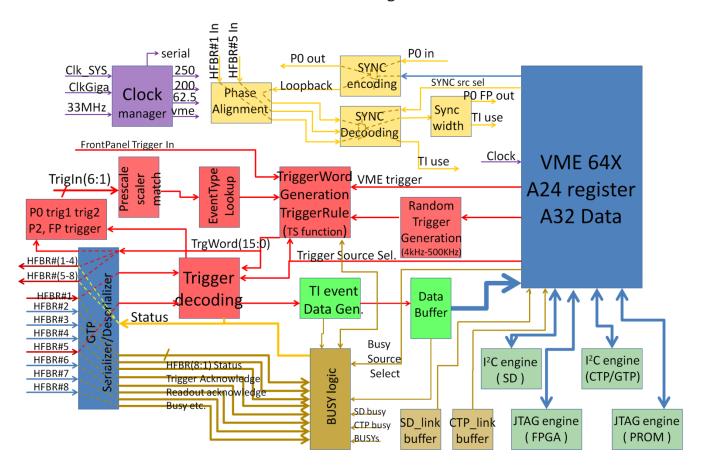

Figure 4 shows the block diagram of the TI module, indicating the major components used in the design. The HFBR-7924 is the multi-channel (4 Rx, 4 Tx) fiber link that the TI fans out/receives a low-jitter (<3ps RMS) 250MHz global pipeline clock, serialized 16bit trigger words, and a sync signal used in producing a synchronized trigger. The AD9510 is the main clock driver and gets synchronized lower frequency clocks. The Xilinx

XC5VLX30T is used to encode/decode the trigger words at 16ns, to interface with the VME, to control the working mode etc. The P0 is compatible with the VXS payload slots, which matches with GTP, CTP, SD positioned in switch slots.

# TI board block diagram

## TI FPGA block diagram

#### 3.2 Fiber links

The HFBR-7924 is the multi-channel (4 Rx, 4 Tx) fiber optic link for the TI. For some TImaster boards, all the eight HFBR-7924 transceivers will be installed, so each can support another eight front end data acquisition crates. For the standard TI in the front end crates and global trigger crate, One (maybe two) HFBR-7924 transceiver will be installed, to receive the trigger/clock/sync from central trigger (and subsystem trigger).

The HFBR\_7924 is chosen over the HFBR-7934, because the HFBR-7924 is about \$100 cheaper per piece, and there is no visible performance degradation comparing with HFBR-7934. [GU, 2010]

The first pair (Tx/Rx) is used to transfer trigger words from TD to TI, and status from TI to TD. The second pair is used to transmit the 250MHz clock from TD to TI. The third pair is used to transmit the SYNC from TD to TI. The TI to TD links on second pair and third pair are not used.

The fourth pair (Tx/Rx) is looped back on the TD for fiber length (latency) measurement. The fiber numbers #2, #3, #4, #6, #7 and #8 on TImaster are looped back by a short trace on the PCB between the HFBR Tx and Rx pads. The fiber#1 and #5 are controlled by the FPGA. For TImaster, the FPGA loops back the signals; for standard TI, the FPGA generates a pulse and receives the loopback pulse. By measuring the delay, the fiber delay is measured.

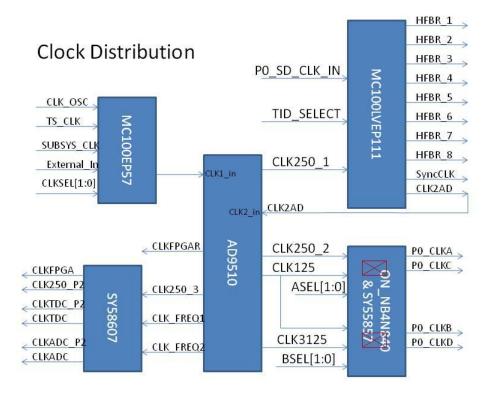

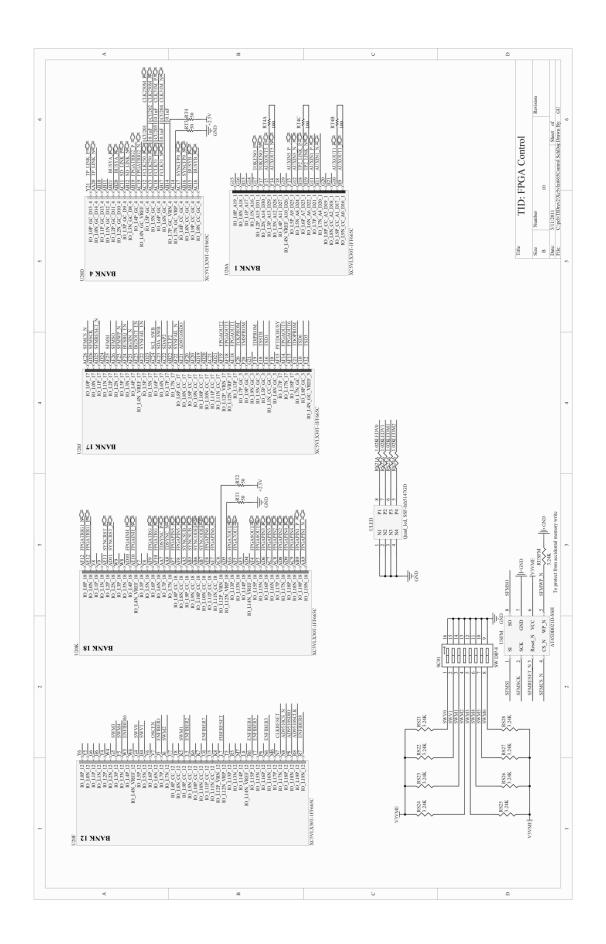

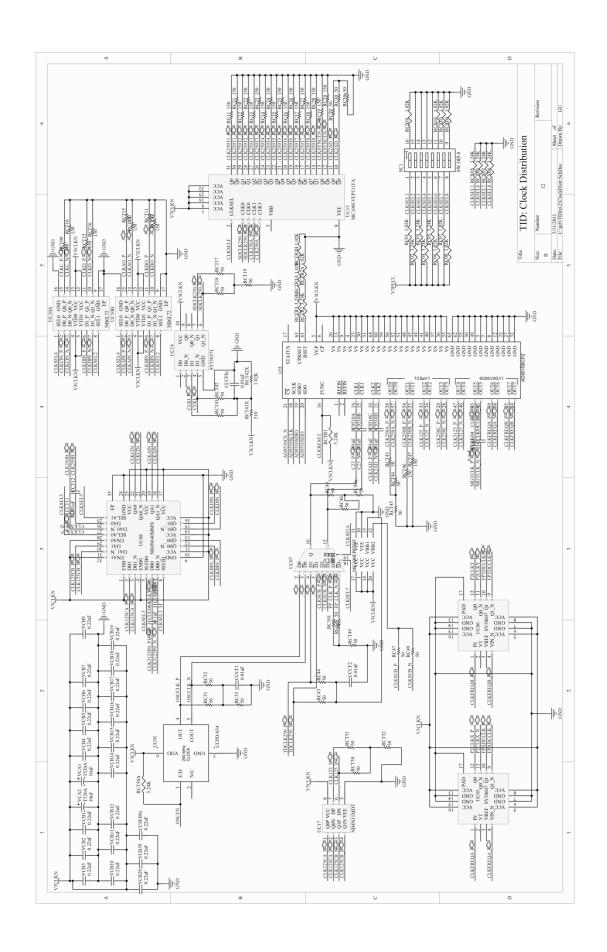

#### 3.3: Clock Distribution

One of the TI's major functions is the pipeline clock distribution. There are four possible sources for the 250MHz clock: 'onboard oscillator', 'external clock input from twisted pair cable', 'optical fiber input from central trigger HFBR#1' and 'optical fiber input from subsystem trigger HFBR#2'. The five clock sources will be multiplexed. There will be only one 250MHz clock running on the TI. The clock is multiplexed by a MC100EP57 chip and go to the AD9510 CLK1 input, and the output of the AD9510 drives all the outputs. In TImaster mode, The clock is fanned out by the MC100LVEP111 2:1:10 clock driver to the optic transceivers.

Three clocks (with frequencies of 250 MHz, 125 MHz, and 31.25 MHz) are distributed to the P0 backplane. One On-Semiconductors' NB4N840M and two NB6L72 are used to switch the clocks, so that, the switch slot #A and switch slot #B can get two clocks. Each clock could be any of the three frequencies. The NB6L72 is also used as a level shifter from CML to LVPECL.

The clock is also distributed to the front panel connectors via ECL on twisted pair cables and VME P2 backplane user defined pins for VME ADC or TDC modules, which are NOT VXS compatible.

The CAEN V1290 TDC will get a synchronized 41.67MHz clock through TID P2 connector via a fan out board in the crate, instead of the nominal 40MHz onboard oscillator frequency, because there will be too much effort involved to generate a system wide synchronized 40MHz clock, and the V1290 can be calibrated to accept the 41.67 MHz clock.

An eight-bit on board switch will be used to select the clock sources except for the AD9510, which will be set by the switch, but the setting can be over written by the FPGA firmware (and software).

Figure 5 shows the TID clock distribution diagram:

The clock is distributed in (LVP)ECL levels to keep the low jitter and low skew (faster propagation). The LVDS clock is used to drive the FPGA for easy termination.

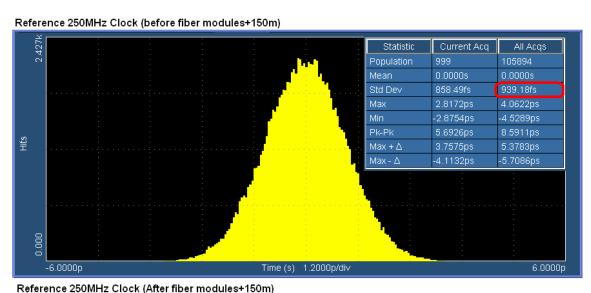

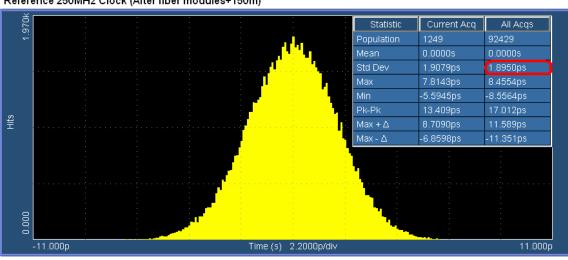

The global 250MHz clock signal received over the fiber runs the L1 trigger pipeline electronics and nearly all of the front-end modules. Several front-end modules require this clock to have low-jitter and so the clock signal is buffered with components that contribute low-jitter, including the fiber driver and receiver. Figure 3c shows a measurement of the jitter contribution from the fiber driver/receiver pair, including a small increase in clock jitter (roughly 1.6ps additive jitter from the fiber driver/receiver with 150m of fiber between them) by GU et al. [ (GU, 2010)]. Careful component selection, signaling, and layout techniques are employed to minimize overall clock jitter. The SD board can further clean up the jitter by its PLL chips.

Figure 6: Global Clock (250 MHz) Jitter

# 3.4 Trigger distribution:

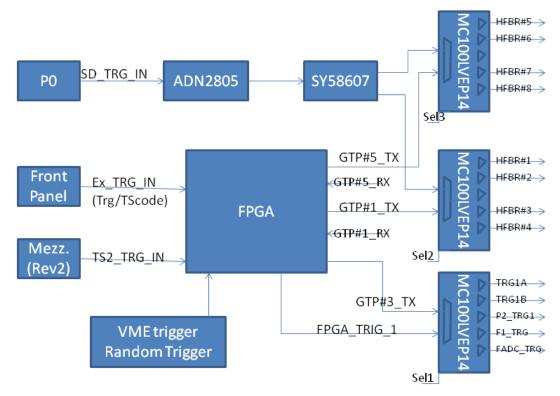

Figure 7 shows the trigger distribution on TI. The TI receives the trigger signal by the optical fiber and decoded by the FPGA. The trigger is sent to the fan out buffer then to the P0 backplane and other connectors. When the TI is in TImaster mode, the TM takes the trigger from the front panel input and send to the SD in gigabit serial mode (encoded) or pulse mode, and it also sent to the fiber in encoded format, though the HFBR#1, #2, #3 and #4 are identical, and HFBR#5, #6, #7 and #8 are identical. (Surely, these two groups can be the same too). The independent choices of the trigger enable the versatile functions of the TI.

Figure 7, Trigger distribution

## 3.5: Encoded Trigger Word

A 1.25Gbps serial link operating over the fiber is used for distributing a 16bit trigger word every 16ns. There is also a link going in the opposite direction, allowing status words to be sent back to the trigger distribution crate. The 16bit trigger words are decoded as follows (TS->TD->TI flow):

Trigger strobe word – generated by the TS in response to the acceptance of a level 1 trigger. Upon receipt, the TI drives prompt trigger signals to the front-end modules. The TS transmits these with fixed latency relative to the accepted trigger. This word is distributed every 16ns, so the trigger is distributed every 16ns. The timing information is added in the trigger word to distinguish which quadrant of the 16 ns period the trigger is generated to be fully compatible with the 4ns pipeline design architecture. The TI can distribute trigger signal in 4ns precision. This could potentially reduce the FADC readout window width, and reduce the event size.

Trigger content word – additional information about the trigger for use by the ROCs. It is queued in a FIFO and sent in any frame not used by a trigger strobe word. The TI matches the trigger strobe and trigger content words by the order of their reception.

Control Word – request status, or other command (VME trigger for example). They can be queued in a FIFO and sent in any frame not used by a trigger strobe word or trigger content word.

Master Time Word – to fully use the trigger link, bits [13:2] of the TS time is transmitted whenever no other word types are available. By continuously receiving bits [13:2] of the TS time, each TID can promptly detect if its frontend crate has lost global synchronization (i.e. compare the global time with its own time). Otherwise, the loss of synchronization could only be detected at the event building stage. The continuous transmission of 'known' (i.e. predictable) data also allows one to monitor the integrity of the link.

| This table    | shows    | the | format   | of t  | the | trigger | word  |

|---------------|----------|-----|----------|-------|-----|---------|-------|

| I III G table | DIIO W D | uic | 101111ut | $o_1$ | u   | uissui  | word. |

|       |       |           | 66                   |

|-------|-------|-----------|----------------------|

| Bit13 | Bit12 | Word Type | Meaning of Bit[11:0] |

| 0 | 0 | Time            | Lower 12 bits of TS time      |

|---|---|-----------------|-------------------------------|

| 0 | 1 | Control         | Control or Command            |

| 1 | 0 | Trigger Strobe  | Trigger type/Trigger quadrant |

| 1 | 1 | Trigger Content | Additional Trigger data       |

Bits [15,14] are used on TS to further distinguish the trigger types and TS partitioning.

The following defines the data format for the opposite direction of the link (TI->TD->TS flow):

Bit [15] parity bit;

Bit [14:12] 000 right now;

Bit [11] TI (including the front end crate) BUSY: '1' = busy, '0' = not busy;

Bit [10] Trigger\_1 acknowledge;

Bit [9] Trigger\_2 acknowledge;

Bit [8] one block of triggers received;

Bit [7] ROC readout acknowledge (one block of trigger is readout and acknowledge by ROC);

Bit [6:0] status.

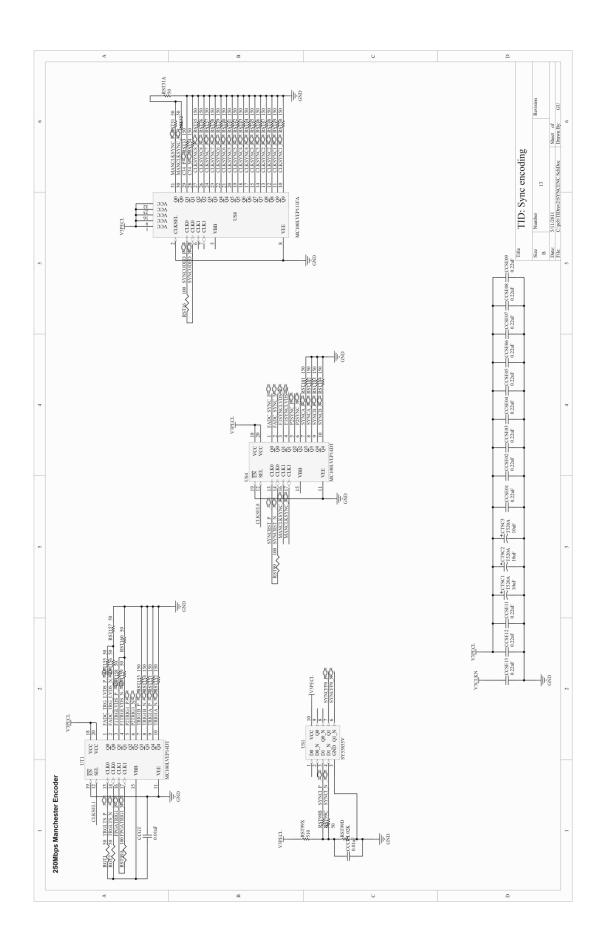

## 3.6: Fixed Latency SYNC

The SYNC signal is a 250Mbps serial line operating in synchronous mode. This serial link allows a 4bit command to be sent at chosen 4ns points in time. SYNC is synchronized to a slower clock (62.5 MHz) derived from the 250 MHz master clock and is sampled every 4 ns. The line is considered to be idle when more than 4 samples in a row are read '1'. A command is sent between idle times by sending first a '0' followed by the 4bits that comprise the command, LSB first. After the command has been sent, a final '1' is sent so that the line will return to the IDLE state. The encoding portion of this serial protocol is performed on the TS (or the TS function of the TImaster). Since the TD distributes this serial line over the fiber module, additional encoding (Manchester) is performed to balance the 1's and 0's of the line and to keep the maximum run length of the signal below the requirements of the fiber module. The TID decodes the SYNC signal (Manchester and command). Careful design in minimizing SYNC to the distributed master CLK250 skew guarantees a fixed latency link.

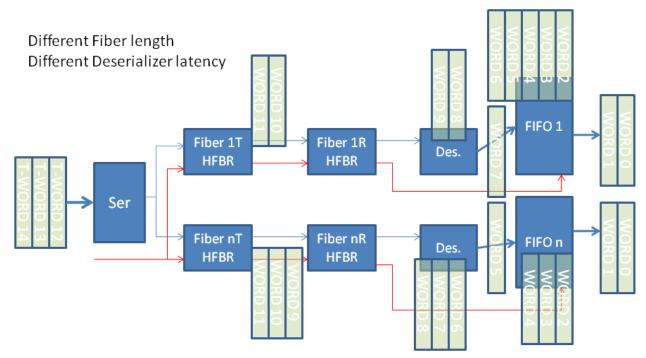

The SYNC is fiber delay adjusted on each TI. The fiber latency is measured using the fourth pair of the fiber. The SYNC is delayed so that all the TI modules will execute the SYNC command at exactly the same time (within the skew of the global 250MHz clock distribution).

The SYNC link is used in conjunction with a synchronous FIFO to enforce a fixed latency on the serial trigger link. The TD uses LVPECL buffers to fan out the trigger signal and the Sync signal, which is encoded (Manchester encoding) in the FPGA, to the HFBR\_7924 transceivers. In the TI, the trigger word is clocked into a FIFO using the FPGA built in MGT transceivers and clocked out of the FIFO using a 62.5MHz clock derived from (and in phase with) the 250 MHz system clock. At startup, the FIFO is reset (0 words) and reading the FIFO is disabled. No words are written into the FIFO since the TS is not yet transmitting data words on the trigger link (i.e. received data valid signal is not asserted). Acceptance of triggers by the TS is also disabled. The TS starts transmission (time words) on the trigger link, and after a fixed number of 62.5MHz clock cycles issues a trigger start command on the SYNC line. In response to the trigger start command, the TI enables continuous readout of the FIFO. There must always be a non-zero number of words in the FIFO to maintain a fixed latency link. This will be true if the number of words pre-filled into the FIFO x 16 ns is greater than the latency uncertainty of the link. In the case of the MGT, several words (e.g. 3 or 4) are enough when the latency is set to minimum, as the elastic buffer is not necessary as all the clocks are the same or derived from the same 250MHz clock (no clock frequency difference). The TS must always be transmitting valid data to maintain the fixed latency of the link. This is illustrated in figure 8:

Figure 8: Illustration of the Trigger synchronization process

The SYNC link is also useful in ensuring that the lower frequency clocks derived in the TI from the distributed system clock (CLK250) have the same phase across all TI modules in the front-end data acquisition system. At startup, the TS issues a SYNC command CLKRESET. This resets the clock distribution chip (AD9510) in each TI on the same CLK250 edge, assuring that the lower frequency clocks (125MHz, 62.5MHz, 41.67MHz and 31.25MHz) are in phase across the entire system. This command is sent before the TI sync command. The delay between them is determined by the maximum MGT reset recovery time, as the MGT clock is changed (AD9510 clock reset) during clock reset. The time is several milliseconds.

Figure 9 shows the block diagram of the SYNC distribution on the TI board:

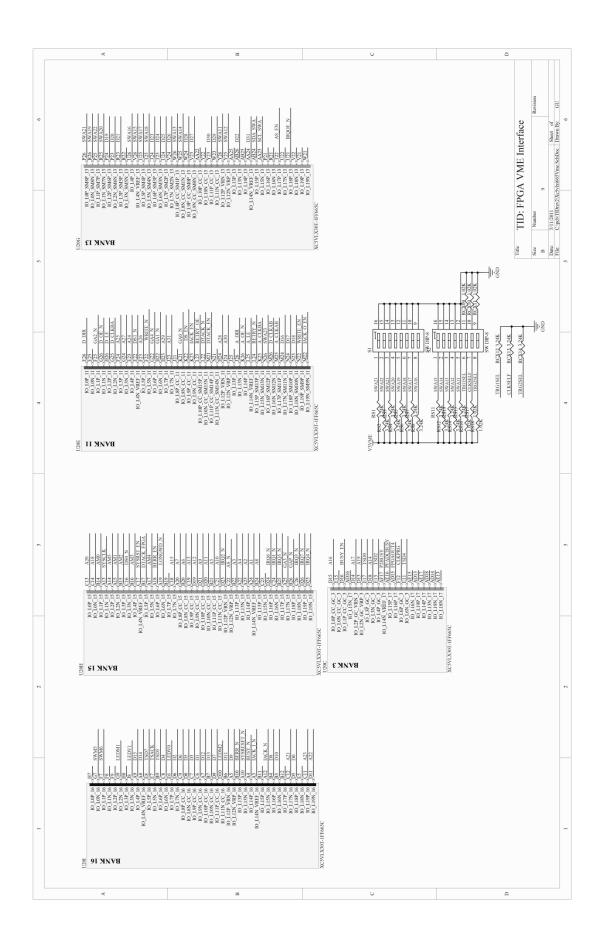

## 3.7 VME interface

The TI board is a VXS payload slot board. It is compatible with VME64x backplane. Normally, it is a VME slave board, with interrupt capability.

The TI can also be a master VME board. It supports single level bus request (BR3, level 3) only, as we do not expect many boards to be a VME master in the crate.

For simplicity, three kinds of VME address modifier codes are implemented. (1), User defined address modifier. (0x19,0x1A, 0x1C and 0x1D) This is similar to the A24 address modifier. It is used to load the PROM by the emergency logic. (2), Standard A24 address modifier. This is used to readout the registers on the FPGA, slow controls of the TI peripherals, and to request data from other boards in the crate when in master mode. (3), A32 BLT data transfer. This is used to transfer data to the ROC (Read Out Controller). This is implemented the same way as other ADC/TDC board, so the ROC needs only one read to get all the front end boards' data out for higher efficiency.

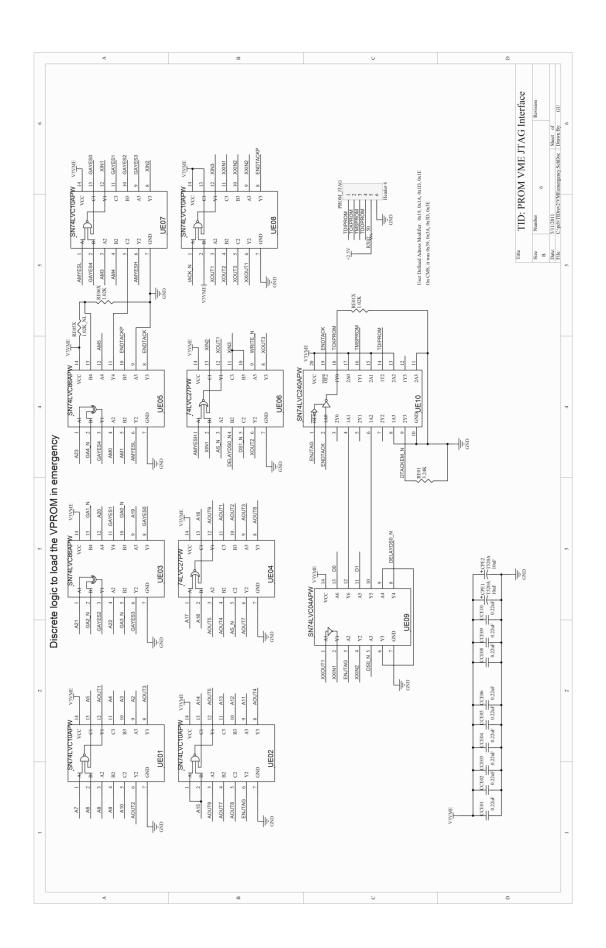

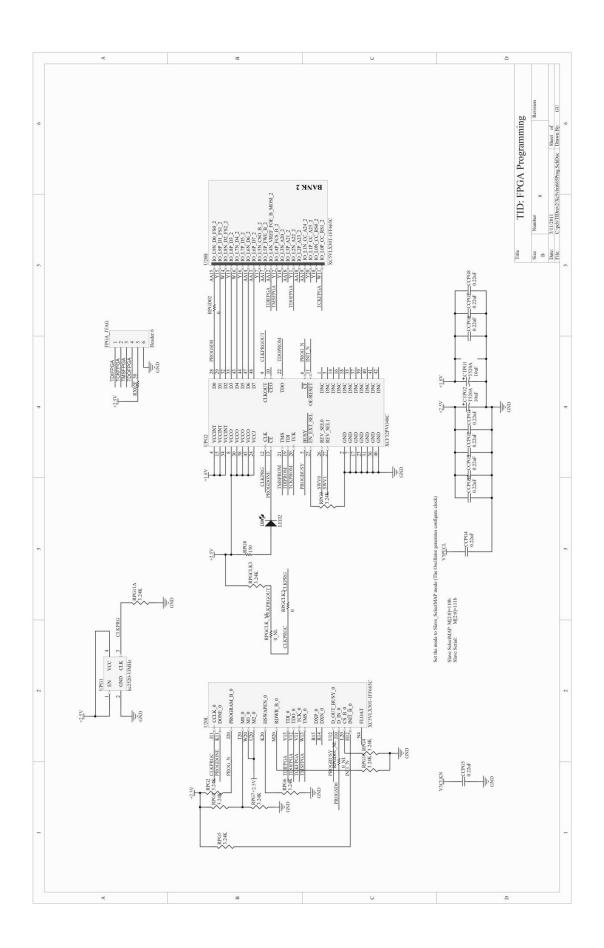

## 3.8: The Xilinx PROM programming.

The Xilinx XCF32P PROM is used to program the FPGA. It can save two different versions of the FPGA (XC5VLX30T) firmware when used in non-compression mode. It can save four different versions of the firmware when bit stream compression is used, in which case, only the slave serial and slave SelectMAP modes are supported. The PROM is programmed using VME with emergency logic decoding. It can be addressed in the VME64x crates by its geographical address. If it is in the crate without geographical address, only one TI in the crate should be addressed as geographical slot#0. To avoid conflict with other VME addressing, the user-defined address modifiers are used for the PROM loading. The emergency logic supports A24 user defined address modifier codes: 0x19, 0x1A, 0x1D and 0x1E (Similar to 0x39, 0x3A, 0x3D and 0x3E). Out of the data, bit[1] is used for TDI, bit[0] is used for TMS, and all the other bits are unused. The emergency loading is tested. With M6100 controller, the 32 Mbit PROM (XCF32P) can be loaded in less than five minutes. The emergency loading provides VME remote firmware re-loading and broadcast firmware loading even if the FPGA is not working. One 33 MHz on-board oscillator is used to program the FPGA in slave mode, and used by the FPGA for slow control, for example, the VME to AD9510 serial control engine. The PROM is in master mode with external clock. This is set when producing the SVF download file.

The PROM can also be programmed by the on-board JTAG connector and VME-JTAG engine (after the FPGA is programmed and working) in the FPGA. The JTAG engine in the FPGA provides VME remote firmware loading when the FPGA is working with more efficient VME data transfer (32 bits versus 1 bit).

# 3.9: Status passing

The TI can merge the status together and pass on to upper level. Specifically, the TI can merge the status from the CTP and SD via P0 backplane and pass on to TD in the global trigger/clock distribution crate via optical links. Right now, only the BUSY is defined as status. We have the capability to add a less severe state, WARNING, to the status.

The TI in the front end crate can send its timing information back to the TD in the trigger distribution crate. This information can be used to check the system synchronization status. Here is how this will work.

On the start of the run, a global sync command will reset all the counters synchronously. Each TI will have its own clock counter, that count how many clock cycles since the sync reset. As the trigger is synchronized on all the TIs, all the TI should receive the same trigger at the same clock cycle. The TI in the front end crate will send the clock counter, recorded when it receives the trigger, to the TD in the distribution crate along with the trigger acknowledge. This signal may be received asynchronously as a status word (ref to section 3.5), but all the eight words should match on the TD. The TD check the difference between the trigger sent and the trigger acknowledge received. The TD also checks the trigger acknowledge timing. If the TD received un-matching numbers from front-crate, it is most likely a trigger loss if the timing difference is large; it is most likely a clock loss if the difference is small. In this way, the trigger synchronization can be checked at the hardware level.

#### 3.10: Serial data communication with SD

The TI can send data to the SD via a 250Mbps link, (it is possible to increase it to 500 Mbps using DDR techniques). This can be implemented using the Xilinx SelectIO standard differential IO pin pair. In this case, the SD can be implemented as a data concentrator card to collect data from the VXS crate (the payload modules include FADC, FTDC, TI, etc.). The TI will send data to SD on every trigger (event). This is another data readout path in addition to the standard VME readout. The maximum data rate is 50 MB/sec per slot. The full crate can reach up to 900 MB/sec assuming all 18 payload slots are used. The data from SD is event based, and there is no need to re-format the data as needed by the VME readout (block readout is used for high efficient usage of the VME bus data transfer).

The SD can also send data to TI using this link, though there are not much useful per event data from SD anyway. The direction of the data link depends on the firmware (TI and SD) implementation.

## 3.11: legacy compatibility

A mezzanine board is used to interface with the TS\_rev2 module directly for backward compatibility, which may still be used in the experiment halls. The Mezzanine board has the same connector as the TI\_rev2 board (matching with Trigger Supervisor rev2). With the mezzanine board plugged in, the TI will behave like a TI\_rev2 board (produced in 2001) to interface with TS\_rev2 board.

#### 3.12 Other functions

The TI has a generic IO 34 pins connector, which can accept one external trigger input, and six trigger input codes. It can also accept external clocks and trigger inhibit. Using these, some of the Trigger Supervisor functions can be implemented in the TI. The TI can serve as a subsystem trigger supervisor board. A nine crates setup can be implemented by TIs for (sub)system commissioning and subsystem test setups.

## 3.13: Readout Synchronization

In addition to the event number and trigger time stamp, the readout can be forced to get synchronized by synchronization events (SyncEvent). There are two ways to generate the SyncEvent.

First, the SyncEvent can be generated periodically by TS (or TImaster). The last event of the every N blocks is generated as the SyncEvent. (for now, the block level, or number of event per block, is up to 255) The N is any value between 1 and 65535, which is set and enabled by A24 register offset 0xD4. When the periodic SyncEvent is marked, the original event type is kept.

Second, the SyncEvent can be forced by VME command to the TS (or TImaster). This event may be any event in the trigger block. It is an added event with event type "00000000". The forced SyncEvent can be generated by VME A24 register offset 0x100, bit#20. It is also possible that the SyncEvent is generated by a front panel signal input.

The TS (or TImaster) will assert a short BUSY (3us) after generating the SyncEvent, and stop further triggers. After receiving the SyncEvent, the TI will generate BUSY, and set the SyncEvent marker in the ROC polling register A24 offset 0x34. The BUSY of TI will propagate back to the TS through fibers and P0 backplane. The latency of this should be less than 3us, so that it will overlap with the short BUSY on TS. After the front end data is cleared, and the Readout acknowledge will clear the BUSY on the TI. In pipeline readout mode, If there are more than one trigger blocks to be read out, the very last acknowledgement clears the SyncEvent BUSY on the TI. After all the TI boards clear their BUSY, the TS will distribute trigger again. Depending on the data acquisition mode and the amount of data backed up on the frontend, this process may take tens of microseconds to many milliseconds.

Upon SyncEvent, the trigger distribution will be paused. Users can change the DAQ settings during this time. If no reset in this time period, the event number and trigger time be continued.

# 4. Specification Sheet

## 4.1 Mechanical

• Single width VITA 41 Payload Module. It will be positioned in PP18 in front-end data acquisition crate and global trigger crate; it can also be plugged into any slots in standard VME crates without VXS. In system commissioning, it can be in PP18 and support up to 9 crates with some TS functions. In luxury setup (optional), it can be in any payload slots (except PP18) of the subsystem crates, and serve as a subsystem Trigger Supervisor, which can group up to 8 crates together as a subsystem.

## 4.2 High speed serial P0 and P2 inputs:

- BUSY LVDS signals on P0;

- BUSY ECL signals on P2;

- I<sup>2</sup>C to VXS Switch A & B;

# 4.3 High speed serial P0 and P2 outputs:

- Any two of these clocks (250MHz, 125MHz, and 31.25MHz) to Switch slot #A and Switch slot #B.

- Trig 1 LVPECL Trigger Signal

- Trig 2 LVPECL Trigger Signal

- Sync LVPECL Trigger Signal

- 250/500 Mbps data (LVDS) to/from SD at per event basis

## 4.4 Front panel inputs and outputs:

- 250MHz ECL Clock Input & Output

- Trig 1 ECL Trigger Input & Output

- Trig 2 ECL Trigger Input & Output

- Sync ECL Trigger Input & Output

- Busy ECL Input & Output

- Up to eight HFBR-7924 transceivers for TImaster; up to two HFBR-7924 transceivers for standard TI in front-end data acquisition crate.

# 4.5 Fiber channel signals:

- SYNC Fixed Latency Link

- o 250Mbps Serial Communication

- Manchester Encoded

- o SYNC to CLK skew variation adjusted at FPGA receiver.

- TRIGLINKTX/TRIGLINKRX

- o 1.25Gbps Trigger Word Line

- o Provides 16bit parallel data every 16ns

- o A BUSY status word in the opposite direction.

- CLK

- o 250MHz Clock <3ps RMS Jitter

#### **4.6 LED Indicators: Front Panel:**

- Bit 1 (close to the PCB): FPGA programmed and the clock (DCM locked) is ready;

- Bit 2: VME DTACK, VME activity;

- Bit 3: Trigger 1 is sent out;

- Bit 4: HFBR MGT Rx error;

#### On board:

- Power OK near each regulator or DC-DC converter (LED is OFF when the power is OK);

- FPGA program DONE (LED is OFF when programmed);

- Fiber optical transmitter FAULT and receiver SIGNAL\_DETECTED near each HFBR-7924 module.

# 4.7 Programming:

- VME to JTAG A24D32 with user defined AM (Address Modifier) for remote loading with redundant On board JTAG connector;

- Custom VME to JTAG engine implemented in the FPGA using A24D32 for firmware loading;

- Up to four revisions of the firmware can be stored in the PROM simultaneously.

## **4.8 Power requirements:**

- +5v @ 4 Amps; -12V @ 0.25 Amp; +12V @0.25 Amp (From Backplane)

- Optional DC-DC converters for +3.3V, and Local regulators for other required voltages: +1.0V, +1.2V, +1.8V, +2.5V, +3.3V, and -5V.

## 4.9 Environment:

- Forced air cooling: Weiner standard VME64x/VXS

- Commercial grade components (0-75 Celsius)

Figure 10 shows a typical TI board:

# **5 TI operation procedures:**

The TI needs be properly set, and plugged into the proper crate and slot. Damage may happen to the TI, the crate, or other PCBs in the crate if the right procedure is not followed.

# **5.1 TI Power supply:**

The TI can use +3.3V directly from VME64x crate. It can also generate its own +3.3V supply by a DC-DC converter. Another dedicated +3.3V DC-DC converter can be used to power the optical transceivers (HFBR-7924). The HFBR\_7924 can also be powered by the main +3.3V supply for the board. Proper settings are needed to avoid damage to the board or backplane.

If the dedicated +3.3V DC-DC converter is used to power the HFBR-7924:

- (1). Make sure that the DC-DC converter LTM4604, UP01, is stuffed.

- (2). Inductor, LP3 is removed.

If the TI main +3.3V power is used to power the HFBR-7924:

- (1). Make sure that UP1 NL is NOT stuffed,

- (2). Inductor LP3 is stuffed.

If the VME64x crate +3.3V power is used for the TI:

- (1). The fuse, FP1 is stuffed;

- (2). The DC-DC converter UP1 is removed.

If the VME64x crate +3.3V power is not used for the TI:

(1). The fuse, FP1 is removed;

# **5.2 Hardware setting (Switch etc.):**

The TI drives signals to the P0 connector. This is set by three pairs of resistors or capacitors. If the 0 Ohm resistors are used, the signals are DC coupled, if 0.047uF capacitors are used, the signals are AC coupled. When in Subsystem TS mode, stuff C0001/C0002, C0003/C0004, and C0007/C0008; when in TI mode (including TImaster), stuff C0011/C0012, C0013/C0014, and C0017/C0018. This will avoid driving conflict with SD.

There are four 8-bit switches on the TI, and marked as: S1, S2 (VME address space setting switches), SC01 (TI mode setting) and SC1 (TI clock setting). Some switches are LVTTL, some are LVPECL. When the switch is ON, the switch is LOW, (0V for LVTTL, and 1.4V for LVPECL); when the switch is OFF, the switch is HIGH, (3.3V for LVTTL, and 2.5V for LVPECL). Here are the details of the switch setting:

#### **5.2.1. SC1 setting:**

Bit1: LVPECL, open=high, trigger\_1 source selection. When low, the trigger\_1 source is FPGA MGT\_112 output (serialized trigger data); when high, the trigger\_1 source is standard FPGA differential output (pulse);

Bit2-5: LVTTL, open=high, P0 CLK\_A, CLK\_B, CLK\_C, CLK\_D selection. Clk\_A is the same as CLK\_C and CLK\_B is the same as CLK\_D. The clocks are selected in two stages:

| Switch \ clock out | Clock_X | Clock_Y |

|--------------------|---------|---------|

| Bit3=0; bit5=0     | 250     | 31.25   |

| Bit3=1; bit5=0     | 250     | 125     |

| Bit3=0; bit5=1     | 125     | 31.25   |

| Bit3=1; bit5=1     | 125     | 125     |

| Switch \ clock out | Clock_A, Clock_C | Clock_B, Clock_D |

|--------------------|------------------|------------------|

| Bit2=0; bit4=0     | Clock_X          | Clock_X          |

| Bit2=1; bit4=0     | Clock_X          | Clock_Y          |

| Bit2=0; bit4=1     | Clock_Y          | Clock_X          |

| Bit2=1; bit4=1     | Clock_Y          | Clock_Y          |

Bit[7:6]: LVPECL, open=HIGH, closed = LOW: TID 250MHz clock source selection. When bit7=0&bit6=0, on-board oscillator is selected; when bit7=1&bit6=0, TD input from optical transceiver #1 is selected; when bit7=0&bit6=1: subsystem clock input from optical transceiver#5 is selected; when bit7=1&bit6=1: front panel generic connector inputs is selected; For FPGA control, refer to A24 register offset 0x2C bit(1:0).

Bit8: LVPECL, open=high, TI connectors' sync signal source selection. When low, Sync\_reset is selected; when high, Manchester encoded SYNC signal is selected.

#### **5.2.2 SC01 setting:**

Bit[2:1]: LVTTL, open=high. Firmware revision selection. When Bit2=0&Bit1=0, select firmware Rev0; when Bit2=0&Bit1=1, select firmware Rev1; when Bit2=1&bit1=0, select firmware Rev2; when Bit2=1&Bit1=1, select firmware Rev3. If the program bits are not compressed, the PROM XCF32P can only fit two revisions of the firmware.

For TImaster5 firmware (not the latest TIFPGA firmware), the Bit(4:3) are decoupled from Bit(2:1). The Bit(2:1) controls the firmware revision, while the Bit(4:3) is a firmware variable. If Bit(4) = 1, the CLK1 input of AD9510 is selected, which is the mux of four independent 250MHz clocks. If Bit(4)=0, the CLK2 input of AD9510 is selected, which is the clock from P0 backplane. If Bit(4)=1

and Bit(3)=0, the FiberMode=1, which will power down the HFBR#2, #3, #4, #6, #7 and #8. When the FiberMode=1, the TID is in pure TI mode.

Bit[6]: LVTTL, open = high. Connector output clock frequency selection. When high, the clocks are 41.667 MHz, used for CAEN TDC; when low, the clocks are 250 MHz, used for FADC250 fan-out

Bit[7,8]: LVTTL, open = high. This is to control the SD\_link and CTP\_link loopback test. When high, the driver is disabled, and the TI is the receiver for SD\_link and CTP\_link. When low, the driver is enabled, and the TI is the receiver and the driver. (loopback if no SD/CTP in the crate).

#### **5.2.3 S1 setting:**

Bit[1:3]: These three bits are used to control the OUTPUT(5:2) of the front panel 34-pin connector. The switches are used to multiplex the eight FPGA internal monitoring sources (32 signals) on the four output pins.

Bit[4]: Add an extra word if the total number of words in a block is odd. '1' to enable, '0' to disable;

Bit[8]: keep high, for TID rev1, this pin is used as IACK input to the FPGA;

Bit[8:7]: keep high, for TID rev2, these two pins are used as clock source selection output from the FPGA;

Bit[5:6]: not used.

#### **5.2.4 S2 setting:**

Bit[1:5]=A[23:19], VME address space in A32 or A24 mode. Be careful about the bit order. When in VME64x crate, these addresses should be set the same as its geographical address.

Bit6: LVPECL, open=high. The HFBR#1, #2, #3 and #4 trigger source selection. When low, the source is P0 (from SD), when high, the source is FPGA GTP 116.

Bit7: LVPECL, open=high. The HFBR#1\_8 fan out clock source selection. When low, the fan out source is P0 (from SD), when high, the source is on-board clock manager AD9510. This should be consistent with the bit(4:3) of SC01 switch setting.

Bit8: LVPECL, open=high. The HFBR#5, #6, #7 and #8 trigger source selection. When low, the source is P0 (from SD), when high, the source is FPGA GTP 114.

#### **5.3 Software setting:**

After the board is properly set, and plugged in the right slot, some software setting needs be applied for the board to work. Some parts of the board needs be powered down to reduce the power consumption. The FPGA GTP transceivers will be automatically powered depending on the mode setting (TI or TImaster).

The delay settings will be automatically loaded by fiber measurement. This information could be saved in the Serial Flash Memory (SFM). The parameters (delay etc.) can be set by the VME, and stored in the SFM. We expect the parameter to be stable, but adjustment may be necessary when moving the board (different fiber connection etc.)

In the test setup and commissioning test, some delay parameters (especially the TImaster) needs be manually set.

# **6.** VME Programming Requirements (This part will be updated as the firmware develops)

There are three categories of Address Modifier codes are supported on the TI: the user-defined codes (A24) for emergency firmware loading; Standard A24 for FPGA register read/write and slow control; A32 block transfer for VME data readout.

# **6.1 VME to JTAG emergency loading:**

The AM[5:0] user defined codes are used for this logic. This works even before the FPGA is programmed and working. It is almost the same as A24D32 mode. The valid AM codes are: 0x19, 0x1A, 0x1D and 0x1E. These AM codes are user defined, and similar to the AM codes 0x39, 0x3A, 0x3D and 0x3E.

The valid address bits are A[31:24] do not care; A[23:19]=GA[4:0] for VME64x crates, or A[23:19]=0 for non-VME64x crates; A[18:2]=b'000111111111111111.

Data bit[1] is TDI; data bit[0] is TMS.

For example, if the board is in slot#5 (that is  $\sim$ GA(4:0)= 11010), you need write to A(23:0)=0x28fffc. If data(1:0)=00, both TMS and TDI will be low; if data(1:0)=01, TMS is high, TDI is low; if data(1:0)=10, TMS is low, TDI is high; if data(1:0)=11, both TDI and TMS are high. The normal A24 address should try to avoid this address (0x0fffc).

A more advanced example: Instruction register shift (8-bit, shift in 0x5a) starting from/end up at the 'reset idle' mode: 14 consecutive writes to the address 0x28fffc with AM=0x19, 1a, 1d or 1e, the data are 1, 1, 0, 0, 0, 2, 0, 2, 2, 0, 2, 1, 1, 0 respectively.

| Data | 1  | 1  | 0  | 0  | 0 | 2 | 0 | 2 | 2 | 0 | 2 | 1 | 1  | 0  |

|------|----|----|----|----|---|---|---|---|---|---|---|---|----|----|

| TMS  | Н  | Н  | L  | L  | L | L | L | L | L | L | L | Н | Н  | L  |

| TDI  | 0x | 0x | 0x | 0x | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0x | 0x |

• "TMS H" means logic High, "TMS L" means logic Low, "TDI 0" means 0 or Low, "TDI 1" means 1 or High, and "TDI 0x" means DO NOT CARE by the JTAG, but the set value is 0.

## **6.2 Configuration Registers:**

A24D32 are used for register read/write. Similar to the emergency loading logic, the base address is determined by the Geographic Address in VME64x crate, and external switch for non-VME64x crate. That is, A[23:19]=GA[4:0], or SW[5:1].

#### Address offset: 0x00000: Board ID:

Bit 7-0 (R/W): Crate ID; Reset default 0x00; [0x00, BIT(7:0)]

Bit 12-8 (R): A24 address, higher 5 bits; Reset default 000 [0x54, BIT(4:0)]

Bit 13 (R): '1': TS is in running mode, it is GA parity bit for TI;

Bit 15-14 (R): '10': TS is in running mode (no more register changes), others: TS not in running mode;

Bit 23-16 (R): PCB related setting, 0x01: production board, 0x00; prototype board;

Bit 31-24 (R): Board type: 0x71: TI, 0x75: TS, 0x7D: TD. [0x54, BIT(31:16)]

#### Address offset: 0x00004: Optic transceiver enable:

Bit 7-0 (R/W): on TI: HFBR#8, #7, ... #1 Enable, Reset default 0xFF all enabled. [0x04, BIT(7:0)]

Bit 0: '1' enable HFBR#1, '0' disable HFBR#1; ('disable' means 'power down')

Bit 1: '1' enable HFBR#2, '0' disable HFBR#2;

Bit 2: '1' enable HFBR#3, '0' disable HFBR#3;

Bit 3: '1' enable HFBR#4, '0' disable HFBR#4;

Bit 4: '1' enable HFBR#5, '0' disable HFBR#5;

Bit 5: '1' enable HFBR#6, '0' disable HFBR#6;

Bit 6: '1' enable HFBR#7, '0' disable HFBR#7;

Bit 7: '1' enable HFBR#8, '0' disable HFBR#8;

Bit8: Enable the P0 (SW#A, SW#B), Front panel connectors, and VmeP2 trigger and SyncReset signals, default is 1 to enable; When disabled, the trigger/SyncReset stay LOW.

Bit 23-16 (R): if '1', the HFBR#8, #7, ... #1 is connected to a TI (serial Link synchronized);

Bit 31-24 (R): if '1', the HFBR#8, #7,...#1 connected TI has its trigger source enabled.

Address offset: 0x00008: Interrupt setting:

```

Bit 7-0 (R/W): Interrupt ID; Reset default 0xC8 [0x08, BIT(7:0)]

Bit 10-8 (R/W): Interrupt level; Reset default 5; [0x08, BIT(10:8)]

Bit 16 (R/W): IRQ enable. Reset default: 0; [0x04, BIT(13)]

```

Address offset: 0x0000C: Trigger delay and Pulse width:

```

Bit 7-0 (R/W): Trigger_1 delay, (n+1)*4 ns; Reset default 0x07; [0x0C, BIT(7:0)]

Bit 15-8 (R/W): Trigger_1 Pulse width (n+1)*4 ns; Reset default 0x07; [0x0C, BIT(15:8)]

Bit 23-16 (R/W): Trigger_2 delay, (n+1)*4 ns; Reset default 0x07; [0x0C, BIT(23:16)]

Bit 31-24 (R/W): Trigger_2 Pulse width (n+1)*4 ns. Reset default 0x07; [0x0C, BIT(27:24)]

```

Address offset: 0x00010: A32 address space:

```

Bit 13-5 (R/W): Address Max; Reset default 0x1FF; [0x10, BIT(13:5)] Bit 22:14 (R/W): Address Min; Reset default 0x000; [0x10, BIT(22:14)] Bit 31-23 (R/W): Base Address. Reset default 0x100; [0x10, BIT(31:23)]

```

Address offset: 0x00014: Block size:

Bit 7-0 (R/W): Block size. Reset default 0x01; This is used on TD only. It's read/write register but does not affect anything in the FPGA.

Bit 23-16 (R): Block size (block level). This is the block level used on the FPGA.

Bit 31-24 (R): Block size set by TS (or TImaster). This is an intermediate value. The ROC should readout these eight bits, and set them to the FADC250, FADC125, etc.

Address offset: 0x00018: TI data format control: Reset default 011; [0x00, BIT(31:29)]

Bit 0: if '1', two block placeholder words are enabled; '0' disabled.

Bit 2-1: Event format control:

bit 1: '1' to enable the lower 32-bit trigger timing word;

bit 2: '1' to enable the higher 16-bit of event number and higher 16-bit of trigger timing;

Address offset: 0x0001C: VME setting; Reset default 0x011:

Bit 0 (R/W): '1' enable Bus\_Error\_En, so the block read can be terminated by event block trailer; [0x10, BIT(0)]

```

Bit 1 (R/W): '1' en token in is true, '0' en token in is false; [0x10, BIT(1)]

```

Bit 2 (R/W): '1' enable 'Multi-board' readout, '0' disable 'Multi-board'; [0x10, BIT(2)]; asset to enable multi-board token passing protocol;

Bit 3 (R/W): '1' enable en\_A32m, '0' disable en\_A32m; [0x10, BIT(3)]; assert to enable common A32 multi-board addressing of module;

Bit 4 (R/W): '1' enable en A32, '0' disable en A32; [0x10, BIT(4)]

Bit 7 (R/W): '1' enable VME bus interrupt for module error?

```

Bit 8 (R/W): '1' I2C device address 0x1101xxx, '0' I2C device address 0x0000xxx; [0x04, BIT8]

Bit 9 (R/W): '1' token in high, '0' token in low; [0x04, BIT(9)]. If both bit 9 and bit 1 are set high, the

Token_Out will be high (this is for SD test).

Bit 10 (R/W): '1' first board true, '0' first board false; [0x04, BIT(10)]

Bit 11 (R/W): '1' last board true, '0' last board false; [0x04, BIT(11)]

Bit 15 (R/W): '1' disable data readout buffer full [0x04, BIT(15)]

Address offset: 0x00020: Trigger source register:

Bit 15-0 (R/W): Trigger source enables: Reset default 0x0000; [0x00, BIT(23:16)]

Bit 0: P0 trigger input;

Bit 1: HFBR#1 trigger input;

Bit 2: TImaster loopback trigger input;

Bit 3: Front Panel trigger input;

Bit 4: VME trigger;

Bit 5: Front Panel Trigger Codes (as Supervisor) inputs;

Bit 6: TS_rev2 trigger input;

Bit 7: Random Trigger.

Bit 10: HFBR#5 trigger input

Bit 12: SubTS#1 trigger enable, this is valid on HFBR#1 input only;

Bit 13: SubTS#2 trigger enable, this is valid on HFBR#1 input only;

Bit 14: SubTS#3 trigger enable, this is valid on HFBR#1 input only;

Bit 15: SubTS#4 trigger enable, this is valid on HFBR#1 input only;

Bit 31-16 (R): Trigger source monitor. [0x00, BIT(31:24)]

Address offset: 0x00024: Sync Source register:

Bit 15-0 (R/W): Sync Source enables: Reset default 0x02; [0x00, BIT(28:24)]

Bit 0: P0 sync input (in Subsystem TS mode);

Bit 1: HFBR#1 sync input;

Bit 2: HFBR#5 sync input;

Bit 3: Front panel trigger inhibit enable;

Bit 4: TImaster loopback SYNC enable

Bit 6: automatic SyncReset enable

Bit 7: Enable the option for RESET to be set high (sync code 0x99), and low (sync code 0xcc).

Bit(11-8) (R): last SYNC code from HFBR#1;

Bit(15-12) (R): last SYNC code from HFBR#5;

Bit(19:16) (R): last SYNC code from loopback;

Bit(20) (R): SYNC history fifo empty;

Bit(21) (R): SYNC history fifo has more than 512 entries;

Bit(22) (R): SYNC history fifo full (reached 1024 entries);

Bit 31-24 (R): Sync source monitoring. [0x28, BIT(23:16)]

Address offset: 0x00028: Busy source registers:

```

Bit 15-0 (R/W): Busy source enables: [0x04, BIT(31:16)]

```

Bit 1: '1' enable the Switch Slot #B BUSY input, '0' disable;

Bit 2: '1' enable the VME P2 BUSY input, '0' disable;

Bit 3: '1' enable the FTDC front panel BUSY input, '0' disable;

Bit 4: '1' enable the FADC front panel BUSY input, '0' disable;

Bit 5: '1' enable the Front Panel BUSY, which is the same as TsRev2 busy;

Bit 7: '1' enable TS feed back BUSY, '0' disable the busy. (useful in TM mode)

Bit 15-8: HFBR #8-#1 BUSY enables: '1' enable the HFBR BUSY input, '0' disable;

Bit 31-16 (R): BUSY source monitoring. [0x28, BIT(15:0)]

Address offset: 0x0002C: Clock source selection:

Bit 1-0 (R/W): software bit switch to control the clock source. Reset default 00; [0x08, BIT(13:12)]

Bit[1:0] = 00: oscillator clock;

Bit[1:0] = 01: HFBR#5 clock input;

Bit[1:0] = 10: HFBR#1 clock input;

Bit[1:0] = 11: Front panel 34-pin connector clock input.

Address offset: 0x00030: Trigger_1 pre-scale:

Bit 15-0 (R/W): pre-scale factor: Rate = Rate_0 / (Bit(15:0)+1). [0x0C, BIT(31:28)]

Address offset: 0x00034: Trigger block inhibit:

Bit 7-0 (R/W): TS trigger inhibit threshold (in the unit of event blocks); Reset default 0x01; [0x08,

BIT(31:24)]

Bit 23-8 (R): Number of blocks in the DAQ ready to be readout. [0x14, BIT(31:24)]

(on TI, Bit 23-16 (R): Number of events before the a block is formed. [0x14, BIT(23:16)])

Bit 27-24 (R): Number of missing block acknowledge;

Bit 28 (R): if '1', the RUN is stopped because the block number (readout) has reached. (set by 0xFC)

Bit 29 (R): if '1', the event block is being filled by FillTrg;

Bit 30 (R): SyncReset Request set. If '1', SyncReset is required. To be issued by TImaster/TS.

Bit 31 (R): SyncEvent received, and the system is BUSY. Waiting for ROC to clear the frontend data.

Address offset: 0x00038: Trigger rules:

Bit 7-0 (R/W): No more than 1 Trigger in (Bit(6:0)*(16/500 ns)); Bit7 determines 16ns or 500ns step.

Reset default 0x03; [R:0x58, BIT(23:16)] [W:0x810, BIT(7:0)]

Bit 15-8 (R/W): no more than 2 trigger in (Bit(14:8)*(16/500ns)); Bit15 determines 16ns or 500ns step.

Reset default 0x03; [W:0x810, BIT(15:8)]

Bit 23-16 (R/W): no more than 3 triggers in (Bit(22:16)*(16/500 ns)); Bit23 determines 16ns or 500ns step.

Reset default 0x03; [R:0x58, BIT(31:24)] [W:0x810, BIT(23:16)]

Bit 31-24 (R/W): no more than 4 triggers in (Bit(30:24)*(16/500 ns)). Bit31 determines 16ns or 500ns step.

Reset default 0x03; [W:0x810, BIT(31:24)]

Address offset: 0x0003C: Trigger coincidence window:

Bit 7-0 (R/W): Trigger input coincidence window; Reset default 0x01;

Bit15-8 (R/W): Trigger inhibit window (extra to bit(7:0)). Reset default 0x00;

```

Bit 0: '1' enable the Switch Slot #A BUSY input, '0' disable;

These two parameters are used to determine the event resolution

Address offset: 0x00048: Front panel generic trigger input enable:

Bit 15-0 (R/W): Front panel generic trigger input enable (34-pin TI). Reset default 0x00000000; [0x08, BIT(21:16)] The lower 6 bits are used for front panel TS\_code input control.

Address offset: 0x0004C: Blocks for VME interrupt:

Bit 15-0 (R/W): 4-bit output to the front panel generic output connector; Reset default 0x0000; [0x2C, BIT(3:0)]

Bit 23-16 (R): Number of data blocks ready for VME interrupt. [0x2C, BIT(31:24)]

Bit 31-24 (R): on TI: Number of events of a partial block (or, before the block is formed)

On TS: bit(15:8) of the number of data blocks ready for VME interrupt.

Address offset: 0x00050: Sync delay setting (to compensate for the fiber length):

```

Bit 7-0 (R): on TI: SYNC phase of HFBR#1 input; [0x1C, BIT(7:0)]

Bit 15-8 (R/W): HFBR#1 SYNC input delay; Reset default 0x00; [0x1C, BIT(15:8)]

Bit 23-16 (R/W): TM (internal loopback) SYNC delay; Reset default 0x00; [0x1C, BIT(23:16)]

Bit 23-16 (R): on TI: SYNC phase of HFBR#5 input; [0x1C, BIT(23:16)]

Bit(31:24 (R/W): HFBR#5 SYNC input delay. Reset default 0x00; [0x1C, BIT(31:24)]

```

Address offset: 0x00074: Front Panel generic trigger input pre-scale: Reset default 0x00000000

```

Bit 3-0 (R/W): FP Generic trigger input #1;

Bit 7-4 (R/W): FP Generic trigger input #2;

Bit 11-8 (R/W): FP Generic trigger input #3;

Bit 15-12 (R/W): FP Generic trigger input #4;

Bit 19-16 (R/W): FP Generic trigger input #5;

Bit 23-20 (R/W): FP Generic trigger input #6;

```

Address offset: 0x00078: VME Sync Load[0x900, BIT(7:0)]

```

Bit 7-4 == Bit 3-0 (R/W): 4-bit sync code; Decoding of the Sync command (bit[7:0]):

```

0x11: VME clock DCM reset, and full reset;

0x22: CLK250 resync (AD9510, DCM resync and MGT reset);

0x33: AD9510 re-sync (slower clock phase adjustment), part of 0x22 function;

0x44: Reset the MGT status\_B registers;

0x55: Trigger link enable (serial link started), FIFO read counter reset;

0x77: Trigger link disable, trigger FIFO write counter reset;

0xAA: reset the TIslave trigger ready register;

0xBB: Reset the event number, and trigger input scalars (the 0xDD will not do);

0xDD: (SyncReset), FPGA logic and counter reset, this reset all goes to SD, CTP/GTP;

0x99: Force SyncReset high if this feature is enabled (by offset 0x24, bit 7);

0xCC: set the SyncReset low if it is forced high by code 0x99.

0x66, 0x88, 0xee: to be assigned;

0x00, 0xff: reserved, not to be assigned

Address offset: 0x0007C: VME Sync Delay. The latency before being serialized.

Bit 6-0 (R/W): latency, in 4ns steps. Reset default 000,0111 [0x904, BIT(6:0)]

Address offset: 0x00080: Reset pulse width: Reset default 00,0111

Bit 7-0 (R/W): Reset (to SW#A, SW#B and on-board) pulse width. Pulse width is (Bit(6:0)\*(4/32 ns)), Bit(7) determines the steps (4ns or 32ns); [0x904, BIT(13:8), bit(13) set to pulse to 1us wide]

➤ Address offset: 0x00084: VME Trigger/Command Register

Bit 11-0 (R/W): Trigger Command code transmitted in the trigger link; In the 12 bits, 0xABC, the 0xA determines the command type. For example:

Bit(11-0) = 0x123: (A=1) one trigger1 (readout trigger) pulse will be generated, and the event type = 0x23;

Bit(11-0) = 0x221: (A=2) one trigger2 pulse will be generated. The 0x21 is ignored;

Bit(11-0) = 0x812: (A=8) Set the block level (size), and the block level is set to 0x12.

➤ Address offset: 0x00088 (R/W): VME Random Trigger Command Register: [0x808, BIT(15:0)]

Bit 3-0: Random trigger\_1 rates:  $500KHz/(2^{Bit(3:0)})$ ;

Bit 6-4: same as Bit(2-0) for redundancy check. No match, no trigger\_1;

Bit 7: enable/disable random trigger\_1; (There is NO requirement that it match with bit 3)

Bit 11-8: Random trigger\_2 rates: 500KHz/(2<sup>Bit(11:8)</sup>);

Bit 14-12: same as Bit(10-8) for redundancy check. No match, no trigger\_2.

Bit 15: enable/disable random trigger\_2;

➤ Address offset: 0x0008C(R/W): VME Trigger Generation: [0x804, BIT(31:0)]

Bit 15-0: Number of trigger\_1s to be generated; If 0xFFFF, the number of event will not be limited.

Bit 31-16: (trigger rate control) Time between triggers.  $T = (120+30*Bit(30:16)*1024^{Bit(31)})$  ns. (Assuming that the ClkVme=33MHz or 30ns period).

Address offset: 0x00090(R/W): VME Trigger\_2 Generation: [0x80C, BIT(31:0)]

Bit 15-0: Number of trigger\_2s to be generated;

Bit 31-16: (trigger rate control) Time between triggers.  $T = (120+30*Bit(30:16)*1024^{Bit(31)})$  ns. (Assuming that the ClkVme=33MHz or 30ns period).

Address offset: 0x00094 (R): Number of Blocks in the DAQ system: [0x14, BIT(15:0)]

Bit 31-24: Number of events before a full data block;

Bit 23-0: Number of full data blocks the TI has ever generated;

Address offset: 0x00098 (R): SYNC history fifo, The fifo status is in register offset 0x24.

Bit 31-16: time stamp of the SYNC command, in steps of ~8us;

Bit(15): whether the time stamp has overflowed since previous SYNC code

Bit (14): Loopback sync valid;

Bit (13:10): Loopback sync code;

Bit (9): HFBR#5 sync valid;

Bit (8:5): HFBR#5 sync code;

Bit (4): HFBR#1 sync valid;

Bit (3:0): HFBR#1 sync code;

Address offset: 0x0009C (R/W): The FPGA running mode;

Bit 7-0: TS in running mode if set to 0x5A; if other value, not in running mode. Reset default 0x00; TI in running mode if set to 0x71. TI starts clock monitoring in 'running' mode.

Address offset: 0x000A0 (R): Fiber latency measurement result: [0x18]

Bit 31-23: latency data in 4ns steps

Bit 22-16: Delay in the IODelay, in 5000/64=78.125ps steps

Bit 15:0: Delay in the carry chain, two bits per slice, (or two mux per bit)

Address offset: 0x000A4 (R): Fiber latency measurement result from HFBR#5

Bit 31-23: latency data in 4ns steps

Bit 22-16: Delay in the IODelay, in 5000/64=78.125ps steps

Bit 15:0: Delay in the carry chain, two bits per slice, (or two mux per bit)

➤ Address offset: 0x000A8 (R): Trigger live timer: [0x20]

Bit 31-0 (r): board live time counter. The real time is Bit(31:0)\*256\*30ns.

Address offset: 0x000AC (R): Trigger busy (trigger dead) timer: [0x24]

Bit 31-0 (r): TID busy (cannot accept trigger, or trigger dead) time counter. The real time is Bit(31:0)\*256\*30ns. This counter and the live time counter make up the total time counter, which is the total time since any one of the trigger sources is enabled.

Address offset: 0x000B0 (R): MGT STATUS\_A: [0x30]

Bit 7-0: MGT[7:0] reset\_done;

Bit 11-8: MGT PLL lock detected (two MGTs per PLL lock);

Bit 15-12: fixed at 0x9

Bit 23-16: loopback trigger buffer length, this is the similar register as bit(9:0) of register offset 0xB8.

Bit 31-24: if '1', the HFBR#8, #7,...#1 is receiving idle word (K byte plus non-K byte);

Address offset: 0x000B4 (R): MGT STATUS\_B registers: [0x34]

Bit 7-0: Channel bonding sequence detected in MGT[7:0];

Bit 15-8: received data is not an 8B/10B character, or has disparity error in MGT[7:0];

Bit 23-16: RX disparity error has occurred in MGT[7:0];

Bit 31-24: Rx data not in 8B/10B table has occurred in MGT[7:0].

Address offset: 0x000B8 (R): MGT trigger data buffer length: [0x38]

Bit 9-0: Global trigger data buffer length (to be minimized to 0 for the longest fiber);

Bit 11-10: Data generation fifo full (in TRGDAQ module);

Bit 13-12: Data Readout fifo prog\_almost\_full (in VME module);

Bit 15:14: Data Readout fifo full; The order should be: DataReadoutFifoProgFull → DataGenFifoFull → DataReadoutFifoFull

```

Bit 25-16: Sub-system trigger data buffer length;

Bit 27: TI is in running mode if '1';

Bit 28: HFBR#1 MGT receiver error;

Bit 29: CLK250 DCM locked;

Bit 30: Clk125 DCM locked;

Bit 31: VME CLK (33MHz or 25MHz) DCM locked

Address offset: 0x000BC (R): TS input trigger counter: [0x3C]

Bit 31-0: Number of triggers received by TS (before BUSY inhibits).

Address offset: 0x000C0 (R): valid for TM (or with TS function), not valid for TI: [0x40]

Bit 7-0: Number of blocks to be readout on HFBR#1;

Bit 15-8: Number of blocks is still missing on HFBR#1

Bit 23-16: Number of blocks to be readout on HFBR#2

Bit 31-24: Number of blocks is still missing on HFBR#2

Address offset: 0x000C4 (R): valid for TM (or with TS function), not valid for TI: [0x44]

Bit 7-0: Number of blocks to be readout on HFBR#3;

Bit 15-8: Number of blocks is still missing on HFBR#3;

Bit 23-16: Number of blocks to be readout on HFBR#4;

Bit 31-24: Number of blocks is still missing on HFBR#4;

For TS, Bit 31-0: External Trigger counter, Number of triggers from External trigger before lookup table.

Address offset: 0x000C8 (R): valid for TM (or with TS function), not valid for TI: [0x48]

Bit 7-0: Number of blocks to be readout on HFBR#5;

Bit 15-8: Number of blocks is still missing on HFBR#5;

Bit 23-16: Number of blocks to be readout on HFBR#6;

Bit 31-24: Number of blocks is still missing on HFBR#6;

For TS, Bit 31-0: FrontPanel Trigger counter, Number of triggers from FP trigger before lookup table.

Address offset: 0x000CC (R): valid for TM (or with TS function), not valid for TI: [0x4C]

Bit 7-0: Number of blocks to be readout on HFBR#7;

Bit 15-8: Number of blocks is still missing on HFBR#7;

Bit 23-16: Number of blocks to be readout on HFBR#8;

Bit 31-24: Number of blocks is still missing on HFBR#8;

Address offset: 0x000D0 (R): valid for TM (or with TS function)

Bit 4-0: A24 address used for the module (to match with A23-A19); [0x54, BIT(4:0)]

Bit 9-5: A24 address set by the onboard hardware switch; [0x54, BIT(9:5)]

Bit 14-10: GA(4:0), VME64x geographic address; [0x54, BIT(14:10)]

Bit 15: parity of GA(4:0); [0x54, BIT15]

Bit 27-16: Number of blocks to be readout on TM itself; [0x50, BIT(23:16)]

Bit 31-28: Number of blocks is still missing on TM itself; [0x50, BIT(31:24)]

```

Address offset: 0x000D4 (R/W): Periodic Sync Event register

30

- Bit 15-0: Number of data blocks to assert a sync event (periodic SyncEvent);

- Bit 23-16: Sync event enable if set to 0x5A;

- Address offset: 0x000D8 (R): Event number register

- Bit 15-0: Number of data blocks to assert a sync event (periodic SyncEvent);

- Bit 31-16: higher 16-bit (bit 47-32) of event number counter;

- Address offset: 0x000DC (R): Event number register

- Bit 31-0: lower 32-bit (bit 31-0) of event number counter.

- Address offset: 0x000F0 (R): valid for TM (or with TS function)

- Bit 31-0: Number of valid code from Front Panel Async trigger inputs

- Address offset: 0x000FC (R/W): End\_of\_Run number of block setting

- Bit 31-0: number of block to End the run. If this is set to 0, there is no limit (disabled).

Bit 0: Enable the front panel (external input) signal to latch the trigger input scalars;

- Bit 1: Enable the front panel (same signal as controlled by bit0) to reset the trigger input scalars; These two bits are kind of related to the OneShotVme command, offset 0x100, bit 24 and bit25.

- Address offset: 0x00100 (W): Reset and one-shot registers. The signal will be one ClkVme cycle. If the ClkVme is 25 MHz, the one-shot will be 40ns wide. Positive logic. [0x100]

- Bit 0: not used;

- Bit 1: if '1', RESET signal to reset the VME to I2C engine;

- Bit 2: if '1', RESET signal to reset the VME to JTAG engine;

- Bit 3: if '1', RESET signal to reset the VME to SFM engine;

- Bit 4: if '1', RESET signal to reset the VME registers (TID settings) to their default values;

- Bit 6: if '1', reset the SYNC history fifo (clear the fifo);

- Bit 7: if '1', this register will generate a BUSY reset, and Trg Ack pulse (TS rev2 compatible).

- Bit 8: if '1', Reset the CLK250/Clk200 DCM.

- Bit 9: if '1', Reset the CLK125 DCM.

- Bit 10: if '1', Reset the MGT (MultiGigabit Transceiver,) inside the FPGA.

- Bit 11: if '1', Auto alignment of SYNC phase from HFBR#1; auto align P0 sync input for TD.

- Bit 12: if '1', TI: Auto alignment of SYNC phase from HFBR#5;

- TS: reset the BRAM loading address to 0 (very beginning).

- Bit 13: if '1', Auto alignment of fiber latency measurement signals;

- Bit 14: if '1', Reset the IODELAY;

- Bit 15: if '1', Measure the fiber latency

- Bit 16: if '1', this register will generate a 'TAKE TOKEN'

- Bit 17: if '1', the available number of data blocks will decrease by 1,

- Bit 20: if '1', generate a SyncEvent (forced SyncEvent). This can be used as end of run etc.

- Bit 23: if '1', generate Sync Reset Request.

- Bit 24: if '1', all the trigger input scalars are latched (ready for read out), the BusyTimer and LiveTimer are also latched;

- Bit 25: if '1', all the trigger input scalars are reset. (Bit 24 and Bit 25 can be set simultaneously). The event number is also reset by this.

Bit 31: if '1', the end\_of\_run command. If the readout block is not full, dummy trigger will be generated to fill the block.

Address offset: 0x00180 (R): FP input trigger scalar for #1:

Bit 31-0: 32-bit scalar, number of input#1 counter

Address offset: 0x00184 (R): FP input trigger scalar for #2:

Bit 31-0: 32-bit scalar, number of FP input#2 counter

Address offset: 0x00188 (R): FP input trigger scalar for #3:

Bit 31-0: 32-bit scalar, number of FP input#3 counter

Address offset: 0x0018C (R): FP input trigger scalar for #4:

Bit 31-0: 32-bit scalar, number of FP input#4 counter

Address offset: 0x00190 (R): FP input trigger scalar for #5:

Bit 31-0: 32-bit scalar, number of FP input#5 counter

Address offset: 0x00194 (R): FP input trigger scalar for #6:

Bit 31-0: 32-bit scalar, number of FP input#6 counter

Address offset: 0x001D0 (R): optic transceiver HFBR#1 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#1;

Bit 15-8: Crate ID of the TI connected to fiber#1.

Bit 23-16: Block level set on TI connected to fiber#1.

Address offset: 0x001D4 (R): optic transceiver HFBR#2 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#2;

Bit 15-8: Crate ID of the TI connected to fiber#2.

Bit 23-16: Block level set on TI connected to fiber#2.

➤ Address offset: 0x001D8 (R): optic transceiver HFBR#3 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#3;

Bit 15-8: Crate ID of the TI connected to fiber#3.

Bit 23-16: Block level set on TI connected to fiber#3.

Address offset: 0x001DC (R): optic transceiver HFBR#4 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#4;

Bit 15-8: Crate ID of the TI connected to fiber#4.

Bit 23-16: Block level set on TI connected to fiber#4.

Address offset: 0x001E0 (R): optic transceiver HFBR#5 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#5;

Bit 15-8: Crate ID of the TI connected to fiber#5.

Bit 23-16: Block level set on TI connected to fiber#5.

➤ Address offset: 0x001E4 (R): optic transceiver HFBR#6 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#6;

Bit 15-8: Crate ID of the TI connected to fiber#6.

Bit 23-16: Block level set on TI connected to fiber#6.

Address offset: 0x001E8 (R): optic transceiver HFBR#7 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#7;

Bit 15-8: Crate ID of the TI connected to fiber#7.

Bit 23-16: Block level set on TI connected to fiber#7.

Address offset: 0x001EC (R): optic transceiver HFBR#8 TI ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI connected to fiber#8;

Bit 15-8: Crate ID of the TI connected to fiber#8.

Bit 23-16: Block level set on TI connected to fiber#8.

Address offset: 0x001F0 (R): The TI master (itself) ID (in master mode)

Bit 7-0: Trigger Source Enable of the TI itself, should be the same as bit7-0 of register 0x20;

Bit 15-8: Crate ID of the TI itself, should be the same as bit7-0 of register 0x00.

Address offset: 0x008CX (0x8C0 - 0x8FC) (W): Trigger table loading: (prototype TS / TImaster) [0x8CX]

Bit 31-0: 32-bit wide table loading.

Address bits(5-2) are used to load 16 32-bit words;

6-bit read addressing with 8-bit trigger type (byte wide)

➤ Address offset: 0x02000~0x021FC (R): Mirror registers for VXS switch slot #B on TI board

Bit 31-0: 32-bit wide SD status (or data).

➤ Address offset: 0x02800~0x029FC (R): Mirror registers for VXS switch slot #A on TI board

Bit 31-0: 32-bit wide CTP/GTP status (or data).

## **6.3 VME to Serial engines:**

A24D32 are used for VME to serial engines. The engines include: VME to JTAG engine for the FPGA, VME to JTAG engine for the PROM, VME to I2C for the switch slot #A, VME to I2C engine for the switch slot #B, and VME to I2C engine for the P2 connector (could be used for anything). In the I2C engines design, only the lower one-byte or 2-byte of the 32-bit data word is used. The higher bytes are not used.

Address offset: 0x1XXXX: JTAG for PROM; Refer to the programming manual for VME to JTAG design for details.

Address offset: 0x2XXXX: JTAG for FPGA;

Address offset: 0x3XXXX: I2C for VXS switch slot #A; Refer to the programming manual for VME to I2C design for details.

Address offset: 0x4XXXX: I2C for VXS switch slot #B;

Address offset: 0x5XXXX: I2C for VME P2 connector (to be assigned);

Address offset: 0x6XXXX: Serial Flash memory interface.

Address offset: 0x0NXXX: SFM memory readout: (to be implemented)

0x07X0: IO Delay #X reset;

0x07X4: IO\_Delay #X delay increment (by 1);

0x07X8: IO\_Delay #X de-serialized data readout, idle='0xFFFF';

0x07Xc: IO\_Delay #X automatic delay increment by a number stored in SFM.

## **6.4 VME data acquisition:**

For data acquisition, the A32 block reads are used. The base address is set by the upper 9 bits of A24 register 0x00010, that is A[31:23] = RegData[31:23] of A24=0x00010.

# 7 Backplane pin out tables:

## 7.1 VXS P0 Pinout Table

| Payload slot#18, TI o | Payload slot#18, TI or TImaster |               |                    |  |  |  |

|-----------------------|---------------------------------|---------------|--------------------|--|--|--|

| Pin name              | Signal Description              | Signal Level  | Direction          |  |  |  |

| DP1 (A1+, B1-)        | CLOCK_C                         | LVPECL(DP)    | PP18 → SWA         |  |  |  |

| DP2 (D1+, E1-)        | CLOCK_D                         | LVPECL(DP)    | PP18 → SWA         |  |  |  |

| DP3 (B2+, C2-)        | Not Used                        |               |                    |  |  |  |

| DP4 (E2+, F2-)        | SYNC                            | LVPECL(DP)    | PP18 → SWA         |  |  |  |

| DP5 (A3+, B3-)        | TRIG1                           | LVPECL(DP)    | PP18 → SWA         |  |  |  |

| DP6 (D3+, E3-)        | TRIG2                           | LVPECL(DP)    | PP18 → SWA         |  |  |  |

| DP7 (B4+, C4-)        | TP_Data_LINK                    | LVDS(DP)      | PP18 ←→ SWA        |  |  |  |

| DP8 (E4+, F4-)        | BUSY                            | LVDS          | PP18 ← SWA         |  |  |  |

| SE1 (G1)              | SCL                             | I2C (+3.3V)   | PP18 → SWA         |  |  |  |

| SE2 (G3)              | SDA                             | I2C (+3.3V)   | PP18 ←→ SWA        |  |  |  |

| DP23 (B12+, C12-)     | CLOCK_A                         | LVPECL(DP)    | PP18 → SWB         |  |  |  |

| DP24 (E12+, F12-)     | CLOCK_B                         | LVPECL(DP)    | PP18 → SWB         |  |  |  |

| DP25 (A13+,B13-)      | TOKEN_OUT                       | LVDS(DP)      | PP18 → SWB         |  |  |  |

| DP26 (D13+, E13-)     | SYNC                            | LVPECL(DP)    | PP18 → SWB         |  |  |  |

| DP27 (B14+, C14-)     | TRIG1                           | LVPECL(DP)    | PP18 → SWB         |  |  |  |

| DP28 (E14+, F14-)     | TRIG2                           | LVPECL(DP)    | PP18 → SWB         |  |  |  |

| DP29 (A15+,B15-)      | SD/GTP_Data_Link                | LVDS, 250Mbps | PP18 <b>←→</b> SWB |  |  |  |

| DP30 (D15+,E15-)      | BUSY                            | LVDS          | PP18 ← SWB         |  |  |  |

| SE7 (G13)             | SCL                             | I2C(+3.3V)    | PP18 → SWB         |  |  |  |

| SE8 (G15)             | SDA                             | I2C(+3.3V)    | PP18 ←→ SWB        |  |  |  |

# 7.2 Other payload slots for subsystem TS:

| DP23 (B12+, C12-) | TRIG_LINK | LVPECL(DP) | PP ← SWB |

|-------------------|-----------|------------|----------|

| DP24 (E12+, F12-) | SYNC      | LVPECL(DP) | PP ← SWB |

| DP25 (A13+, B13-) | CLK250MHz | LVPECL(DP) | PP ← SWB |

| DP26              |           |            |          |

| DP27 |              |      |          |

|------|--------------|------|----------|

| DP28 |              |      |          |

| DP29 | SD_Data_link | LVDS | PP←→SWB  |

| DP30 | BUSY         | LVDS | PP → SWB |

| SE7  |              |      |          |

| SE8  |              |      |          |

## 7.3 VME P2 User-defined pin table

Similar to this, but Row-C is used. The two adjacent pins are used as a pair for differential signals.

| Pin name | Signal Name | Signal Level |

|----------|-------------|--------------|

| C01      | SCL         | I2C (LVCMOS) |

| C02      | SDA         | I2C (LVCMOS) |

| C05      | CLK250_P    | ECL          |

| C06      | CLK250_N    | ECL          |

| C09      | CLK_A_P     | ECL          |

| C10      | CLK_A_N     | ECL          |

| C13      | CLK_B_P     | ECL          |

| C14      | CLK_B_N     | ECL          |

| C17      | TRIG1_P     | ECL          |

| C18      | TRIG1_N     | ECL          |

| C21      | TRIG2_P     | ECL          |

| C22      | TRIG2_N     | ECL          |

| C25      | SYNC_P      | ECL          |

| C26      | SYNC_N      | ECL          |

| C29      | BUSY+       | ECL          |

| C30      | BUSY-       | ECL          |

# **8 TID Operation examples:**

The following is some operating procedures at VxWorks interactive mode. This is just a memo for the quick test of the TID board. They may change as the TID debug proceeds. First, one needs to login the VME controller. Here is the sequence:

Xming to PHECDA, linux server computer

From any xterm (or PUTTY), telnet to DAVW1 (neither username, nor password is needed). Only one telnet process is supported for the MVME6100 module). The address mapping for A24 is 0x90xxxxx. For DAVW8, which is a MVME5100 module, the address mapping for A24 is 0xFA000000. The M6100 has twice as much as M5100 in A32 memory. The M5100 is 0x08000000-0x0FFFFFFF; while the M6100 is 0x08000000-0x17FFFFFF.

The following commands are assuming that the TI is in slot#21 VME64x compatible crate (Geographic address available). 0xA8 = 10101xxx, that is the Geographic Address GA=21 or 10101.

## 8.1 A24 register echoing (write and read):

$\rightarrow$  \*(0x90A80008)=0x5566aa99; the same register should be read out

## 8.2 Readout the FPGA user\_ID:

The FPGA user code is readout through VME\_to\_JTAG engine. The FPGA user\_ID is firmware specific. If this code matches, it is TID and the right version of the firmware is loaded.

- → \*(0x90a80100)=0x04: VME to JTAG engine logic reset

- → \*(0x90aa003C)=0x0: Reset FPGA JTAG to 'reset idle' state

- → \*(0x90aa092C)=0x3C8: enable user\_ID readback

- → \*(0x90aa1F1C)=0x00: shift in 32-bit data, and the readback is user\_ID. The user\_ID should be 710xnmmm: n is the major version of the firmware, mmm is the revision of the firmware.

## 8.5 SW#A I2C operation:

The VME\_to\_I2C engine hides the serialization, and the two-bytes write (and/or read) can be finished by a single VME write (and/or read) command. For SW#A, the I2C chain is 011; for device 1101000, the I2C device at the FPGA is 000; assuming the byte address is 0xAD (10101101).

- → \*(0x90a80100)=0x01: VME\_to\_I2C engine reset

- → \*(0x90ab1EB4)=0xDADA: VME\_to\_I2C write

- → m 0x90ab1EB4, 4: VME to I2C read. ignore the higher two bytes

- $\rightarrow$  \*(0x90a80004)=0x100: Set the I2C address to 0b1101xxx

- → \*(0x90ab1eb4)=0xdata: VME to I2C write

# 9 TID Operation procedures (software setup):

The following is the operating procedures at VxWorks interactive mode. This is just a memo for the quick test of the TI board. The procedure will be optimized as the test goes along. This assumes that the hardware switch is set properly (as TI, TD, TS/TD/TI etc.)

## **9.1 Fiber latency measurement:**

- → \*(0x90a80100)=0x4000 //reset the digital IODELAY logic/clock

- $\rightarrow$  \*(0x90a80100)=0x2000 //phase alignment of the latency measurement signal

- $\rightarrow$  \*(0x90a80100)=0x8000 //Fiber latency measurement

- → M 0x90a800a0,4 //Fiber latency readout

- $\rightarrow$  \*(0x90a80100)=0x800 //Sync phase alignment relative to the 250MHz clock

- → \*(0x90a80050)=0xAAxxBBxx // load the Sync delay (AA for HFBR#5, BB for HFBR#1). The BB should be based on the previous measurement.

- → M 0x90a80050,4 //check the SYNC delay setting and phase alignment.

# 9.3 Trigger link startup:

- **→** \*(0x90a80078)=0x77

- → \*(0x90a80078)=0x77 //WriteStart, buffer\_write\_address reset and trigger data transmit disable

- → \*(0x90a8007c)=0x54 //Sync latency, delay before SYNC being serialized. This delay should cover the trigger word sterilizer/deserializer delay.

- $\rightarrow$  \*(0x90a80080)=0x7 //. The Reset pulse width is (7+1)\*4ns;

- → \*(0x90a80078)=0x55 //Start the trigger link, and this SYNC command will enable the trigger link buffer readout.

## 9.7 Trigger/DAQ monitoring:

- → M 0x90a80034, 4 //polling the register to see if there is data block to read

- → M 0x90a800a8, 4 //TID trigger live timer (live time)

- → M 0x90a800ac, 4 //TID trigger busy timer (dead time)

## 9.8 Data Readout:

- → M 0x80300100,4 //A32 readout; or

- → tidRead(slot, nwords) //readout nwords from TI; or

- → tidBERead(slot) // readout a block, and using Bus\_error to terminate the read; or

- → .....

### 10. Citations:

#### **Works Cited**

Chris. (2009). Gloabal Trigger Processor., (pp. 1-14). Chris. (2009). Hall\_D trigger layout., (pp. 20-25). Virginia. Collaboration, C. (2009). CLAS12 experiment. *Journal*, 1-25. Collaboration, G. (2009). GlueX experiment. *journal*, 1-20. Cuevas, C. (2008). Signal Distribution Module., (pp. 1-10). Ed. (2010). Trigger Supervisor Module., (pp. 1-19). experiments, C. (1990). CEBAF experiments. *journal*, 1-10. GU. (2010). Optical transceiver jitter measurement., (pp. 1-12). Raydo, B. (2008). Trigger Distribution board., (pp. 1-10). GU, (2010). VME to JTAG implementation GU, (2010). VME to I2C implementation

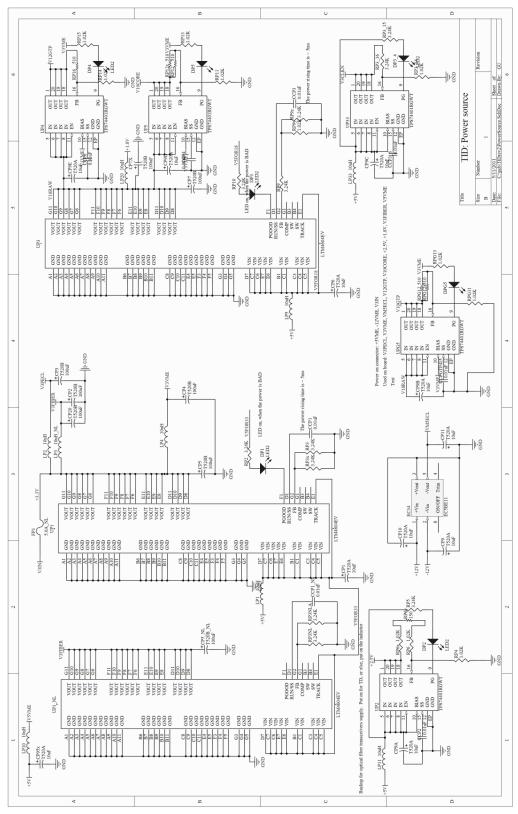

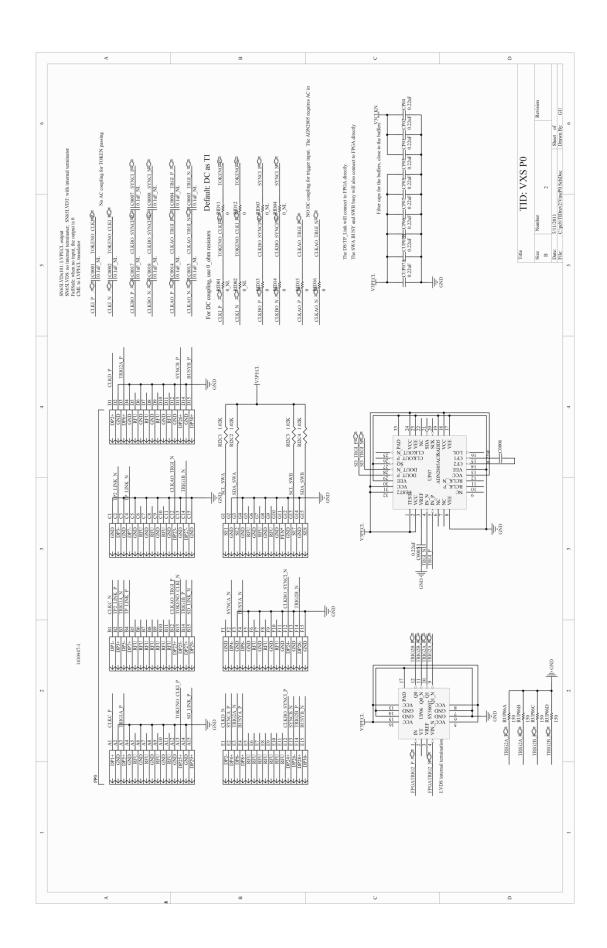

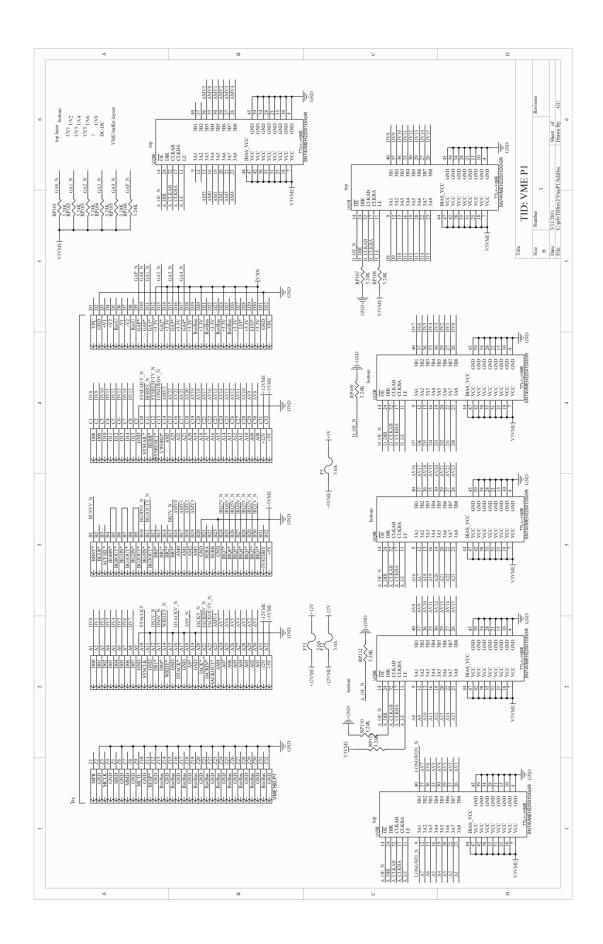

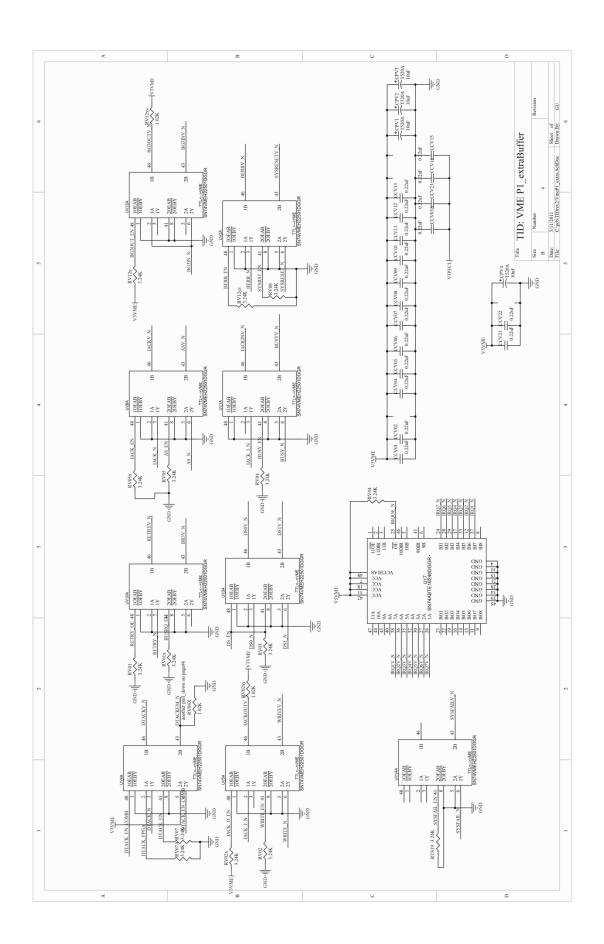

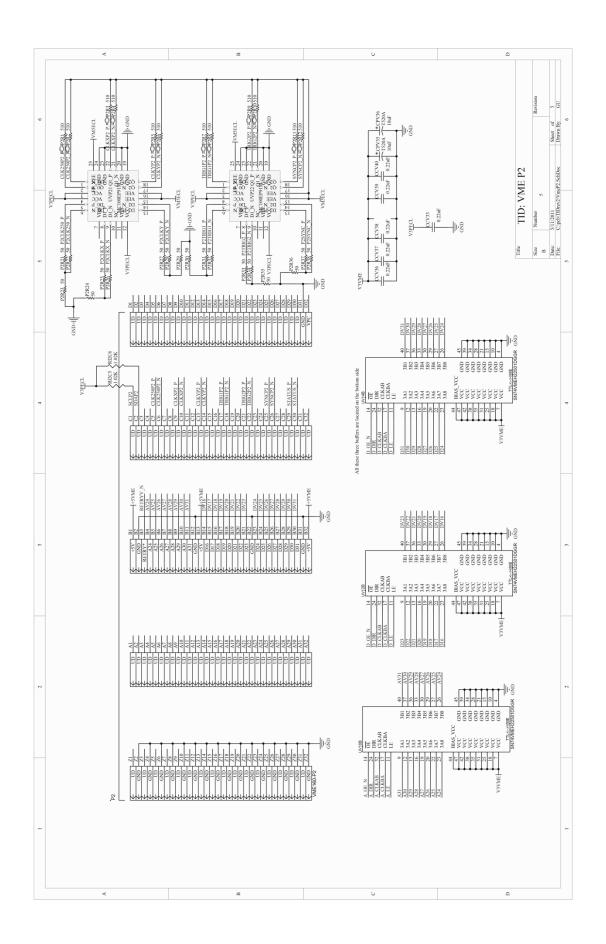

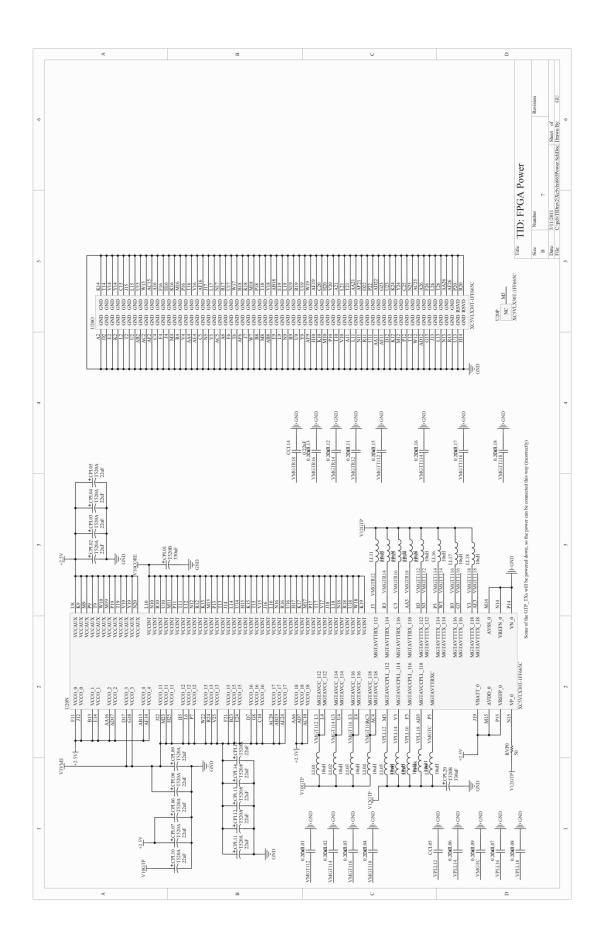

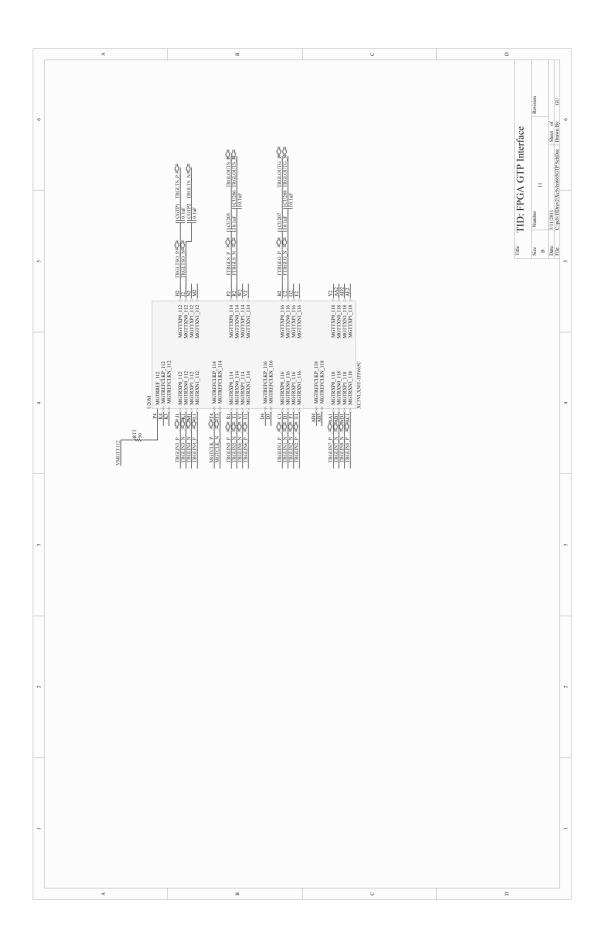

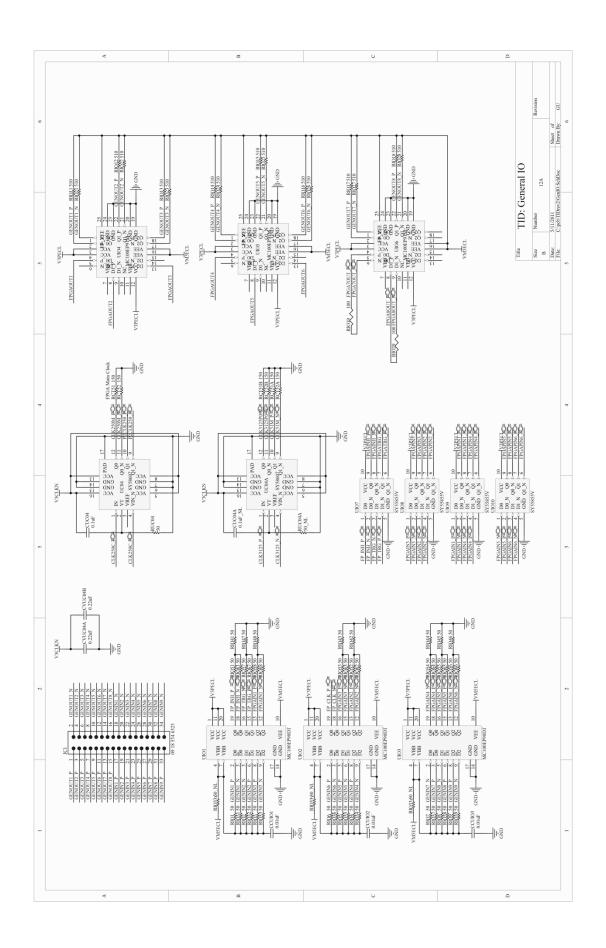

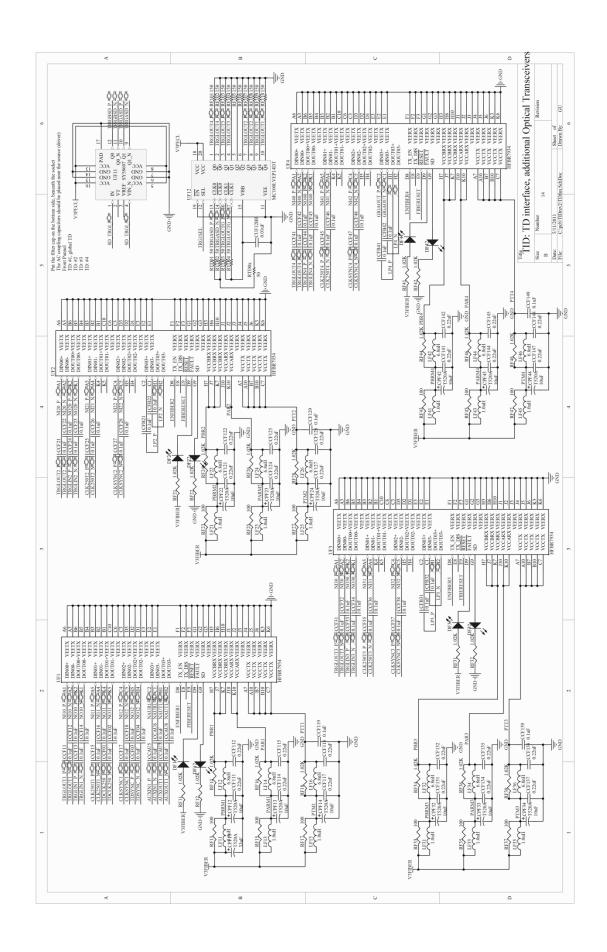

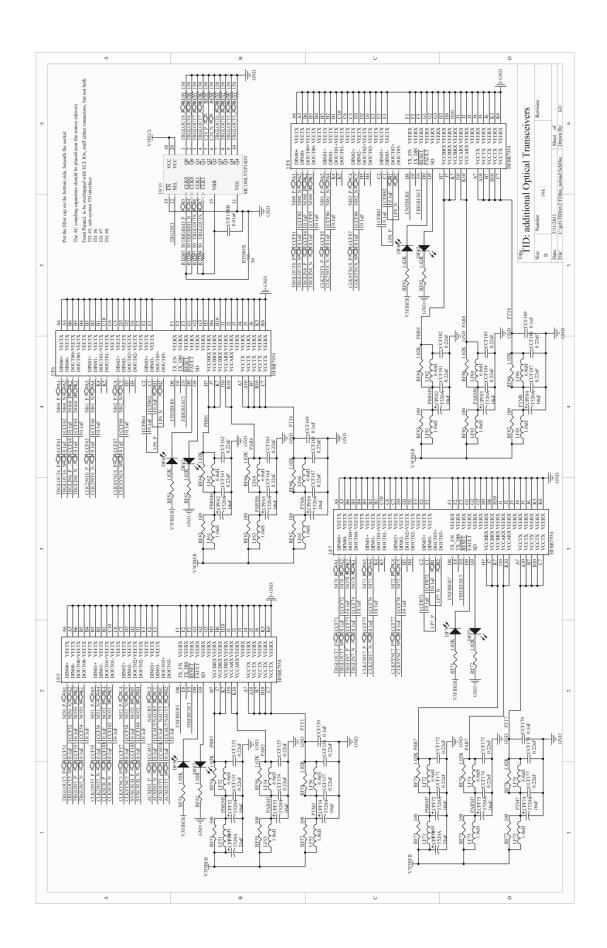

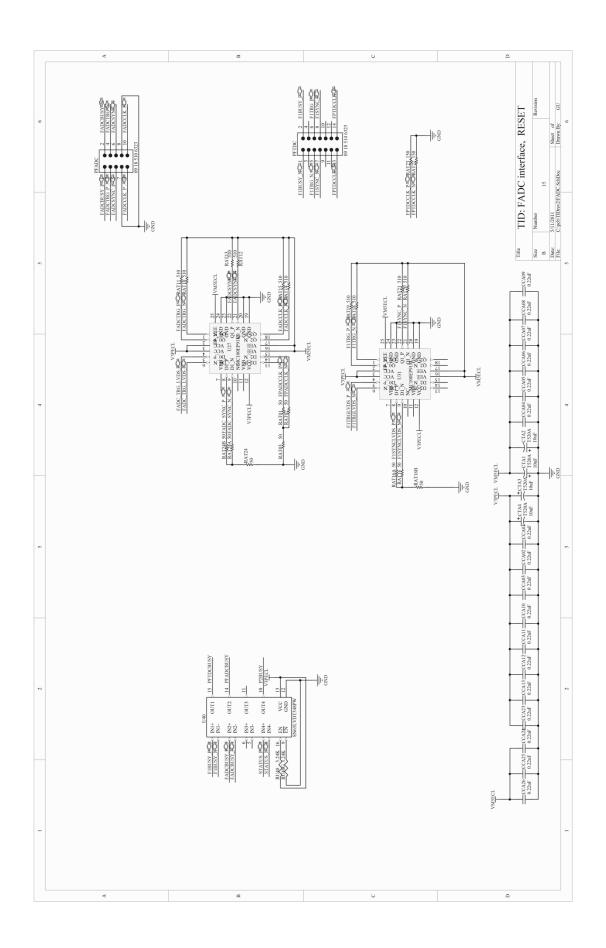

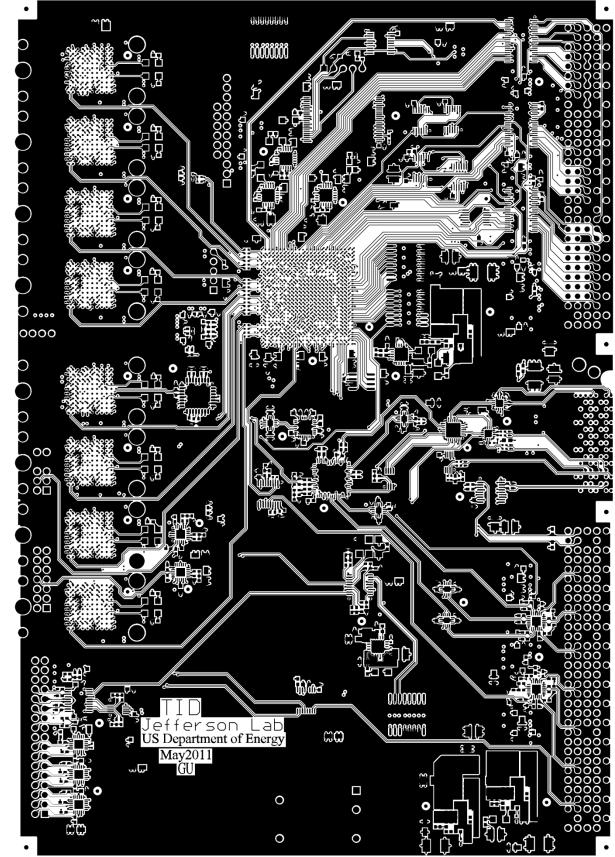

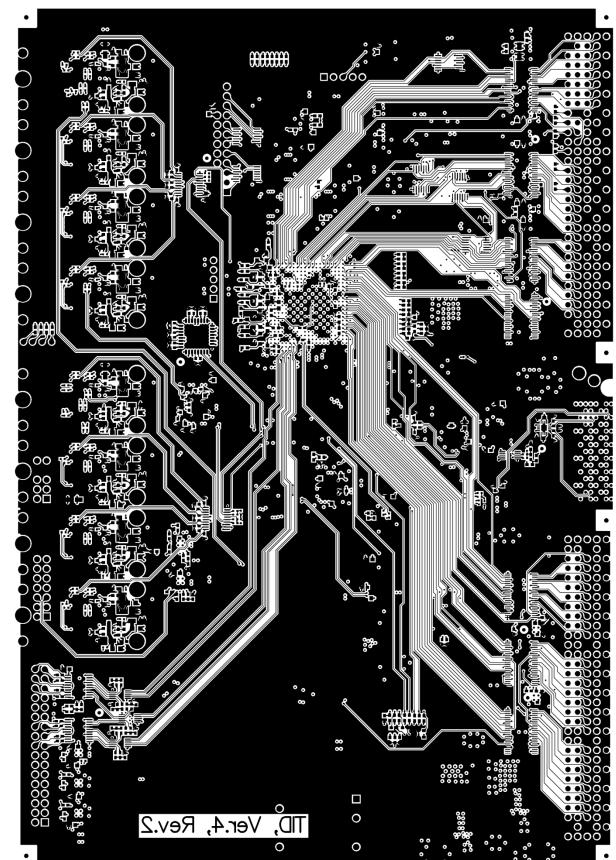

# Appendix A: TID Schematics:

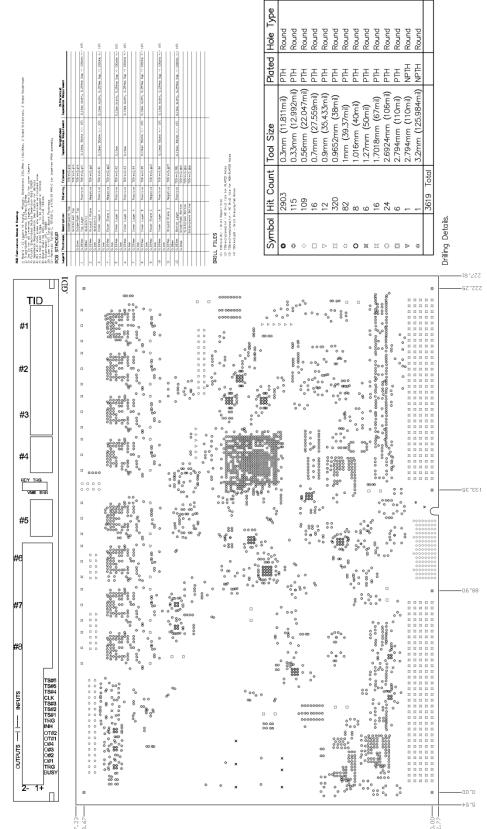

Appendix B: TID fabrication drawing:

# Appendix C: Bill of materials:

# Component list

**Source Data From:**

Project: Variant:

Report Date: 5/12/2011 Print Date: 12-May-11