# JLab 16 Channel Discriminator V2: Prototype Measurements 2009

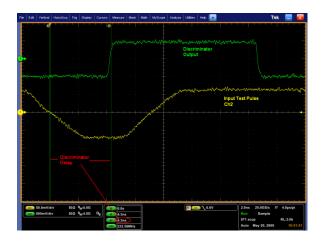

# Discriminator Delay (measured on channel 2): 4.3ns

#### Notes:

• Channels 1 & 2 have the longest delays due to front-panel connectors & layout

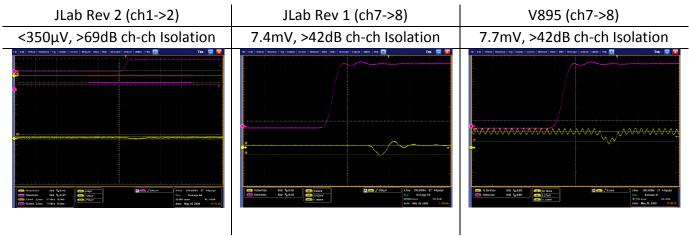

# Discriminator Channel Isolation (Test Pulse 1V/ns step):

### Notes:

- v895 (2 boards checked) have a ~1.8GHz ringing on all inputs (~5mV pk-pk)

- JLab Rev 2 Vertical Scale = 1mV/div, JLab Rev 1 & v895 Vertical Scale = 10mV/div

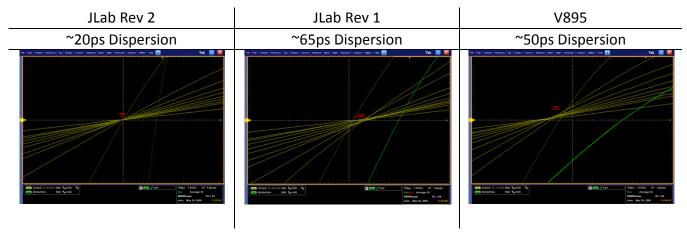

# **Discriminator Slew Rate Dispersion:**

# Notes:

• Input Signal: 356mV, 30ns width negative pulse

Discriminator Overdrive: 100mVEdge Speed: 250mV/ns – 20mV/ns

• Pulse Rate: 100Hz

# **Discriminator Overdrive Dispersion:**

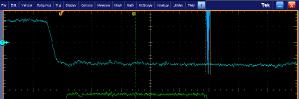

# **Discriminator Maximum Rate (non-updating mode):**

110MHz Rate w/4ns Output Pulse Width

SUBJIC Discriminate logal

80MHz Rate w/8ns Output Pulse Width

### Notes:

• Pusler Dead-time: ~4.5ns, constrained by maximum pulse width

# **Discriminator Output Pulse Width:**

Maximum Output Width = 50ns

Trailing Edge Jitter = 51ps RMS, 340ps pk-pk

#### Notes:

- Trailing edge jitter will likely be improved in next revision by switching to ground referenced driver for pulser output section.

- Maximum pulse width of 50ns put pulser dead-time ~4.5ns

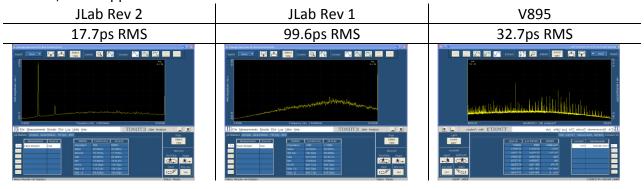

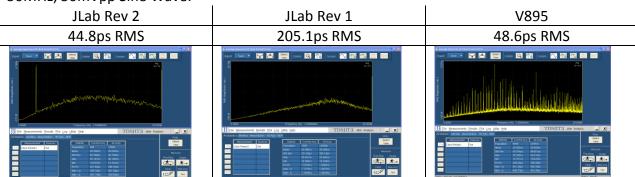

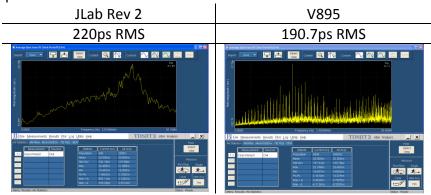

#### **Discriminator Jitter:**

# 50MHz, 100mVpp Sine Wave:

# 50MHz, 50mVpp Sine Wave:

# 50MHz, 10mVpp Sine Wave:

### **Minimum Threshold:**